在項目上使用uvm代碼自動生成可以提高驗證環境搭建的效率,你可以:

使用uvm代碼生成器創建基本的uvm驗證環境框架,然后丟棄代碼生成器模板并擴展和維護生成出來的代碼。盡管uvm代碼生成器僅在項目的初始階段使用,然后被丟棄,但仍然提高了驗證的效率。

團隊所有成員的驗證環境結構獲得了統一,方便了集成和檢視。

根據項目的特定需求,個性化地定制自己的uvm代碼生成器模板和腳本。

示例

要運行uvm代碼生成器,至少需要三個template 文件:

clkndata.tpl Interface templatefile common.tpl Commontemplatefile pinlist Pinlistfile

定義 DUT的文件

mydut/mydut.sv SystemVerilog sourcefilefor the DUT

兩個腳本,一個用于運行uvm代碼生成器,另一個用于運行仿真(為了避免記住命令行及其參數)。

gen Scripttorunthecodegenerator run Scripttorunthe simulator

下面是這個示例中使用的 DUT 文件:

mydut/mydut.sv

module mydut (input clk, input byte data);

always @(posedge clk)

$display("mydut data = %h", data);

endmodule

Interface template file

我們需要的第一個模板文件是The first template file。此文件表征一個 DUT的接口,指定一些變量名稱,諸如UVM transaction中的變量和 SystemVerilog 接口中的變量。

clkndata.tpl

agent_name= clkndata trans_item =data_tx trans_var = rand byte data; if_port= logic clk; if_port= byte data; if_clock= clk

其中變量的含義,見名知意。

agent_nameclkndata將用作生成的許多文件名前綴,例如clkndata_agent、clkndata_if、clkndata_pkg 和 clkndata_config。

實際上,每個 DUT 接口都有一個這樣的template file,每個template file都包含唯一的agent名稱。

trans_itemdata_tx將用作類名,該類擴展uvm_sequence_item以定義生成的agent中使用事務transaction,即從sequener發送到driver和通過monitor的analysis port發送的transaction。

trans_var “=”后面的rand byta data將包含在生成的transaction類中。注意行尾的“;”:這很重要,因為它將被復制到生成的代碼中。另外,如果希望變量隨機化,請記住包含 rand 關鍵字。通常會有多個trans_var行。

if_port“=”后面的logic clk;和if_port= bytedata;將包含在生成的 SystemVerilog interface中。同樣,請注意行尾的“;”。即使是最簡單的例子,我們也需要一個時鐘和一個數據信號。最后,if_clock挑選出其中一個interface變量作為時鐘信號。作為if_clock指定的名稱必須是同一template文件中if_ports之一。

Common template file

我們需要的第二個 template file是Common template file,必須命名為 common.tpl。uvm代碼生成器始終需要一個common.tpl 文件,該文件指定了一些常用設置。只有一個設置是強制的,即dut_top,有大量可選設置可讓你對生成的代碼進行控制。許多設置具有合理的默認值,因此你可以在開始時忽略這些設置。

common.tpl

dut_top= mydut

dut_top指定DUT top module的名稱,在本例中為 mydut。DUT 源文件必須放置在名為 ./dut 的目錄中,或者你可以使用common.tpl文件設置dut_source_path選擇其他目錄名稱,也可以在名為 files.f 的單個文件中手動列出文件的位置。

Filename pinlist

第三個template文件是Pinlist file,它指定 DUT 的端口(在 DUT 的 SystemVerilog 代碼中指定)和 DUT 接口的變量(在Interface template file

中指定)之間的連接。

Pinlist file

!clkndata_if clkclk data data

Pinlist file分為多個部分,每個 DUT 接口一個部分,每個部分以感嘆號 “!” 開頭,后跟接口名稱,該名稱始終是agent名稱加上后綴_if。在這個示例中,只有一個agent clkndata,因此相應的接口名稱為 clkndata_if。其余的每一行都包含 DUT top module的端口名稱,后跟相應 DUT 接口中的變量名稱。

也可以使用Pinlist file連接不屬于任何特定interface的 DUT 端口,例如:

! clock_port global_clock_var reset_port global_reset_var

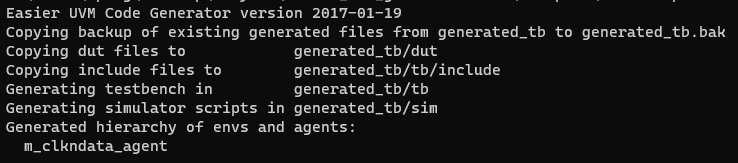

運行uvm代碼生成器

在提供了三個template文件(clkndata.tpl,common.tpl,pinlist)和DUT文件(mydut.sv)之后,我們現在可以為這個示例運行uvm代碼生成器。我們將命令行放在單行腳本文件中:

perl ../easier_uvm_gen.pl clkndata.tpl

Common template file的名稱默認為 common.tpl(但可以使用 -m 開關從命令行進行設置。現在我們可以運行uvm代碼生成器:

生成的結構如下所示。弄清楚代碼生成器到底是做什么的最好方法是自己運行它!

top_tb (module)

? top_th (module instance)

? clkndata_if (interface instance)

mydut (module instance)

top_config (class uvm_object)

? top_test (object, class uvm_test)

? top_env (uvm_env)

? clkndata_config (uvm_object)

clkndata_agent (uvm_agent)

? clkndata_sequencer

clkndata_driver (uvm_driver)

clkndata_monitor (uvm_monitor)

clkndata_coverage (uvm_subscriber)

? top_default_seq (created in run_phase, class uvm_sequence)

? clkndata_default_seq (uvm_sequence)

? data_tx (uvm_sequence_item)

?

審核編輯:湯梓紅

-

UVM

+關注

關注

0文章

182瀏覽量

19171 -

代碼

+關注

關注

30文章

4788瀏覽量

68603 -

生成器

+關注

關注

7文章

315瀏覽量

21010 -

代碼生成器

+關注

關注

0文章

25瀏覽量

9120 -

環境搭建

+關注

關注

0文章

53瀏覽量

9055

原文標題:Easier UVM Code Generator Part 1: 入門

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于STRAIGHT算法的個性化語音生成方法

STM32庫函數代碼自動生成器V1.2

基于UVM的代碼生成器的開發設計

個性化地定制自己的uvm代碼生成器模板和腳本

個性化地定制自己的uvm代碼生成器模板和腳本

評論