摘要

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

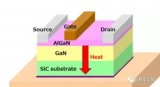

高阻斷電壓、大功率密度、高轉化效率是電力電子器件技術持續追求的目標,基于 4H-SiC 優異的材 料特性,在電力電子器件應用方面具有廣闊的發展前景。圍繞 SiC MOSFET 器件對外延材料的需求,介紹了 國內外主流的 SiC 外延設備及國產 SiC 襯底的發展,并重點介紹了寬禁帶半導體電力電子器件國家重點實驗 室在國產 150 mm(6 英寸)SiC 襯底上的高速外延技術進展。通過關鍵技術攻關,實現了 150 mm SiC 外延材料 表面缺陷密度≤0.5 cm-2,BPD 缺陷密度≤0.1 cm-2,片內摻雜濃度不均勻性≤5%,片內厚度不均勻性≤1%。基于自主外延材料,實現了 650~1 200 V SiC MOSFET 產品商業化以及 6.5~15 kV 高壓 SiC MOSFET 器件的 產品定型。

引言

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

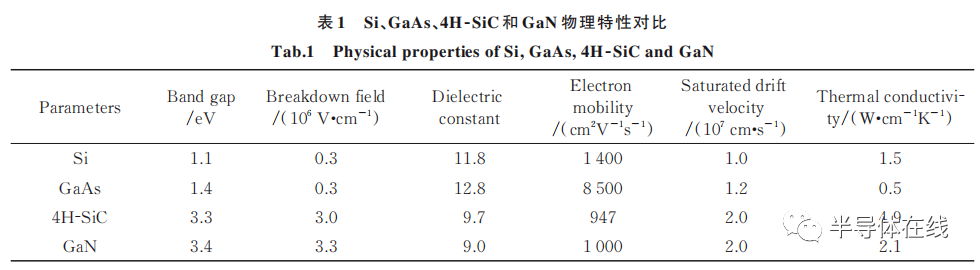

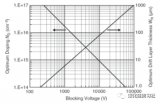

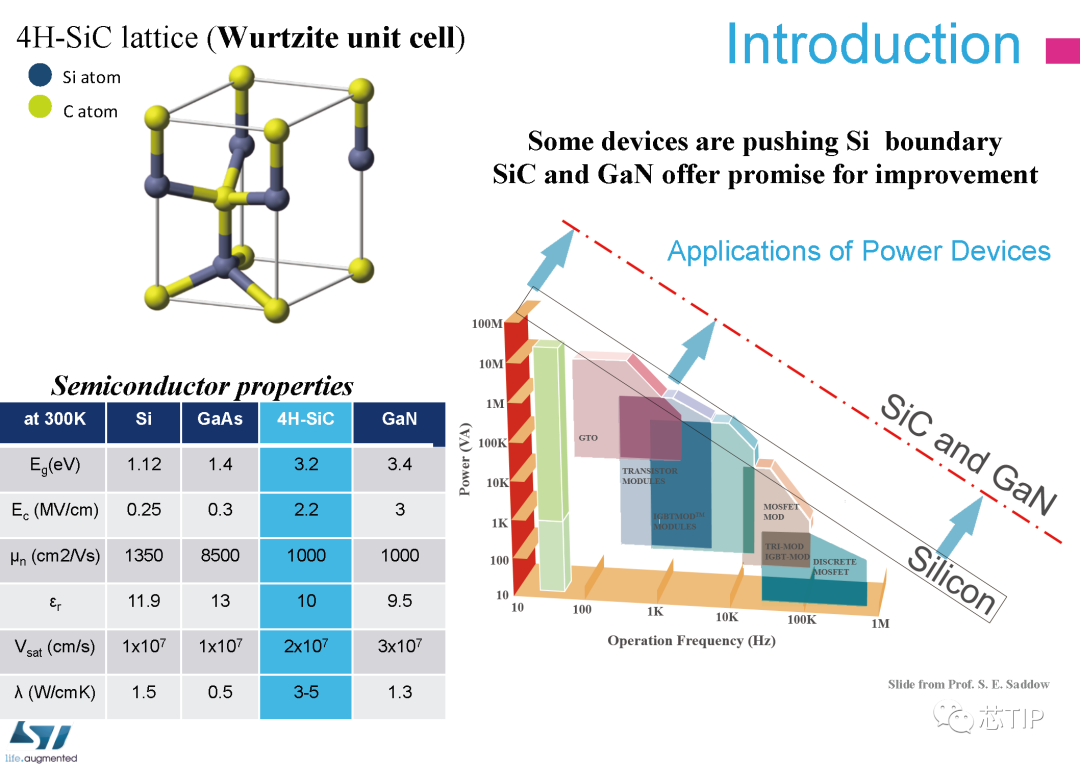

電力電子技術是能源與電能變換領域的核心 技術,能源的高效率轉化是實現節能、環保、低碳經 濟的關鍵,高壓大容量電力電子器件是關鍵元件和 基礎。長期以來,硅(Si)器件幾乎統治了所有電力 電子系統的應用。這主要得益于材料和芯片制備 方面成熟的工藝技術優勢。但是,Si 器件的性能已 經接近由其材料特性所決定的理論極限,性能的進 步提升十分受限。材料是芯片、器件性能實現的基 礎,若要進一步提高電力電子裝置與系統性能,需 訴諸于更優越的半導體材料。表 1 為典型半導體材料特性對比。

4H-SiC 作為第三代寬禁帶半導體材料,與傳統 的 Si 和 GaAs 材料相比,在熱導率、臨界擊穿場強、 工作溫度、飽和電子漂移速度等方面具有非常優異 的材料特性。其中,4H-SiC 的禁帶寬度接近 Si 的 3 倍,且本征載流子濃度遠低于 Si,使得 SiC 器件可以 工作在更高的溫度;4H-SiC 的擊穿場強比 Si高一個 數量級,相同器件耐壓下的 SiC 器件可以設計較小 厚度和更高摻雜濃度的外延材料,大幅度降低器件 的導通電阻;4H-SiC 的熱導率是 Si 的 3 倍以上,SiC 器件可以長時間在溫度更高的環境下穩定地工作;4H-SiC 的飽和電子漂移速率是 Si 的 2 倍,使 SiC 器 件具備更高的工作頻率。加入三代半交流群,加VX:tuoke08。SiC 具備獨特的穩定性、 適用性和突出的性能,切合節能減排、智能制造、信 息安全等國家重大戰略需求,被視為支撐新一代新 能源汽車、高速軌道列車、高壓電網、光伏等產業創 新發展和轉型升級的重點核心材料之一,已成為全 球半導體技術和產業競爭焦點。

幾乎所有的 SiC 器件均在外延材料上實現,高 質量的 4H-SiC 同質外延材料是 SiC 器件研制的基 礎,外延材料的性能直接決定了 SiC 器件性能的實 現。大電流、高可靠性 SiC 器件對外延材料的表面 形貌、缺陷密度以及摻雜和厚度均勻性等方面提出 了更苛刻的要求。大尺寸、低缺陷密度和高均勻性 的 SiC 外延材料已成為 SiC 電力電子產業發展的關 鍵。美國 SiC 行業巨頭 Wolfspeed 公司已經推出了 150 mm(6 英 寸)和 200 mm(8 英 寸)的 多 層 結 構 4H-SiC 外延片,外延層厚度達到了 200 μm,無缺 陷面積≥95%,且仍在不斷進行工藝優化。日本的 Renosac(原昭和電工)6 英寸 30 μm 以內 4H-SiC 外 延片的缺陷密度達到了≤0.5 cm-2,基平面位錯密 度≤0.1 cm-2,2022 年 9 月開始批量出貨 8 英寸 SiC 外延片。國內商業化的 SiC 外延公司瀚天天成、 廣東天域半導體、普興電子和中電化合物等目前已 實現 100~150 mm 4H-SiC 外延片批量生產,無缺陷面積達到 95% 以上,外延層厚度≤100 μm。另 外 ,廈 門 大 學 于 2023 年 3 月 成 功 實 現 了 200 mm 4H-SiC 外延生長,制備的 12 μm 厚外延片片內外延 厚 度 不 均 勻 性 2.3%,片 內 摻 雜 濃 度 不 均 勻 性 < 7.5%,表面缺陷密度≤0.5 cm-2?,在國內首次公開報 道了 200 mm 4H-SiC 外延技術?。?

1 國內外主流外延設備概況

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

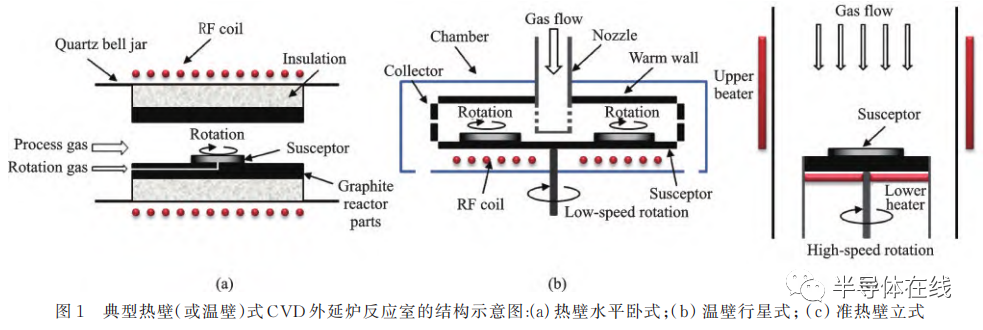

外延是指在單晶襯底上沿原來的晶軸方向生 長 出 新 單 晶 層 的 過 程 ,新 生 長 的 單 晶 層 即 外 延 層。現階段,化學氣相沉積(Chemical vapor deposition,CVD)是最為普及的 4H-SiC 同質外延方法, 已經廣泛應用于工業化生產。4H-SiC CVD 外 延一般采用熱壁或溫壁式 CVD 設備,在較高的生長 溫度條件(1 500~1 700℃)下保證了外延層 4H 晶型 SiC 的延續。熱壁或溫壁式 CVD 經過多年的發展, 按照進氣氣流方向與襯底表面的關系,反應室可以 分 為 水 平 臥 式 結 構 反 應 爐 和 垂 直 立 式 結 構 反 應 爐。熱壁水平臥式 CVD、溫壁行星式 CVD 以及 準熱壁立式 CVD 是現階段主流外延設備技術方案, 已實現商業化應用,其主要結構示意圖如圖 1所示。

熱壁水平式 CVD 系統,一般為氣浮驅動旋轉的 單片大尺寸生長系統,易實現較好的片內指標,代 表性機型為意大利 LPE 公司的 Pe1O6,該機臺可以 實現 900℃高溫自動裝取片,主要特點是生長速率 高、外延周期短、片內及爐次間一致性好等,在國內 市場占有率最高。根據 LPE 官方報道,結合主要用 戶的使用情況,Pe1O6 外延爐生產的厚度 30 μm 以 下 100~150 mm(4~6 英寸)4H-SiC 外延片產品可 以 穩 定 達 到 如 下 指 標 :片 內 外 延 厚 度 不 均 勻 性 ≤2%,片內摻雜濃度不均勻性≤5%,表面缺陷密 度 ≤1 cm-2,表 面 無 缺 陷 面 積(2 mm×2 mm 單 元 格)≥90%。基于該設備生長的 SiC 外延材料, 最大外延厚度已達 200 μm 以上。國內晶盛機電、 中國電科 48 所、北方華創、納設智能均開發了具有 類似功能的單片式 SiC 外延設備。2023 年 2 月,晶 盛機電發布了 6 英寸雙片式 SiC 外延設備,該設備 通過對反應室石墨件的改造,采用上下層疊加的 方式,單爐可以生長兩片外延片,且上下層工藝氣 體可以單獨調控,溫差≤5℃,有效彌補了單片水平 式外延爐產能不足的劣勢。

溫壁行星式 CVD 系統,以行星排布基座的方 式,特點是單爐多片生長,產出效率較高。代表性 機 型 為 德 國 Aixtron 公 司 的 AIX G5 WW C(8× 150 mm)和 G10-SiC(9×150 mm 或 6×200 mm)系 列外延設備。據 Aixtron 官方報道,G10 外延爐生產 的厚度 10 μm 的 6 英寸 4H-SiC 外延片產品可以穩 定達到如下指標:片間外延厚度偏差±2.5%,片內 外 延 厚 度 不 均 勻 性 ≤2%,片 間 摻 雜 濃 度 偏 差 ±5%,片 內 摻 雜 濃 度 不 均 勻 性 ≤2%。截 至 目 前,此類機型在國內用戶端使用較少,批量生產數 據不足,在一定程度上制約了其工程化應用。由于 多片式外延爐在溫場和流場控制等方面技術壁壘 較高,國內同類設備開發仍處于研發階段,尚無替代機型。

準熱壁立式 CVD 系統,主要通過外部機械輔助 基座高速旋轉,特點是通過較低的反應室壓力有效 降低粘滯層厚度從而提高了外延生長速率,同時其 反應室沒有能夠沉積 SiC 顆粒的上壁,不易產生掉 落物,在缺陷控制上擁有先天優勢,代表性機型為 日 本 Nuflare 公 司 的 單 片 式 外 延 爐 EPIREVO S6。據 Nuflare 報道,EPIREVO S6 設備的生長速率可以 達到 50 μm/h 以上,且外延片表面缺陷密度可控制 在 0.1 cm-2以下。在均勻性控制方面,2019 年 Nuflare 工程師 Yoshiaki Daigo 報道了采用 EPIREVO S6 生長的 10 μm 厚 6 英寸外延片的片內均勻性結 果,片內厚度和摻雜濃度不均勻性分別達到 1% 和 2.6%。目前,芯三代、晶盛機電等國內設備制造 商已經設計并推出了具有類似功能的外延設備,但還沒有大規模的使用。

2 國內外單晶襯底進展

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

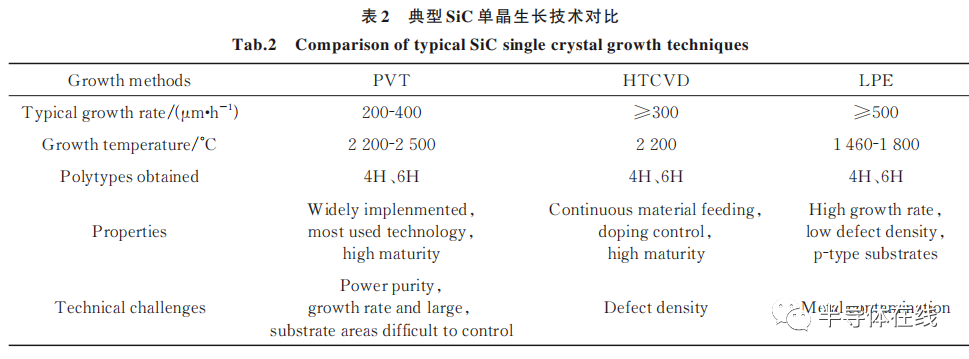

4H-SiC 晶體生長的技術主要有物理氣相輸運 法(PVT) 、高 溫 化 合 氣 相 沉 積 法(HTCVD)以及液相法(LPE)。表 2 從晶體尺 寸、生長速率、晶體缺陷與摻雜控制等單晶生長的 關鍵控制因素角度對比了典型的幾種 SiC單晶生長技術的優點和缺點。現 階 段 ,PVT 法 仍 是 4H-SiC 單晶生長技術中成熟度最高和商業化最廣 的方法。

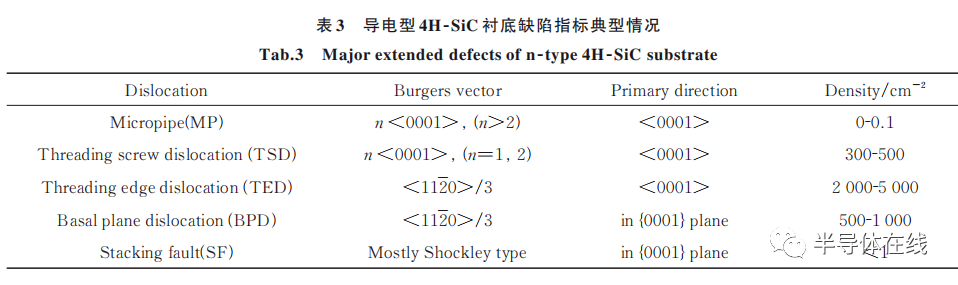

1987 年 , Cree 公 司(現 Wolfspeed)在 美 國 國 防 部 在 資 助 下 ,建 立 了 首 條 SiC 襯 底 生 產 線 ,于 1994 年 推 出 了 商 品 化 的 4H-SiC 單 晶 襯 底 。在 此 以后,隨著 SiC單晶產品市場需求的增長,4H-SiC 單 晶 襯 底 的 技 術 發 展 也 進 入 了 高 速 期 。近 10 年 來,4H-SiC 襯底在晶片尺寸和缺陷指標等方面均 取得了極大的發展,如表 3 所示,隨著商品化程 度 不 斷 提 高 ,國 內 外 已 經 有 多 家 SiC 襯 底 生 產 公 司 推 出 具 有 不 同 導 電 類 型 的 大 尺 寸 4H-SiC 襯底。

以電力電子器件用 n 型 4H-SiC 襯底為例,美國 Wolfspeed 和 Coherent、日 本 Rohm(Sicrystal)以 及 韓國 SK Siltron 等公司均已實現 150 mm 4H-SiC 襯 底的批量供應。在 200 mm 4H-SiC 襯底方面:Wolfspeed 公司計劃 2024 年將 4H-SiC 襯底生產能力提 高 10 倍,且主要生產 200 mm SiC 襯底;Coherent 公 司 計 劃 5 年 內 將 包 括 200 mm SiC 襯 底 在 內 的 4H-SiC 襯底生產能力提高 5~10 倍;SK Siltron 公司 和 Sicrystal 公司分別計劃于 2023 年和 2024 年啟動 200 mm SiC 襯底量產。

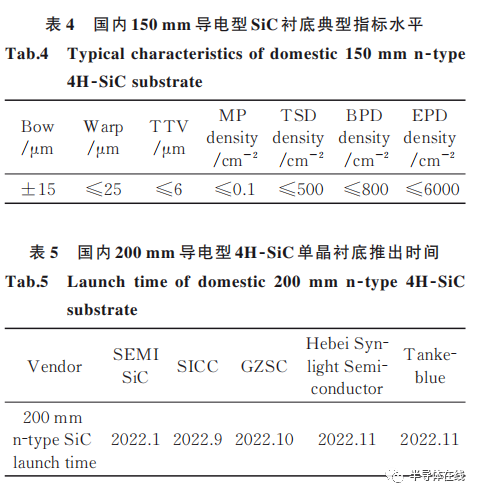

國 內 SiC 單 晶 襯 底 研 發 起 步 較 晚 ,但 近 年 來 發展十分迅速,以爍科晶體(SEMISiC)、天岳先進 (SICC)、南砂晶圓(GZSC)、同光股份(Hebei Syn-light Semiconductor)、天 科 合 達(Tankeblue)等 為 代表的襯底供應商已經實現 150 mm 單晶襯底的 穩定生產,典型指標水平如表 4 所示。同時,2022 年 國 內 襯 底 制 造 商 也 相 繼 推 出 了 200 mm SiC 襯 底 樣 品 ,如 表 5 所 示 ,預 估 2023 年 將 實 現 小 規 模 量產。

3 基于國產單晶襯底高速外延進展

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

依托中國電子 科 技 集 團 公 司 第 五 十 五 研 究 所 建 立 的 寬 禁 帶 半 導 體 電 力 電 子 器 件 國 家 重 點 實 驗 室 根 據 電 力 電 子 器 件 發 展 的 需 求 ,在 2018 年 啟 動 了 基 于 國 產 150 mm 4H-SiC 單 晶 襯 底 的 外 延 生 長 技 術 開 發 。截 止 目 前 ,基 于 LPE Pe1O6 外 延 機 臺 ,已 突 破 大 尺 寸 外 延 幾 何 參 數 控 制 、外 延 缺 陷 控 制 、片 內 均 勻 性 提 升 等 關 鍵 技 術 ,實 現 了 基 于 國 產 單 晶 襯 底 的 150 mm SiC 外 延 材 料 工 程 化 應 用 。

3.1 幾何參數控制

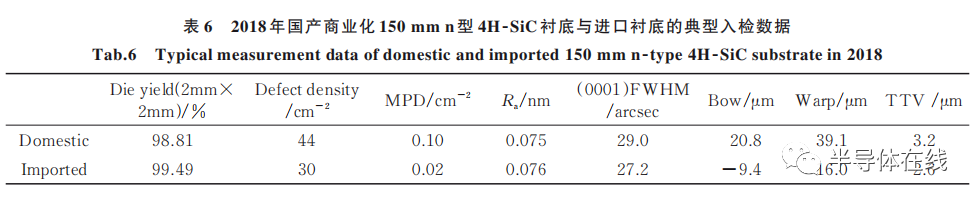

2018年國產商業化 150 mm n型 SiC 襯底與同類 進口襯底的入檢數據如表 6 所示。國產襯底(0001) 半高寬(Full width at half maximum, FWHM)和表 面粗糙度(Ra )方面等指標方面與進口襯底水平相 當,但在幾何(面型)參數方面存在明顯差距,國產 150 mm 導電 SiC 襯底 Bow 和 Warp 值較大且外延后 數值增大更為明顯、大多數超出 50 μm。

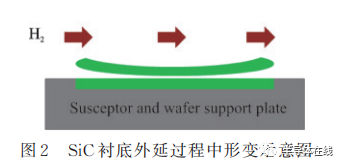

外延生長過程中,SiC 襯底背面直接與石墨基 座接觸,被熱傳導加熱。襯底正面有大量的氫氣 流過,散熱較快,襯底正反面存在溫度差異,因此 高溫狀態下襯底趨向于碗狀(正 Bow 值)分布,如 圖 2 所示。因而,在國產襯底 Bow 和 Warp 值較大 的 時 候 ,工 藝 過 程 中 傾 向 于 采 用 負 Bow 值 的 SiC 襯 底 。此 外 ,在 外 延 生 長 之 前 對 背 面(C 面)進 行 拋光可極大地消除外延層(Si 面)的殘余應力, 進而減小外延片形變。

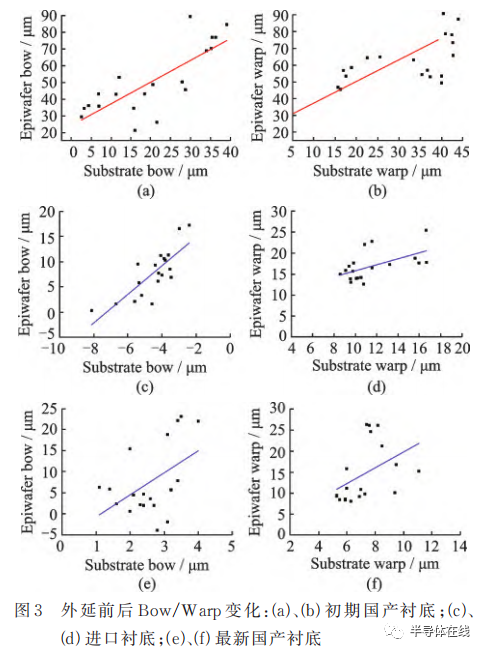

通 過 外 延 材 料 特 性 與 襯 底 參 數 之 間 的 關 聯 性研究,明確了襯底晶體及加工質量是導致外延 前 后 幾 何 參 數 指 標 退 化 的 關 鍵 因 素 。通 過 對 單 晶襯底進行高溫退火以及背面拋光工藝優化,目 前 國 產 襯 底 外 延 前 后 幾 何 參 數 及 工 藝 穩 定 性 均 達 到 了 與 進 口 襯 底 相 當 的 水 平 ,如 圖 3 所 示 ,外 延 后 Bow 和 Warp 值 分 別 減 小 到 25 μm 和 30 μm 以內。

3.2 外延缺陷控制

4H-SiC 外延材料生長的核心技術首先是缺陷控制技術,尤其是對易導致器件失效或者引起可靠 性退化的缺陷控制技術。外延生長過程中襯底缺 陷延伸進入外延層的機理、襯底/外延層界面處的 缺陷轉移轉化規律、缺陷成核機制等方面的研究是 明確襯底缺陷和外延結構缺陷之間相關性的基礎, 能夠有效指導襯底篩選以及外延工藝優化。

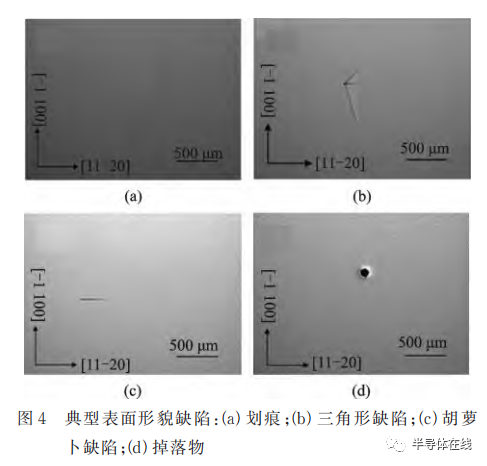

4H-SiC 外延材料中的外延缺陷包括表面形貌 缺陷和晶體結構缺陷。表面形貌缺陷借助顯微鏡 可通過肉眼直接觀察,具有典型的形貌特征。表 面形貌缺陷主要包括:劃痕(Scratch)、三角形缺陷 (Triangular defect) 、胡 蘿 卜 缺 陷(Carrot defect) 、掉落物(Downfall)以及顆粒(Particle) 等 ,如 圖 4 所 示 。在 外 延 過 程 中 ,外 來 顆 粒 異 物 、 襯底缺陷和表面損傷以及外延工藝偏差均可能影 響 局 部 臺 階 流 生 長 模 式 ,從 而 產 生 表 面 形 貌 缺陷。

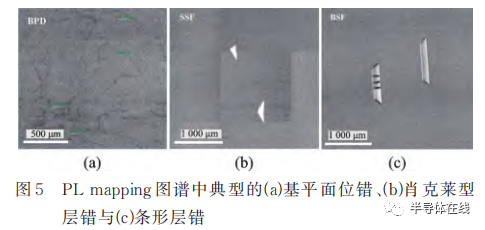

4H-SiC 外 延 層 中 的 晶 體 結 構 缺 陷 主 要 包 括 點、線及面缺陷,其中點缺陷包括雜質原子、空位、 間 隙 原 子 及 其 復 合 體 等 ,線 缺 陷 包 括 微 管 (MP)及 螺 位 錯(TSD)、刃 位 錯(TED)、 基平面位錯(BPD) 等各類位錯 ,面缺陷主要為 各類堆垛層錯(SF)等。晶體結構缺陷除微管以 外,特征尺寸極小,無法借助顯微鏡直接觀察。光 致發光成像(PL mapping)是檢測基平面位錯及堆 垛層錯的有力手段 。在 PL mapping 圖中基平 面 位 錯 表 現 為 沿方 向 的 異 色 線 條 ,如 圖 5 (a)所示;堆垛層錯在 PL mapping 圖有兩種典型的形貌 :三角形和條形(梯形),如圖 5(b)和(c)所 示。大部分三角形層錯為肖克萊(Shockley)型層 錯(SSF),大 部 分 條 形 層 錯(BSF)為 弗 蘭 克(Frank)型層錯。

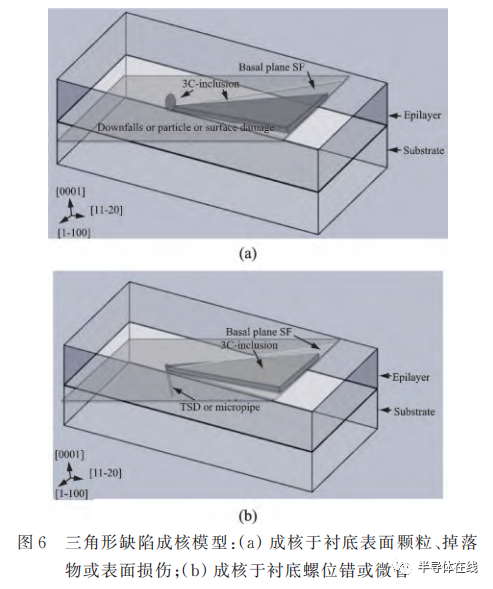

表 面 形 貌 缺 陷 中 掉 落 物 、三 角 形 缺 陷 和 胡 蘿 卜型缺陷會導致芯片反向耐壓失效,屬于“致命” 缺陷。其中掉落物缺陷主要源自生長過程中反應 室上壁及側壁的顆粒掉落,可以通過優化反應室 石墨耗材周期性維護流程進行優化。三角形缺陷 呈三角形形狀,形貌中含有兩條及兩條以上的邊 線 ,具 有 方 向 性 ,第 三 條 邊 與方 向 幾 近 成 90°。三 角 形 頭 部 有 時 有 一 明 顯 的 小 三 角 形 凹 痕 或掉落物。胡蘿卜缺陷由基平面層錯、棱柱面層 錯和兩者交界處的梯桿狀位錯組成,和三角形缺 陷一樣,一般起始于外延層和襯底交界處,胡蘿卜 缺陷具有類似胡蘿卜的形貌,呈線型且一端較粗, 一 般 平 行 于方 向 。本 課 題 組 與 北 京 天 科 合達半導體股份有限公司合作,研究了三角形缺 陷以及胡蘿卜缺陷的起源 。研究結果發現一 部分三角形缺陷成核于襯底中的螺位錯或微管, 而 另 一 部 分 三 角 形 缺 陷 則 是 自 發 成 核 ,如 圖 6 所 示 。通 過 降 低 緩 沖 層 C/Si 比 可 以 有 效 降 低 襯 底 中螺位錯轉化為三角形缺陷的幾率且抑制三角形 缺 陷 沿[1-100]方 向 的 缺 陷 擴 展 。通 過 優 化 襯 底 刻蝕時間及溫度可以有效消除由襯底表面加工損 傷引入的劃傷周邊臺階聚并形貌以及三角形缺陷 的成核幾率。

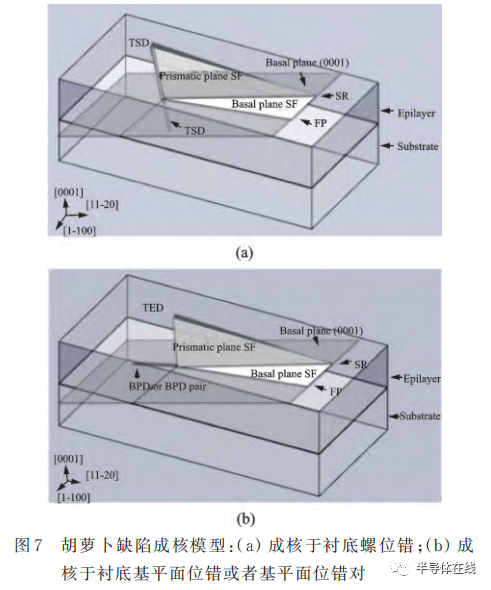

胡蘿卜缺陷主要來源于襯底螺位錯和基平面 位錯等晶體缺陷,如圖 7 所示。正常襯底和會產生 大量胡蘿卜缺陷的襯底,在表面散射光頻道分析圖 中存在明顯差異。基于上述研究結果,通過對同晶 錠襯底的無損篩選,可以有效剔除會導致胡蘿卜缺 陷密度超標的襯底。

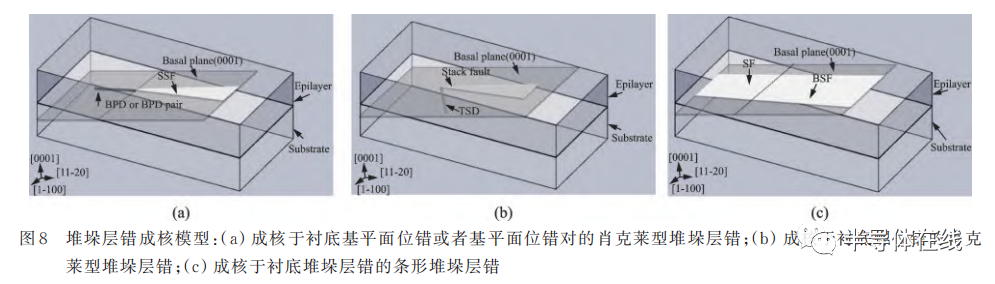

堆垛層錯會降低器件擊穿電壓以及增大反向漏 電,影響器件的性能及可靠性。外延層中堆垛層錯,主要源自襯底缺陷,如圖 8所示。其中 BSF主要成核 于襯底中的堆垛層錯,SSF主要成核于襯底中的 BPD 或 TSD。源自襯底缺陷的堆垛層錯在 PL-mapping圖 像中,沿[11-20]方向的特征尺寸長度與外延層的厚度 成 正 比 。源 自 外 延 工 藝 偏 差 的 堆 垛 層 錯 在 PL-mapping 圖像中具有相對較小的特征尺寸長度。通過優化襯底氫氣刻蝕工藝、降低初期外延速率、提 高生長溫度等工藝優化來降低層錯密度。

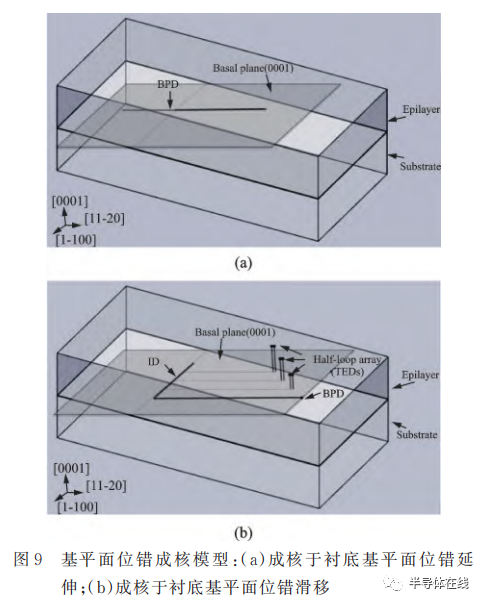

BPD 在電子-空穴復合作用下會發生不全位錯 滑移,在雙極型器件有源區或者 MOSFET 體二極 管區域內擴展形成新的肖克萊層錯,增加器件的導 通電阻,導致器件正向開啟電壓漂移,嚴重影響器 件可靠性 。外延層中的 BPD 主要來源自襯底 BPD 位錯延伸,如圖 9 所示。大部分襯底 BPD 在 外延界面處轉化為具有相同伯格斯矢量且彈性勢 能更低的 TED。通過中斷生長以及復合緩沖層設 計可以進一步提高 BPD-TED 的轉化率。生長過 程中溫度、摻雜濃度差異引入的剪應力也會誘發界 面位錯(ID)滑移并產生基平面位錯延伸進入外延 層。通過優化緩沖層 C/Si 比、溫度以及外延速率 切 換 方 式 等 工 藝 條 件 可 以 降 低 此 類 基 平 面 位 錯 密度。

3.3 均勻性控制

在水平式外延爐中,源沿進氣方向在單晶襯底 徑向的耗盡造成了外延片片內各點厚度及摻雜濃度 的差異。如果源的耗盡接近線性耗盡,通過基座氣 浮旋轉便可以有效消除由源分布引起的不均勻性。然而大部分源的耗盡方式更加接近于二次函數或指 數型耗盡,通過基座氣浮旋轉并不能有效消除由源 分布引入的不均勻性 。在前期的研究工作中,本 課題組通過正交實驗,明確了 C/Si比、Cl/Si比、主氫 流量、生長溫度、三路氣體比等工藝參數對 SiC 外延 厚度和摻雜濃度均勻性指標影響的主次順序,有效 提高了 100 mm SiC 外延片的厚度及濃度不均勻性。

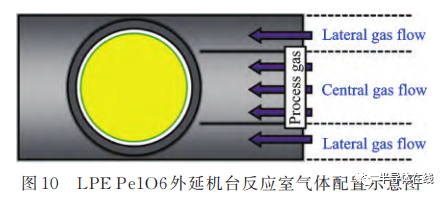

當外延尺寸上升至 150 mm 之后,外延片片內 摻雜濃度和厚度均勻性對比 100 mm 外延片存在明 顯退化,主要原因在于外延片中心點和最邊緣點厚 度及摻雜濃度差異較大。借助反應室的特殊的氣 路設計可以對 150 mm 外延片的片內均勻性進行有 效調控。如圖 10 所示,反應室中央氣路對應外延片 4 英寸區域,側邊氣路對應 150 mm 邊緣區域,通過 加大側邊氣路氫氣流量配比,可以在提高邊緣區域 外延厚度的同時降低中心區域外延厚度,進而可實 現優化外延厚度均勻性的目的。同時通過在側邊氣路通入額外的摻雜源,補償邊緣摻雜濃度,可實 現優化摻雜濃度均勻性的目的。

3.4 基于自主外延材料的 SiC MOSFET 研制

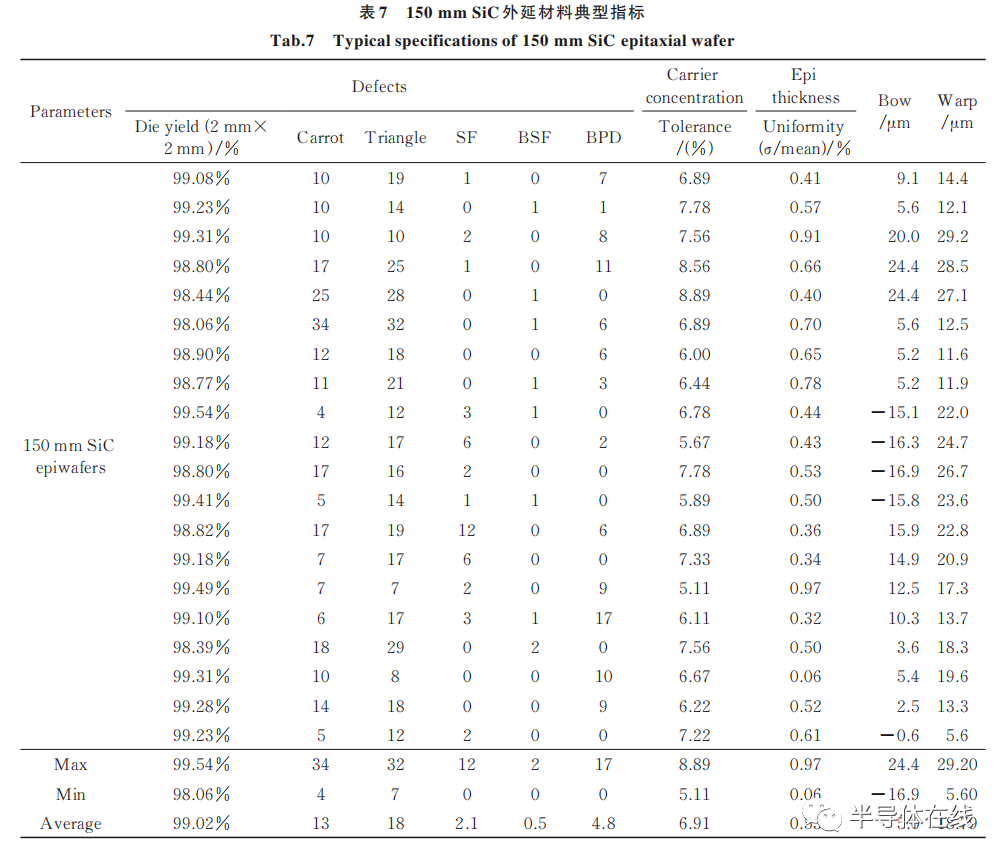

通過上述關鍵技術攻關,寬禁帶半導體電力電 子器件國家重點實驗室基于國產單晶襯底的 4HSiC 同質外延材料典型外延指標如表 7 所示,達到了 國際主流產品水平。

采用自主 4H-SiC 同質外延材料,2019 年寬禁 帶 半 導 體 電 力 電 子 器 件 國 家 重 點 實 驗 室 基 于 150 mm 工 藝 平 臺 開 發 了 G1 1 200~1 700 V SiC MOSFET 器 件 ,2022 年 開 發 了 G2 650~1 200 V SiC MOSFET 器件,柵壓 18 V 驅動時 1 200 V 器件 比導通電阻較 G1 降低 35%。G2 SiC MOSFET 產 品適用于車載充電器(On board charger,OBC)、主 驅電機控制器和光伏儲能等領域。SiC MOSFET 系 列 產 品 中 OBC 裝 車 量 超 過 一 百 萬 臺 。采 用 1 200 V/25 mΩ SiC MOSFET 芯片的 400 A 三相全 橋 SiC 功率模塊,完成萬公里路實驗驗證。光伏升 壓變換器采用 1 200 V SiC MOSFET 實現了低開關 損耗與高開關頻率,儲能端使用 SiC MOSFET 提升 了 功 率 轉 換 效 率 ,1 200 V/75 mΩ 和 40 mΩ SiC MOSFET 產品出貨量近百萬只。

采用平面型 MOS 結構,基于自主材料研制了芯 片尺寸為 8.0 mm×8.0 mm 的 6.5 kV SiC MOSFET 器件,通過終端及外延結構優化,實現了擊穿電壓 7 600 V 和 低 導 通 電 阻 160 mΩ。國 家 電 網 采 用 6.5 kV/400 A SiC MOSFET 功 率 模 塊 ,研 制 出 35 kV/5 MW 全 SiC 電力電子變壓器,并在柔性變電 站示范應用 。相比 Si 器件裝置,SiC 基變壓器體 積、重量、損耗減少 90% 以上,有望極大推動我國高 壓輸變電技術發展。目前基于自主材料研制的 SiC MOSFET芯片樣品最高耐壓為 15 kV,該芯片尺寸為 9.2 mm×9.2 mm,實現了擊穿電壓 16 kV和導通電阻 650 mΩ。15 kV SiC MOSFET 的導通電阻 RON,SP可 達 204 mΩ·cm2,已接近單極型 SiC器件的理論極限。

4 結論

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

國產 SiC 外延設備和單晶襯底取得了顯著的進 展,國內企業已經能夠批量生產 150 mm SiC 外延材 料并已有 200 mm SiC 外延片樣品的報道,與國外龍 頭企業差距不斷縮小。基于國產單晶襯底,寬禁帶 半導體電力電子器件國家重點實驗室完成了外延 生長關鍵技術攻關,150 mm SiC 外延材料產品表面形貌缺陷密度≤0.5cm-2,BPD 密度≤0.1cm-2,片 內摻雜濃度不均勻性≤5%,片內厚度不均勻性≤ 1%,達到國際主流產品水平。基于自主外延材料 研制的 650~1 200 V SiC MOSFET 器件已批量應 用于新能源汽車車載充電器,后續將進一步拓展應 用至主驅電機控制器。

對 標 國 際 先 進 水 平 ,國 內 商 業 化 的 150 mm 4H-SiC 單晶襯底還需要進一步提高技術能力,降 低 位 錯 密 度 并 提 高 單 晶 生 長 及 加 工 良 率 。針 對 車 規 級 MOSFET 器 件 應 用 ,在 保 證 現 有 致 命 型 (Killer)外 延 缺 陷 控 制 水 平 的 基 礎 上 ,需 與 器 件 端聯合攻關,深入研究表面微坑、堆垛層錯、基平 面位錯等非致命型(Nonkiller)外延缺陷導致器件 可 靠 性 退 化 的 機 理 ,提 出 對 應 的 篩 選 和 控 制 方法。

新能源汽車、光伏和儲能等中低壓應用推動了 SiC 電力電子產業快速增長,在電網和軌道交通等 高壓領域,SiC 電力電子的應用優勢也初步彰顯,亟 待聯合攻關實現批量工程應用。高可靠、大電流密 度的 SiC MOSFET 器件是實現持續增長的關鍵,外 延是鏈接單晶襯底及器件的核心。全產業鏈需要 抓住市場爆發和國產化替代的機遇期,持續提升單 晶襯底、外延材料和器件關鍵技術能力,縮小與國 際龍頭企業的技術和產業化水平差距。

來源:固體電子學研究與進展第 43 卷 第 2 期

作者:趙志飛1,2 王 翼1,2 周 平1,2 李士顏1,2 陳谷然1,2 李 赟1,2??

(1 南京電子器件研究所,南京,210016)

(2 寬禁帶半導體電力電子器件國家重點實驗室,南京,210016)

審核編輯:湯梓紅

-

MOSFET

+關注

關注

147文章

7201瀏覽量

213621 -

半導體

+關注

關注

334文章

27515瀏覽量

219773 -

天線

+關注

關注

68文章

3206瀏覽量

140901 -

SiC

+關注

關注

29文章

2841瀏覽量

62721 -

5G

+關注

關注

1355文章

48479瀏覽量

564781

原文標題:【半導光電】基于國產單晶襯底的150 mm 4H-SiC 同質外延技術進展

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

科銳開發出直徑150mm的n型4H-SiC外延晶圓

改善4H-SiC晶圓表面缺陷的高壓碳化硅解決方案

150mm晶圓是過去式了嗎?

尖嘴鉗150mm是指什么

4H-SiC離子注入層的歐姆接觸的制備

基于簡單的支架多片4H-SiC化學氣相沉積同質外延生長

簡述碳化硅襯底的國產化進程

8英寸導電型4H-SiC單晶襯底制備與表征

國產CVD設備在4H-SiC襯底上的同質外延實驗

半導體襯底和外延有什么區別?

基于國產單晶襯底的150mm 4H-SiC同質外延技術進展

基于國產單晶襯底的150mm 4H-SiC同質外延技術進展

評論