摘要

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

隨著物聯網時代的來臨,傳統的傳感器芯片與存算芯片相分離的架構已難以滿足實際場景的 需求。3D集成技術能夠縮短傳感器芯片與存算芯片間的物理距離,實現功能擴展,提升系統能效。晶圓級集成由于對準精度高和互連密度大,一直是學界和產業界的研究熱點。文章對晶圓級集成 技術中的兩種主流工藝,包括硅通孔和混合鍵合工藝,進行了系統性介紹;并結合國內外多個研究 機構的最新進展,對其發展方向進行了展望,以實現適用于感存算一體化芯片的晶圓級集成工藝。

0 引言

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

進入物聯網時代,各種傳感器終端的數量呈幾 何倍數增長,需要對海量的數據進行處理,來獲取有 用的信息。現有傳感器一般將采集到的信號進行壓 縮編碼后,傳輸到云端計算機,在云端解壓后,基于 部署在云端的模型實現信號的進一步處理,如目標 識別、目標檢測等。這種模式需要經過壓縮、傳輸、解壓縮、模型計算等多個步驟,會帶來延時、隱私安 全、功耗、成本等一系列問題,難以滿足實際需求。將傳感器芯片與存算一體化芯片進行三維集成,可 以大大簡化系統設計和信息處理過程,節省系統功 耗,實現高性能感存算一體化芯片。

三維集成工藝的好壞會對整個集成單元的電學 性能、熱學性能和力學性能產生影響,直接關系到最 終產品的成功與否。三維集成主要有晶圓級集成和 芯片間互連兩種技術路線,晶圓級集成由于其對準 精度高且互連密度大,成為產業界和學界的研究熱 點。目前晶圓級三維集成的主流工藝主要有硅通孔(through-silicon via,TSV)和混合鍵合( hybrid bond? ing,HB)兩種。

1硅通孔工藝

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

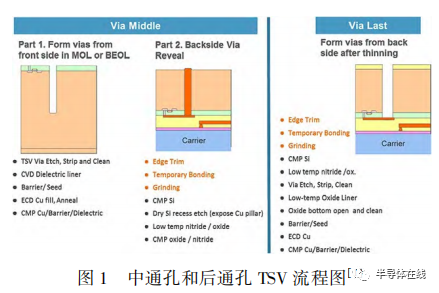

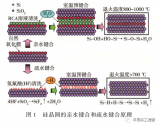

TSV是一種穿透硅基板或芯片的垂直互連結 構,用來完成上下晶圓或芯片間的電學連接。TSV技術依據通孔形成的順序可以分為先通孔( via first)、中通孔(via middle)和后通孔(via last)三種工 藝類型。圖1為中通孔和后通孔的流程示意圖,主要包含以下幾個步驟:通孔的形成、通孔的填充以 及填充后的表面處理。TSV作為一種3D集成技 術,已廣泛應用在圖像傳感器等領域中。

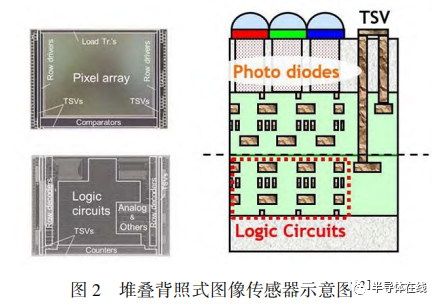

Sukegawa等人開發了一種堆疊背照式圖像 傳感器( backside illumination - CMOS image sensor, BI-CIS),包括傳統的背照式圖像傳感器技術和65 nm的標準邏輯技術。新型的堆疊工藝將傳統的 支撐基板替換為邏輯基板,能夠采用獨立于CIS工 藝的技術制作先進的邏輯電路。如圖2所示,整個 芯片由兩部分組成,芯片的上半部分由傳統的90 nm的1P4M BI-CIS工藝形成;芯片的下半部分由65 nm的1P7M邏輯工藝形成。上部CIS芯片和 下部邏輯芯片完成堆疊之后,在芯片的頂部制作彩 色濾光片和微透鏡,頂部和底部之間通過TSV實現電學連接。

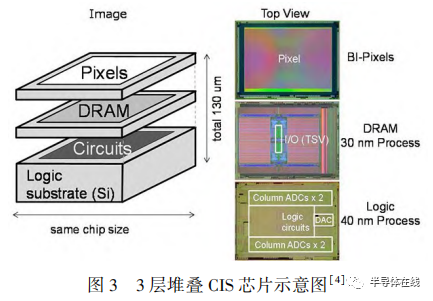

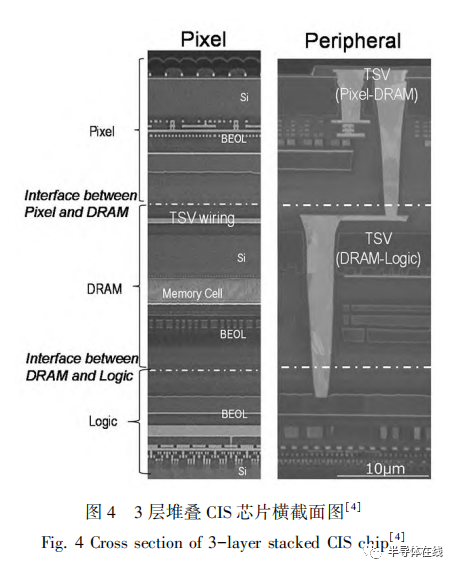

Tsugawa等人在像素-邏輯兩層堆疊背照式 圖像傳感器的基礎上,在中間層加入DRAM作為緩 存,開發了一種集成像素晶圓、DRAM晶圓和邏輯晶 圓的晶圓級集成工藝,如圖3和圖4所示。在單獨 制作像素、DRAM、邏輯晶圓后,首先將DRAM晶圓 倒置與邏輯晶圓面對面鍵合。接下來,將DRAM晶 圓的Si基板減薄,并形成用于連接DRAM晶圓和邏 輯晶圓的TSV布線。最后,將像素晶圓倒置并將其 鍵合到DRAM/邏輯堆疊晶圓上,將像素晶圓的背面 減薄,形成TSV。通過在像素晶圓邏輯晶圓之間堆 疊DRAM晶圓,有助于減少I/ O口數目,降低功耗,并且實現對高速鏡頭的捕捉。

2混合鍵合工藝

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

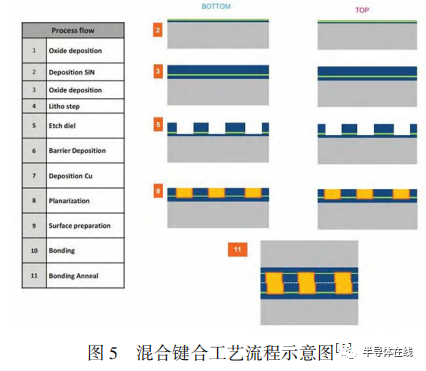

相較于硅通孔工藝,混合鍵合工藝更為簡單,混 合鍵合可以同時實現兩個基板間的物理連接和電氣 連接,并且能夠以密度更高的垂直互連實現更小的 尺寸。圖5為混合鍵合工藝的流程示意圖,其關鍵 步驟包括銅通孔的制作、表面平坦化、表面激活、對 準以及鍵合后退火。首先,通過深反應離子刻蝕來 形成通孔,利用電鍍方式填充銅。再通過化學機械 研磨進行表面平坦化,表面平整度和銅通孔的凹陷 度會對最終鍵合界面質量產生重要影響。接下來利用等離子體對表面進行激活,為預鍵合做準備。上 下晶圓對準,完成預鍵合,經過退火操作,來進一步 促進銅通孔鍵合面的擴散,完成良好的電學連接。銅-銅混合鍵合被認為是用于20 μm間距以下最有 前途的3D集成解決方案之一,已成為3D集成的 主流技術之一。

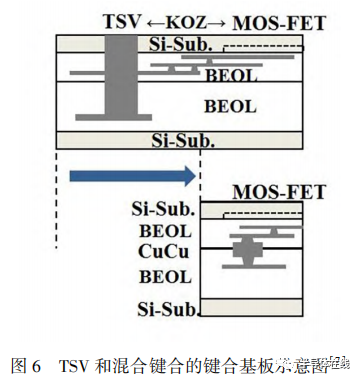

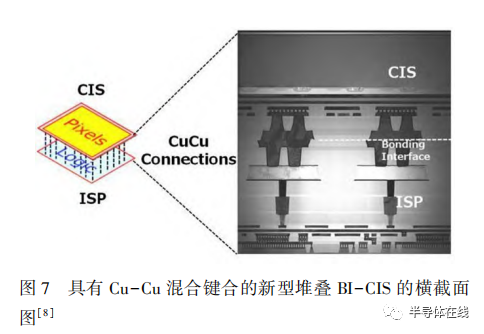

Kagawa等人利用混合鍵合工藝成功制造了2250萬像素、1 / 2.6尺寸的背照式圖像傳感器,其中 混合鍵合間距為4 μm。如圖6所示,與傳統采用硅 通孔(TSV)工藝進行層間連接的堆疊背照式傳感器 不同,銅-銅混合鍵合能夠實現細間距和大規模連 接,可以提高電路設計靈活性,并進一步減小芯片尺 寸。由圖7可以觀察到,退火后的上下側銅通孔連 接牢固,鍵合界面無空洞,表現出良好的電學互連和 可靠性。

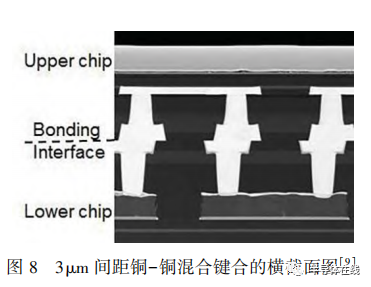

之后,Kagawa等人通過進一步優化工藝,提 高晶圓對準精度,成功在300 mm晶圓上將混合鍵 合間距縮小至3 μm,并且使鍵合對達到300萬。其 中,銅通孔的尺寸為1.5 μm,通孔間空白區域尺寸 為1.5 μm,新的鍵合工藝成功將對準誤差控制在0. 5 μm以內,保證了鍵合連接的穩定性。如圖8所 示,每對Cu-Cu鍵合牢固地連接上芯片和下芯片,鍵合界面沒有任何缺陷或空隙。

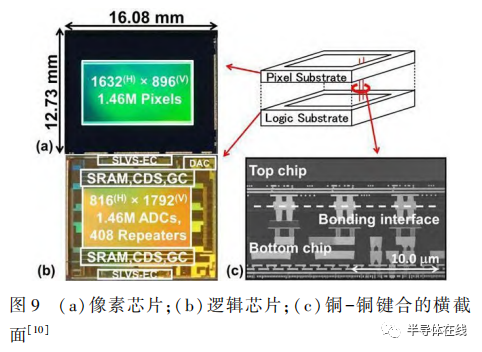

Sakakibara等人通過銅-銅混合鍵合工藝,實現CIS芯片與邏輯芯片的像素級連接,如圖9所 示。CIS芯片采用90 nm的1P4M工藝制造,像素間 距為6.9 μm;邏輯芯片采用相對先進的65 nm的1P7M工藝制造。通過Cu-Cu連接直接將ADC單元集成在像素下方,能夠將所有像素值同時讀出,進 行數據的并行處理,使得最大拍攝幀率能夠達到660fps。

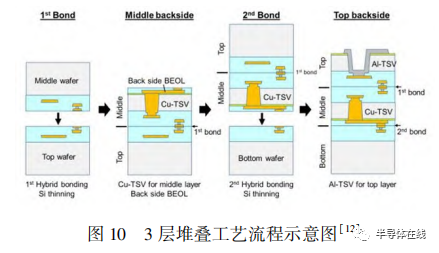

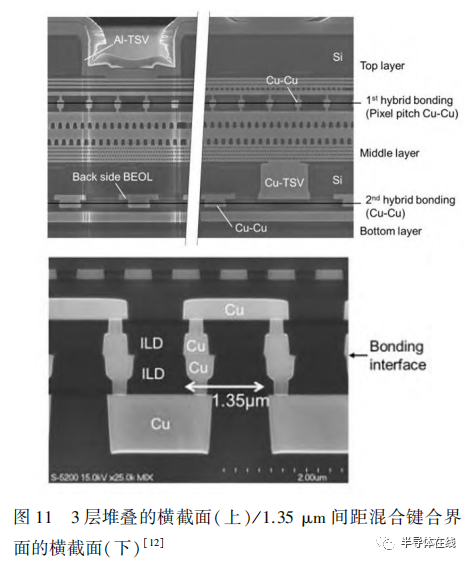

Tanida等人成功展示了采用全混合Cu-Cu直接鍵合工藝制造的三層堆疊背照式圖像傳感器(BSI),與只采用硅通孔(TSV)連接的三層堆疊背照 式圖像傳感器相比,混合鍵合連接能夠實現更高性 能和更多功能。圖10為其3層堆疊工藝流程示意 圖。首先,利用混合鍵合將中間層鍵合到頂層。在 中間層Si減薄之后,制作Cu-TSV和背面BEOL,作 為中間層正面和背面之間的電學通路。再進行第二 次混合鍵合,利用Cu-Cu鍵合將中間層的背面與底 層連接。最后,減薄頂層Si并形成貫穿頂層Si的Al-TSV。研究團隊還發現鍵合晶圓表面上的等離 子體活化條件是提高較小間距的Cu-Cu鍵合成品 率的關鍵因素,通過優化等離子體活化氣體比例,成 功實現了間距為1.35 μm的混合鍵合,圖11為鍵合 橫截面的TEM圖。

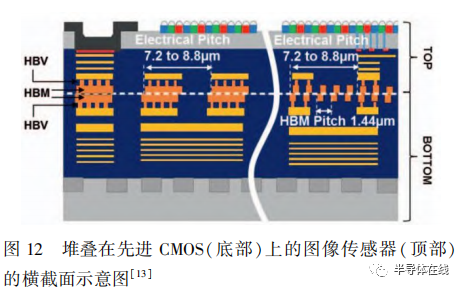

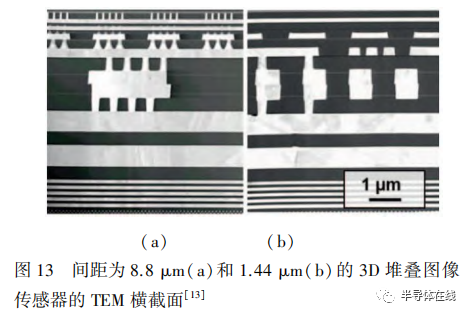

STMicroelectronics和CEA-LETI機構的研究人 員合作開發了用于3D堆疊CMOS圖像傳感器的200 mm和300 mm 晶圓級混合鍵合工藝。在200 mm晶圓級混合鍵合工藝中,研究人員通過優 化晶圓鍵合對準系統、偏移補償程序、測量系統、優 對準鍵,以及使用反饋回路來提升晶圓對準精度。通過進一步優化工藝和設備,成功將晶圓級混合鍵 合擴展到300 mm晶圓上,并且鍵合通孔間距達 到6 μm,可完全符合BSI進行3D堆疊的要求。更 小鍵合通孔間距能夠實現更高密度互連,但是較小 間距互連可能會危及電氣和可靠性性能。研究團隊 研究了鍵合通孔間距收縮對互連穩健性的影響,從工藝、器件性能和魯棒性的角度出發,分別研究了8.8 μm到1. 44 μm鍵合間距,對3D堆疊背照式CMOS圖像傳感器性能的影響,如圖12和圖13所 示。

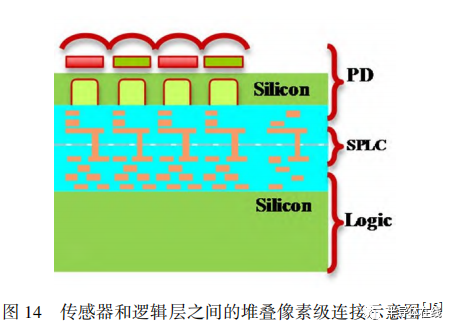

國內圖像傳感器廠商豪威科技也在進行堆 疊式圖像傳感器研究。圖14是一款雙通道轉換增 益的堆疊式圖像傳感器示意圖,其中像素單元的部 分器件被布置到邏輯層,以提高傳感器填充系數,增 加功能。傳感器晶圓和邏輯晶圓單獨制造,并通過 間距為1.5 μm的混合鍵合通孔進行像素級連接,像 素級連接使得數據能夠從傳感器層上的像素陣列快 速傳輸到邏輯層上的器件陣列。

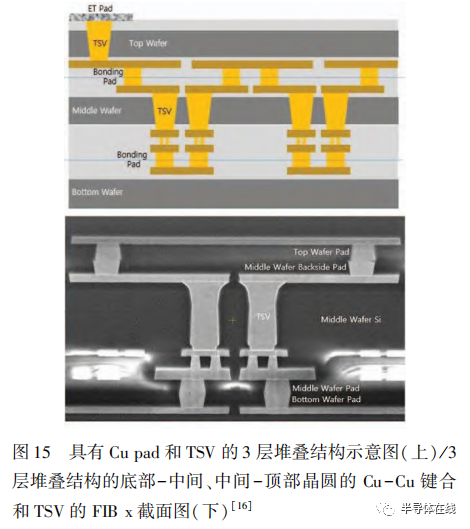

可以看到,目前采用混合鍵合工藝的主流產品 是堆疊式圖像傳感器,各大研究機構也在推動混合 鍵合技術不斷完善,以使其成為一項通用的三維集 成技術,能夠應用在其他領域及產品。三星Sam?sung通過將TSV工藝和混合鍵合工藝結合,推出X- Cube [16]工藝,應用于多枚芯片堆疊封裝中。與采用 多個芯片平面封裝的方式相比,X-Cube 3D封裝使 整個芯片結構更加緊湊,能夠進行更高效和簡單的I/ O設計,并且由于更短的互連會帶來更低的電阻。Samsung研究人員通過優化工藝參數,利用面對面(F2F)和背對面(B2F)兩種方式,實現了多個晶圓 的堆疊集成。以圖15中3片晶圓堆疊為例,每片晶 圓首先通過大馬士革銅線后端工藝來制作混合鍵合 所需的銅通孔,為了構造用于混合鍵合的銅通孔,每 片晶圓應該至少包含兩層金屬層。中部和底部晶圓 采用面對面的方式鍵合在一起,緊接著對中部晶圓 的背部進行減薄,加工形成TSV以及用于與頂部晶 圓進行混合鍵合的銅通孔。頂部晶圓以背對面的方 式與中部/底部堆疊晶圓進行混合鍵合,對頂部晶圓 背部進行減薄并制作TSV用于進行電學測試。

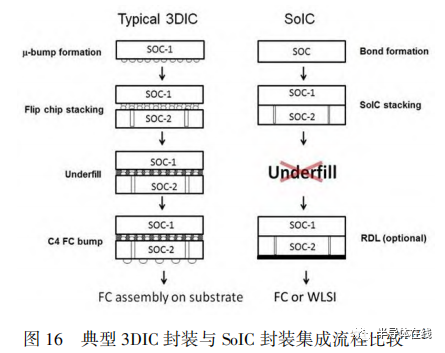

臺積電TSMC發布名為SoIC的三維集成 工藝,是業界第一款邏輯-邏輯、存儲器-邏輯的3D集成工藝。SoIC技術能夠將不同工藝節點、材料、功能和尺寸的芯片進行堆疊,設計和集成更加靈活,使系統能夠以更低的成本和更好的性能進行擴展。

如圖16所示,SoIC不再使用凸點(bump)進行芯片 間的連接,轉為表面更為平整的混合鍵合進行連接,因此 無 須 再 進 行 層 間 縫 隙 填 充。與 傳 統 采 用μ-bump的3D集成方式相比,SoIC能夠提供更高的I/ O鍵合密度,鍵合間距至少小4倍,鍵合密度至少 高16倍。并且實現了更低的功耗、更低的RC延 遲、IR壓降和更低的熱阻。

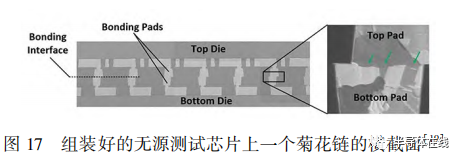

Intel公司也在基于混合鍵合工藝開發自 家的3D集成技術。Intel研究了混合鍵合工藝對頂 部金屬層無源器件和功率傳輸的影響,提出最小化 影響的具體設計。并且通過優化相關工藝參數,來 滿足混合鍵合要求。例如,在制作鍵合金屬層時,避 免引起過度的晶片翹曲;在進行化學機械拋光時,實 現光滑平坦的表面電介質和凹陷受控的鍵合通孔;在鍵合時,保持極其干凈的鍵合表面、高精度對準和 最大化測試覆蓋率。圖17是測試芯片上的一個鍵 合菊花鏈的橫截面,顯示出良好的對準精度和鍵合 界面,可以看到鍵合界面金屬顆粒相互擴散,實現金 屬到金屬的鍵合。

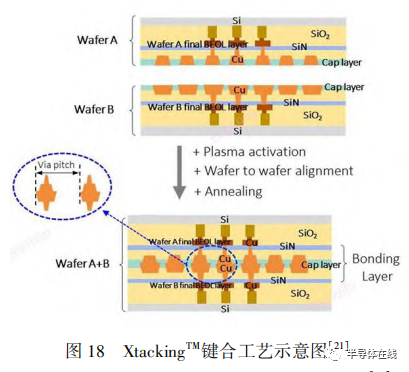

長江存儲YMTC最先在3D NAND Flash制造中 引入混合鍵合工藝,并將其命名為Xtacking。3D NAND Flash由存儲單元和外圍電路組成,在傳 統工藝中,外圍電路和存儲單元并排放置,共享有限 的芯片面積。但是隨著3D NAND存儲單元層數的 增加,外圍電路占整個芯片尺寸的百分比將增加,外 圍電路占據的面積難以忽視。Xtacking工藝通過存 儲單元和外圍電路分別制造在兩片晶圓上,利用混 合鍵合工藝進行層間連接。分離開的存儲單元和外 圍電路可以獨立設計生產,極大提升了工藝靈活性,并縮短了研究周期。圖18是Xtacking鍵合工藝的 簡要描述,兩片晶圓在準備結束之后進行對準,退 火,形成數百萬對具有小間距的金屬通孔,完成電學 連接和物理支撐。研究團隊從測試結構和產品兩個 層面研究了Xtacking工藝鍵合界面的可靠性。在測 試結構級可靠性測試中,Xtacking鍵合層在超長時 間熱或濕度應力后表現出非常穩定的金屬電阻、介 電泄漏、鍵合強度和介電擊穿電壓。在產品級可靠 性測試中,封裝的3D NAND產品表現出類似的優 異可靠性,充分證明了混合鍵合工藝的可行性。YMTC不斷對Xtacking工藝進行改進,到目前為止,已推出Xtacking 2.0和Xtacking 3.0版本,并已有相 關產品面世。

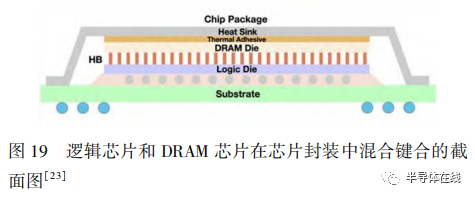

阿里巴巴達摩院提出針對于人工智能應用 的高密度和高能效的近內存計算解決方案,其中利 用混合鍵合工藝來連接邏輯芯片和DRAM芯片,如 圖19所示。晶圓級混合鍵合技術能夠實現高帶寬 集成,實 驗 數 據 表 明,其 能 效 比HBM或DDR SDRAM等片外存儲器解決方案高出200倍,比最先 進的近內存計算解決方案高出至少2倍。DRAM芯 片和邏輯芯片分別基于25 nm和55 nm工藝制造,通過間距為3 μm的銅通孔連接在一起,銅通孔為 兩者間的電學通道。

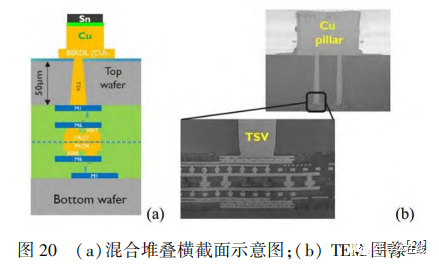

比利時微電子研究中心IMEC基于標準的65 nm工藝技術制造了鍵合通孔間距為2.5 μm的300 mm混合鍵合晶圓片,并且對鍵合晶圓的電學、熱學、力學和可靠性性能進行評估,如圖20所示。研究團隊通過晶圓片上的回環結構來評估混合鍵合 通孔的電學性能,并證明了當測試樣品在4點彎曲 設置中經受1000次機械循環時,混合鍵合界面的質 量不受影響。以及通過在測試芯片的一個單元中產 生熱源,并利用集成溫度傳感器測量兩個晶圓片的 熱響應來評估堆疊晶圓的熱性能,結果表明,溫度傳 感器和熱源相對于外部熱邊界條件的位置在分析實 驗結果時起著重要作用。

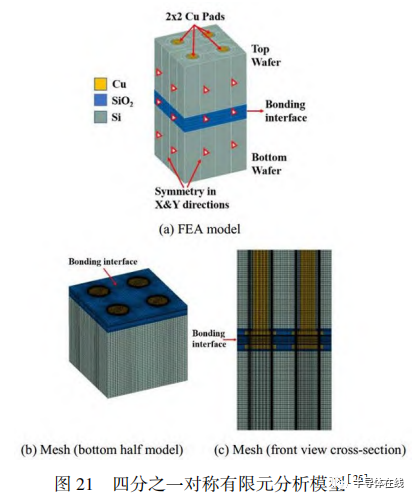

新加坡IME機構基于有限元分析方法對混合 鍵合機制進行了一系列仿真研究,圖21為鍵 合面有限元分析模型。通過對晶圓級混合鍵合工藝 的多個流程進行三維建模,針對各種設計和工藝條件,例如晶圓片翹曲度、銅通孔凹陷值、退火溫度和 退火時間、硅通孔( TSV)深度和銅通孔間距等,從 熱-力-電的角度模擬混合鍵合技術的鍵合過程,詳 細研究影響鍵合完整性的關鍵因素,并提供可能的 改進方法。對混合鍵合工藝進行數值研究可以為實 際設計和工藝提供指南和參考,有助于優化設計和 工藝參數,縮短工藝開發周期和降低研發成本。

海力士半導體SK Semiconductor 、格羅方德GlobalFoundries、富 士 通Fujitsu以 及 三 菱Mitsubishi也對混合鍵合工藝進行了深入研究。

3 結論

本文研究了一種用于5G通信的射頻微系統與天線一體化三維扇出型集成封裝技術. 通過在玻璃晶圓 上使用雙面布線工藝,實現毫米波天線陣列的制作. 將TSV轉接芯片與射頻芯片倒裝焊在玻璃晶圓上,再用樹脂材料 進行注塑,將玻璃晶圓與異構芯片重構成玻璃與樹脂永久鍵合的晶圓. 減薄樹脂晶圓面漏出TSV轉接芯片的銅柱,在 樹脂表面上完成再布線. 把控制、電源管理等芯片倒裝焊在再布線形成的焊盤處,植上BGA焊球形成最終封裝體. 利 用毫米波探針臺對射頻傳輸線的損耗進行測量,結果表明,1 mm長的CPW傳輸線射頻傳輸損耗在60 GHz僅為0.6 dB. 在玻璃晶圓上設計了一種縫隙耦合天線,天線在59.8 GHz的工作頻率最大增益達到6 dB. 這為5G通信的射頻微系統 與天線一體化三維扇出型集成提供了一個切實可行解決方案.

本文對晶圓級集成技術的兩種主流工藝——— TSV工藝和混合鍵合工藝進行了系統性的介紹,綜 合多個研究機構的最新技術成果,對其進行了進一 步詳細說明。

混合鍵合由于其工藝較為簡單,集成密度更高,能夠同時實現電學連接和物理支撐,是接下來研究 和發展的重點。在將混合鍵合工藝應用于感存算一 體化芯片之前,仍有大量研究工作需要進行,包括優 化設計和工藝參數,提高晶圓對準精度,實現低溫退 火以及降低成本等。面向感存算一體化芯片的晶圓級集成工藝的成功開發,將有力推動感存算一體化 技術的進步和實際應用,為我國先進半導體工藝技 術的自主自強做出貢獻。

來源:功能材料與器件學報第 29 卷第 1 期

作者:趙國強1,2 ,趙 毅2,3(1.中國電子科技南湖研究院,;2. 浙江大學信息與電子工程學院;3. 華東師范大學集成電路科學與工程學院)

審核編輯:湯梓紅

-

射頻

+關注

關注

104文章

5591瀏覽量

167836 -

晶圓

+關注

關注

52文章

4922瀏覽量

128057 -

通信

+關注

關注

18文章

6036瀏覽量

136082 -

物聯網

+關注

關注

2909文章

44704瀏覽量

374024 -

5G

+關注

關注

1354文章

48466瀏覽量

564552

原文標題:【半導光電】晶圓級集成技術研究進展

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HRP晶圓級先進封裝替代傳統封裝技術研究(HRP晶圓級先進封裝芯片)

新型銅互連方法—電化學機械拋光技術研究進展

薄膜鋰電池的研究進展

傳感器EMC的重要性與研究進展

太赫茲量子級聯激光器等THz源的工作原理及其研究進展

廢舊鎳氫電池回收處理技術研究進展

量子計算關鍵技術研究進展

晶圓級集成技術研究進展

晶圓級集成技術研究進展

評論