封裝的主要功能之一是為芯片提供電源.以及為芯片提供通向外部和封裝內(nèi)其他芯片的電信號(hào)通路,其電氣性能關(guān)系到I 能否在更高一級組裝中正常工作。在設(shè)計(jì)中,應(yīng)考量如下 3個(gè)方面。

1.信號(hào)完整性

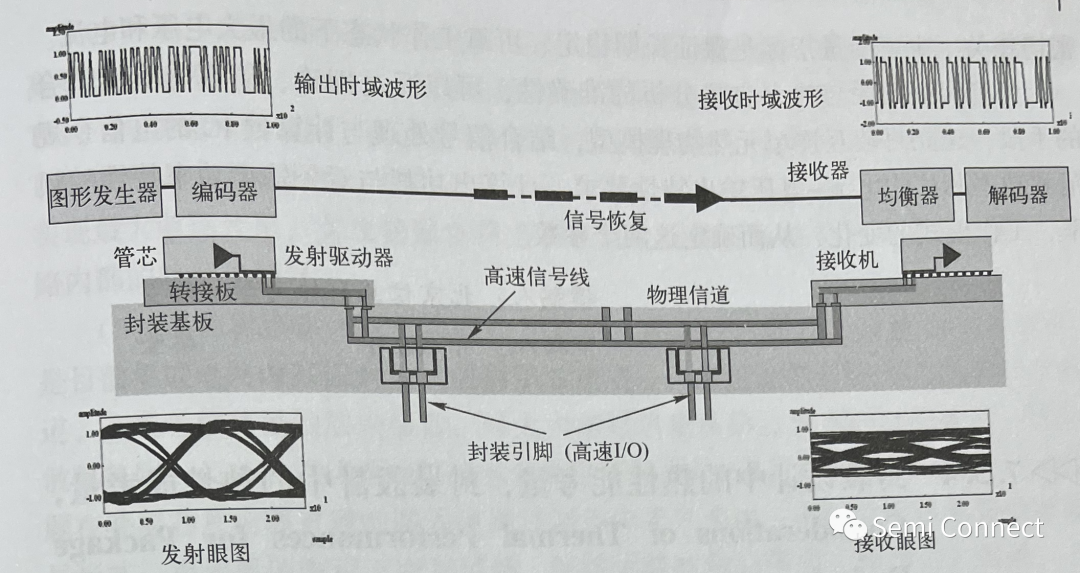

信號(hào)完整性(Signal Integrity, SI)是指電信號(hào)在封裝級互連上傳輸?shù)钠焚|(zhì)包含電壓波形的精度和信號(hào)上升/下降沿到達(dá)接收電路輸人端的時(shí)間精度兩個(gè)方面,具體的衡量指標(biāo)包括延遲、反射、串?dāng)_、時(shí)序、振蕩等方面的電氣指標(biāo)。在封裝實(shí)踐中.因電信號(hào)互連存在串?dāng)_輻射 阻抗失配與延遲等非理想物理因素會(huì)出現(xiàn)電信號(hào)傳輸品質(zhì)劣化(如接收端眼圖閉合)甚至電路無法穩(wěn)定工作的現(xiàn)象。因此,為了保障信號(hào)完整性,必須掌握相應(yīng)的機(jī)理、特性的預(yù)測,以及在設(shè)計(jì)中的糾正方法。目前,信號(hào)完整性主要考量數(shù)字電路的模擬特性,其基本原理和分析問題的角度實(shí)際上與模擬和射頻/微波集成電路封裝是相通的。信號(hào)完整性問題通常出現(xiàn)在工作時(shí)鐘頻率為 50MHz 以上的封裝與 PCB 系統(tǒng)中,目前數(shù)字電路的工作頻率已遠(yuǎn)遠(yuǎn)超出 50MHz,因此信號(hào)完整性問題越來越突出。

從電磁學(xué)原理來看,信號(hào)完整性問題可以歸結(jié)為鄰近信號(hào)之間電磁場的寄生耦合與電磁場結(jié)構(gòu)的畸變、傳輸線結(jié)構(gòu)的非對稱性和不連續(xù)性導(dǎo)致的電磁波傳播奇生模態(tài)、奇生通路與多重反射等。正因如此,在封裝電學(xué)設(shè)計(jì)方法研究中往往通過物理建模、電路建模和實(shí)際測量相結(jié)合的辦法,揭示物理結(jié)構(gòu)參數(shù)對電磁場分布與傳播的影響,從而確定集成電路與其他附屬元件和封裝基板PCB 的性能參數(shù),制定集成電路與元器件布局、高速信號(hào)的布線、濾波接地等結(jié)構(gòu)設(shè)計(jì)規(guī)范,以及與之對應(yīng)的信令規(guī)范(如數(shù)據(jù)的編碼、端接方式等)和信道均衡化措施,使傳輸?shù)浇邮招酒_的信號(hào)在時(shí)序、持續(xù)時(shí)間和幅值方面符合要求,即確保良好的信號(hào)完整性,從而保障接收芯片能正確讀取發(fā)送來的數(shù)據(jù)。在采用恰當(dāng)?shù)男帕詈驼莆招盘?hào)完整性影響機(jī)制的基礎(chǔ)上,就可以建立高速信號(hào)的高可靠傳輸物理通路與機(jī)制。圖所示的是,采用信號(hào)恢復(fù)措施后,使得接收到的眼圖閉合的信號(hào)恢復(fù)到接近驅(qū)動(dòng)器輸出端處的水平。

2,電源完整性

電源完整性(Power Integrity,PI)是指封裝芯片電源引腳處的供電電壓的量值精度和穩(wěn)定性,其衡量指標(biāo)是芯片供電電壓的波動(dòng)范圍及噪聲等。在工程實(shí)踐中,需掌握非理想因素對封裝供電網(wǎng)絡(luò)的影響機(jī)制及其預(yù)測 與評估方法,相應(yīng)地提出;在設(shè)計(jì)中進(jìn)行糾正的方法。電源波動(dòng)必然會(huì)影響信號(hào)的輸出和接收,從而加劇影響信號(hào)的完整性,因此電源完整性和信號(hào)完整性通常要協(xié)同考慮。

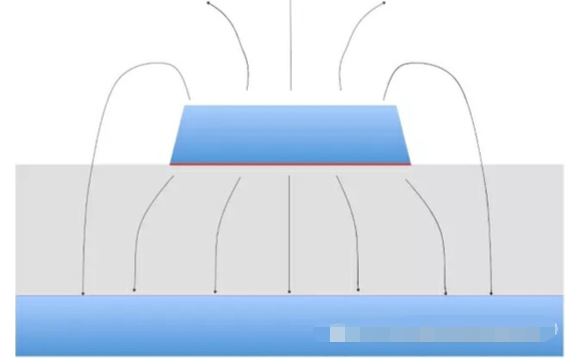

造成電源完整性問題的直接原因主要包括兩個(gè)方面,即電源互連的電阻壓降和電源回路中電流波動(dòng) (如同步開關(guān))造成的電壓波動(dòng)。前者主要為低頻波動(dòng),可以通過對奇生電阻的識(shí)別和在設(shè)計(jì)中減小其電阻值來解決;后者可以造成較高的頻率波動(dòng),影響芯片、封裝和 PCB 三個(gè)層級,通常需要對供電網(wǎng)絡(luò)中的電流通路及IC 典型工作模式 下的電流波形頻譜進(jìn)行分析,識(shí)別出存在顯著奇生電感、電容或電磁輻射的互連結(jié)構(gòu),以及對信號(hào)影響顯著的電源波動(dòng)的頻率分量,然后提出相應(yīng)的削弱其影響的互連物理設(shè)計(jì)。

3.功耗及功率容量功耗及功率容量

指標(biāo)涉及封裝長期工作的熱穩(wěn)定性和電源系統(tǒng)設(shè)計(jì),與器件工作頻率、模式密切相關(guān)。在封裝層面上,除IC本身發(fā)熱之外,功耗的主要來源是封裝互連的熱耗散,其中包括歐姆發(fā)熱和介質(zhì)損耗。當(dāng)前,封裝的微小電互連截面面積僅為數(shù)平方微米,隨著新型介質(zhì)的使用日益廣泛,其歐姆發(fā)熱和介質(zhì)損耗不可忽視;此外,三維集成封裝中納米IC 與穿透1IC 的垂直互連間的納水級互連存在界面聲子作用顯著增強(qiáng)等問題,這也會(huì)導(dǎo)致熱耗散,加劇功耗增長。功率電子器件通常要考慮功率容量,該參數(shù)與功耗和器件的工作穩(wěn)定性密切相關(guān),主要衡量指標(biāo)是保證長期穩(wěn)定、可靠工作狀態(tài)下的最大電壓和電流。

為了保證功耗與功率容量分析的準(zhǔn)確性,可以通過理論、仿真與實(shí)測結(jié)合的手段,建立封裝互連單元熱物理模型,結(jié)合信號(hào)處理與計(jì)算型 IC 的電信令規(guī)范和功率芯片的電流-電壓輸出特性要求,計(jì)算出功耗與對外輸出功率特性隨頻率、工作模式的變化,從而確定這兩個(gè)參數(shù)。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423675 -

封裝

+關(guān)注

關(guān)注

126文章

7902瀏覽量

142966 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1408瀏覽量

95488 -

電氣性能

+關(guān)注

關(guān)注

0文章

32瀏覽量

8464 -

封裝設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

35瀏覽量

11941

原文標(biāo)題:封裝設(shè)計(jì)中的電氣性能考量,封裝設(shè)計(jì)中的電氣性能考量

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

簡單介紹IC的高性能封裝

電容的作用及分布參數(shù)對電氣性能的影響!

連接器電氣性能的穩(wěn)定性如何保證

奇異電氣性能石墨被確認(rèn)

關(guān)于PCB板級設(shè)計(jì)和IC封裝設(shè)計(jì)的信號(hào)完整性100條經(jīng)驗(yàn)法則

防水插頭基本性能之電氣性能

分析高頻應(yīng)用中的銅箔粗糙度對電氣性能的影響

封裝設(shè)計(jì)中的熱性能考量

封裝設(shè)計(jì)中的電氣性能考量

封裝設(shè)計(jì)中的電氣性能考量

評論