基于DWC2的USB驅動開發-0x05 DWC2 USB2.0 IP 寄存器介紹 (qq.com)

前言

驅動的編寫無非就是寄存器的配置,所以我們先要對控制器的寄存器現有一個整體的概覽,知道有哪些寄存器,配置某個功能要操作哪些寄存器,寄存器的整體組織架構,等等。現有了整體了解后面具體莫格模塊和功能的配置式就可以找到地方,然后參考具體的寄存器的描述進行配置。

概覽

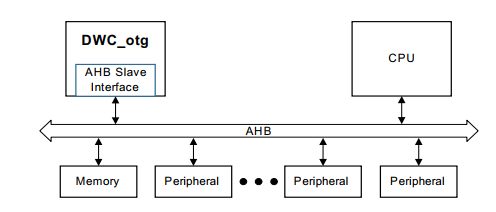

前面DWC_otg_core架構部分,已經介紹了控制和狀態寄存器CSR的一些內容。從架構的角度看CSR塊位于AHB時鐘域,但是有兩個特殊的,一個是電源和時鐘門控寄存器PCGCCTL和控制器中斷寄存器GINTSTS的b[31:29],這些寄存器位位于BIU從模塊中,在斷電模式下依然處于活動狀態。為什么這兩個不一樣呢? 因為要進行低功耗管理,要對AHB和PHY以及RAM的時鐘進行門控即可關閉和打開,如果位于AHB時鐘域那么關閉AHB時鐘域時這個寄存器本身也就斷電了,也就沒辦法退出斷電模式了,所以這個寄存器必須位于AHB時鐘域以外。GINTSTS的b[31:29] WkUpInt SessReqInt DisConnInt也是類似的原因。

站在USB控制器的角度,對應的是AHB從接口,即外部CPU通過AHB主和控制器的AHB從通訊,讀寫控制器的CSR寄存器,注意控制器本身也是要寫CSR的狀態和中斷相關的寄存器的,因為要設置中斷標志各種狀態等,同時也要讀CSR因為要根據寄存器中的配置決定自己的行為。那么就存在CPU和控制器都同時去寫某些寄存器的可能,主要是中斷相關的,比如控制器要置位某個中斷位,而軟件要去清除某個中斷位,此時控制器的寫是優先的,即控制在寫時軟件的寫會忽略掉,這么做的原因是避免丟失中斷事件。

另外注意所有寄存器都是32位訪問的,哪怕寄存器本身只需要一個字節。由于中斷位的設置和清零分別是控制器和軟件通過AHB接口去訪問的,可能同時寫,所以硬件上做了處理,不同中斷位的寫是完全獨立的,控制器和AHB接口可以同時寫不同的中斷位,這是硬件保證的,而不是我們通常的讀-修改-寫的實現方式就是出于該考慮。如果是寫同樣的中斷位呢,那就是上面說的控制器優先忽略AHB的寫。

為了節省空間,HSOT和DEVICE模式的寄存器是共用物理空間的,因為同一時間要不是主機模式要不是設備模式。另外有些寄存器要根據配置決定是否實現,比如如果只有兩個端點,那么其他端點相關寄存器就沒有實現,但是空間還是占用的,這樣是為了方便代碼兼容,也就是寄存器的偏移地址都是固定的,沒有實現的的就空著。未實現的寄存器寫忽略讀返回值不確定。這里注意只有全局控制, 電源和時鐘門控, Data FIFO 訪問,和 Host Port 寄存器是主機和設備都可以訪問的,其他是模式相關的寄存器。如果主機模式去寫設備相關的寄存器(反之亦然)則會產生GINTSTS.ModeMis事件,該為置位,如果使能了對應中斷還會產生中斷,寫會忽略讀返回值不確定。

如果切換了模式則需要重新編程所有相關寄存器,就好比上電復位之后的狀態一樣。

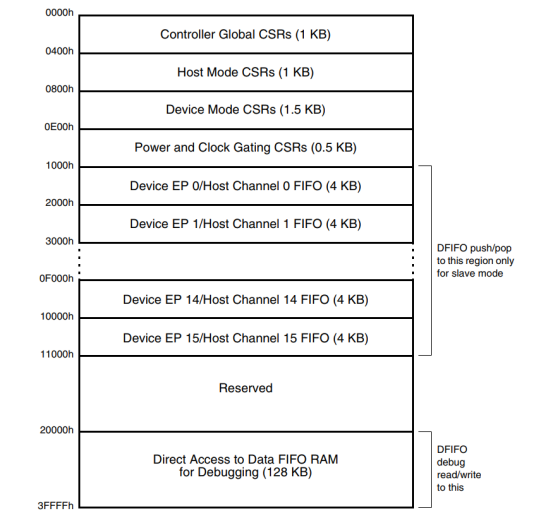

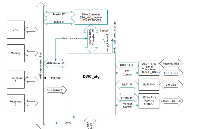

CSR存儲映射

CSR的地址映射是固定的,不隨著配置改變而改變,即每一個寄存器的偏移是固定的,前面已經解釋過了原因。主機和設備模式寄存器占用不同的地址。

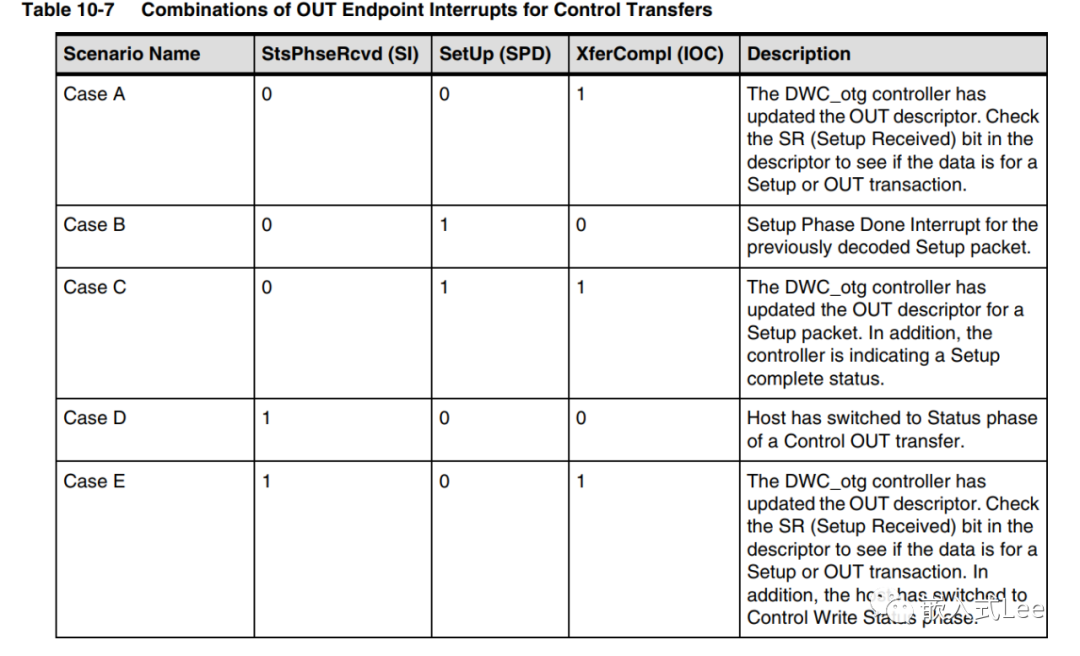

整個寄存器的空間如下所示

閱讀寄存器有一些經驗,

G開頭的代表全局控制寄存器

H開頭的代表主機相關寄存器

D開頭的代表設備相關寄存器

這樣一眼就可以看到寄存器大概是和什么相關的。

Controller Global CSRs (1 KB)部分:主機和設備模式都可以訪問

Host Mode CSRs (1 KB):進入主機模式需要配置的寄存器

Device Mode CSRs (1.5 KB):進入設備模式需要配置的寄存器

Power and Clock Gating CSRs (0.5 KB):實際只有一個寄存器,電源和門控配置,主機和設備模式都可以訪問。

Device EP x/Host Channel x FIFO (4 KB):這些寄存器在主機和設備模式下都可用,用于在給定方向上讀取或寫入特定端點或通道的FIFO空間。在主機通道IN端點則FIFO只讀,OUT端點則FIFO只寫,在設備IN端點則FIFO只寫,OUT端點則FIFO只讀,注意這里的IN和OUT是符合USB規范的IN和OUT即都是針對主機而言的。

Direct Access to Data FIFO RAM for Debugging (128 KB):直接訪問該空間可以查看RAM中數據用于調試使用。

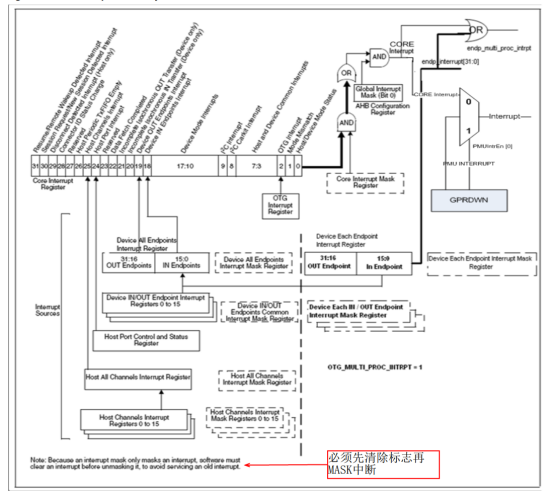

中斷相關寄存器架構

中斷相關寄存器非常重要,可以說USB的驅動就是基于中斷的驅動,所有流都是中斷去驅動的,當然也有所謂的基于事件的驅動比如uC-USB實際也是在中斷服務函數中發送信號量或者事件,在某個線程中或者主循環中去處理事件,本質還是一樣的,還是基于中斷的。中斷中根據狀態決定下一步要做什么。

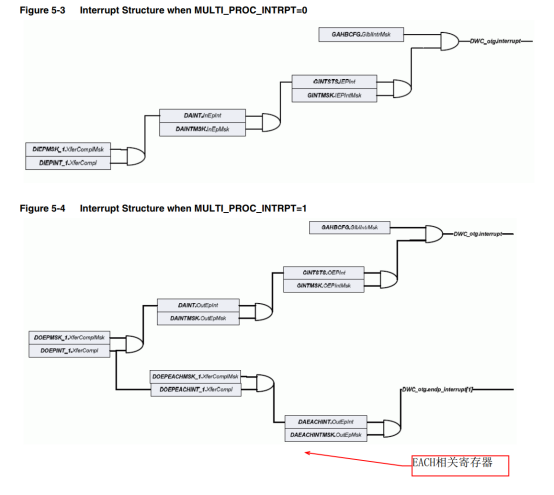

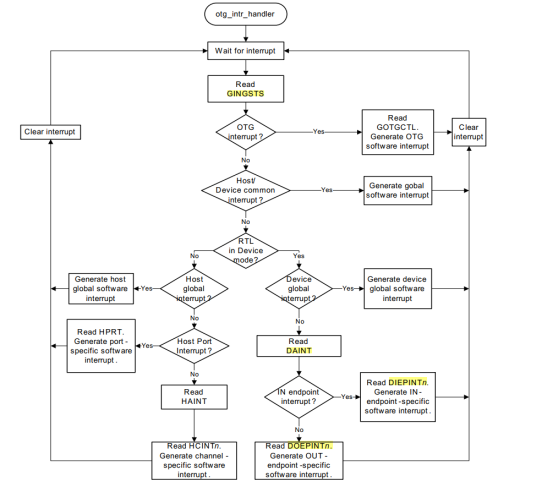

對應中斷狀態寄存器GINTSTS,中斷是一個分層的結構,即總分的形式,先整體有總的中斷狀態,比如是設備IN還是OUT端點中斷,是主機Port還是通道相關中斷,是OTG的中斷,還是內核相關的中斷。比如如果知道是設別IN或者OUT中斷則往下走一層看是DAINT是哪一個IN端點或者哪一個OUT端點的中斷,找到了然后再往下走一層查看具體的DIEPINTi或者DOEPINTi已確認更詳細的中斷信息。

還有就是編程上需要注意使能中斷時一定要先清除中斷標志再使能中斷,避免一使能中斷標志就是置位的馬上就產生中斷,這也是驅動開發的常識。

中斷架構還支持多處理器模式,即可以將中斷信號分發到不同的處理器,以配合多處理器系統使用。支持多處理器中斷模式時就是多了包含EACH字樣的寄存器,供各自處理器使用對應的中斷寄存器。

中斷的處理如下,即和上面提到的層次結構對應

- 先看GINGSTS總中斷狀態,處理全局的中斷

- 然后看主機或者設備通道或者端點相關中斷狀態 比如看DAINT

- 最后看具體是哪一個端點或者通道比如看DIEPINTi,DOEPINTi。

主要使用的寄存器

這里先對一些高頻使用的寄存器做簡單介紹,介紹其對應的功能,詳細的可以再參考具體的寄存器描述。這樣先從整體有一個了解。

| GOTGCTL全局OTG控制和狀態寄存器:控制OTG行為并反映控制器的OTG功能的狀態。 | ||

|---|---|---|

| 11 | DevHNPEn設備設置主機協商協議使能這是設備端的操作 | 設備端收到主機的SetFeature.SetHNPEnable命令時設置該位。0HNP不使能1HNP使能 |

| 10 | HstSetHNPEn主機設置主機協商協議使能這是主機端的操作 | 主機端在SetFeature.SetHNPEnable命令完成后設置該位0主機設置HNP不使能1主機設置HNP使能 |

| GAHBCFG:全局AHB控制寄存器,上電或者切換模式時配置AHB相關信息,只能傳輸前初始化一次 | ||

| 5 | DMAEn使能DMA | 只有IP配置支持DMA才可以選,如果是OTG_ARCHITECTURE = 0則固定為Slave-Only模式沒得選。0 使用Slave模式1 使用DMA模式 |

| GUSBCFG:全局USB配置寄存器,上電或者切換模式時配置AHB相關信息,只能傳輸前初始化一次,USB和PHY相關配置 | ||

| 30 | ForceDevMode強制為設備模式 | 寫1強制為設備模式,而不管utmiotg_iddig信號。設置后需要等25mS生效。只有OTG_MODE = 0, 1 , 2時才有效。 |

| 29 | ForceHstMode強制為主機模式 | 寫1強制為主機模式,而不管utmiotg_iddig信號。設置后需要等25mS生效。只有OTG_MODE = 0, 1 , 2時才有效。 |

| 9 | HNPCapHNP功能使能 | 控制使能HNP功能,寫1使能。注意這里和上面的DevHNPEn和HstSetHNPEn不一樣,這里是有HNP的功能是否使用,只有使用了才支持HNP,才有上面的SetFeature.SetHNPEnable協商之后的結果設置。只有OTG_MODE中支持HNP的模式才有效。 |

| 8 | SRPCapSRP功能使能 | 寫1使能,即對于B設備請求連接的A設備激活VBUS和啟動session。只有OTG_MODE中支持SRP的模式才有效。 |

| 6 | PHYSelPHY選擇 | 0: USB 2.0 高速 UTMI+ 或ULPI PHY,只有OTG_HSPHY_INTERFACE = 1支持高速PHY接口才能設置為01: USB 1.1 全速串行收發器,只有OTG_FSPHY_INTERFACE = 1支持全速接口才能設置為1 |

| 4 | ULPI_UTMI_SelPHY接口ULPI和UTMI選擇 | 0選擇UTMI+1選擇ULPI只有OTG_HSPHY_INTERFACE = 3時同時支持UTMI+和ULPI時才有的選,否則IP配置為什么就是什么。 |

| 3 | PHYIf選擇接口寬度 | 只對選擇了UTMI+的才可配置對于ULPI只能配置為0即8位。0 :8位1:16位 |

| HCFG:主機配置寄存器,只初始化時配置一次 | ||

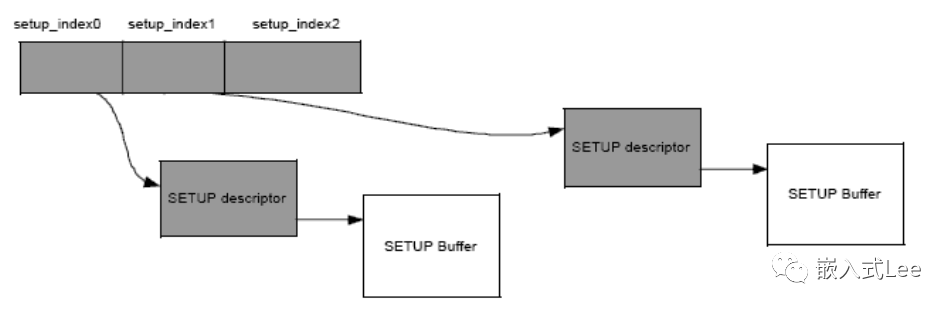

| 23 | DescDMA是否使能基于描述符的DMA | 只有IP配置支持 Scatter/Gather DMA 才能使能。有一下幾種組合GAHBCFG.DMAEn=0, HCFG.DescDMA=0 => Slave mode GAHBCFG.DMAEn=0, HCFG.DescDMA=1 => Invalid GAHBCFG.DMAEn=1, HCFG.DescDMA=0 => Buffered DMA mode GAHBCFG.DMAEn=1, HCFG.DescDMA=1=> Scatter/Gather DMAmode |

| 2 | FSLSSupp | 在主機模式設置該位為1則不管設備支持什么速度都枚舉為全速或者低速,而如果設置為0則根據實際設備支持什么速度就枚舉成什么速度。 |

| HCCHARn:主機通道相關特性設置 | ||

| 19:18 | EPType | 設置通道類型00: Control01: Isochronous10: Bulk11: Interrupt |

| 15 | EPDir | 端點方向0:OUT1:IN |

| 14:11 | EPNum | 端點號 |

| 10:0 | MPS | 對應端點最大包大小 |

| HCTSIZn:主機通道傳輸大小配置 | ||

| 30:29 | PID | 應用設置數據的初始類型,后續的控制器硬件自動更新(所以這里明確了哪些是軟件做哪些是硬件做,之前就提到過寫驅動理解這一點很重要,這些信息都是從手冊中獲取)00: DATA001: DATA210: DATA111: MDATA (non-control) |

| DCFG:設備配置寄存器,枚舉或者控制為設備模式時配置,只初始化配置一次 | ||

| 25:24 | PerSchIntvl | 周期調度間隔只有Scatter/Gather DMA模式才有配置一個微幀內DMA花多少時間去處理同步IN數據,剩余的時間處理非同步傳輸。對于UVC 同步傳輸等可以提高該值以達到高傳輸速率。如果沒有同步端點則該配置被忽略。00: 25% of (micro)frame.01: 50% of (micro)frame.10: 75% of (micro)frame.11: Reserved |

| 23 | DescDMA | 只有IP配置支持 Scatter/Gather DMA 才能使能。 支持的組合如下GAHBCFG.DMAEn=0,DCFG.DescDMA=0 => Slave mode GAHBCFG.DMAEn=0,DCFG.DescDMA=1 => Invalid GAHBCFG.DMAEn=1,DCFG.DescDMA=0 => Buffered DMA mode GAHBCFG.DMAEn=1,DCFG.DescDMA=1 => Scatter/Gather DMA mode |

| 10:4 | DevAddr | 收到主機的SetAddress命令后設置對應的地址值 |

| 1:0 | DevSpd | 軟件設置該值要求硬件枚舉為對應的速度。硬件速度枚舉后反應最終實際的速度。也就是軟件可以要求,但是實際是多少硬件說了算,這也是前面提到的什么是軟件做什么是硬件做的體現,編程要知道這些信息。00:High speed (USB 2.0 PHY clock is 30 MHz or 60 MHz)01: Full speed (USB 2.0 PHY clock is 30 MHz or 60 MHz)10: Reserved11: Full speed (USB 1.1 transceiver clock is 48 MHz) |

| DIEPCTLn/DOEPCTLn:端點控制寄存器,控制對應端點的行為 | ||

| 29 | SetD1PID | Scatter/Gather DMA 和nonScatter/Gather DMA 模式都可使用。配置數據的類型為DATA1只對中斷/批量 IN和OUT端點有效。 |

| 28 | SetD0PID | Scatter/Gather DMA 和nonScatter/Gather DMA 模式都可使用。配置數據的類型為DATA0只對中斷/批量 IN和OUT端點有效。 |

| 19:18 | EPType | 端點類型00: Control01: Isochronous10: Bulk11: Interrupt |

| 10:0 | MPS | 對應端點的最大包大小 |

寄存器描述

閱讀寄存器要注意下寄存器的屬性

| 讀寫屬性 | 描述 |

|---|---|

| RC | 讀清除 |

| RS | 讀置位 |

| RM | 讀會修改寄存器內容 |

| Wo | 只能寫一次 |

| W1C | 寫2清除 |

| W1S | 寫1置位 |

| W1T | 寫1翻轉 |

| W0C | 寫0清除 |

| W0S | 寫0置位 |

| W0T | 寫0翻轉 |

| WC | 寫清除. |

| WS | 寫置位 |

| WM | 寫反轉 |

| no Read Behavior attribute | 不能讀Write-Only. |

| no Write Behavior attribute | 不能寫Read-Only |

| 訪問屬性 | 描述 |

|---|---|

| R | 只讀 |

| W | 只寫 |

| R/W | 可讀寫 |

| R/W1C | 可讀,寫清除 |

| RC/W1C | R讀清除,寫1清除 |

| R/Wo | 可讀,只能寫一次. |

| 屬性 | 描述 |

|---|---|

| Volatile | IP-XACT規格定義的,寫后讀或者連續讀不保證內容一致性。 |

| Testable | IP-XACT規格定義的,可能的值unconstrained, untestable, readOnly, writeAsRead, restore. |

| Reset Mask | IP-XACT規格定義的.復位值不確定.比如其復位值受其他寄存器或者硬件引腳影響或者基于RAM的寄存器. |

| * Varies | 可變的,即根據實際的配置而變化 |

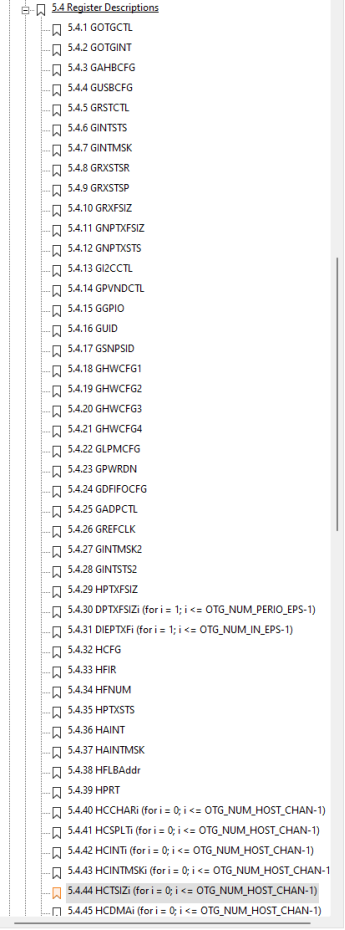

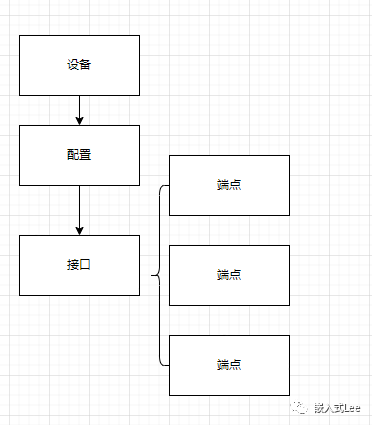

寄存器組織

寄存器按塊組織

DWC_otg_map/DWC_otg_intreg

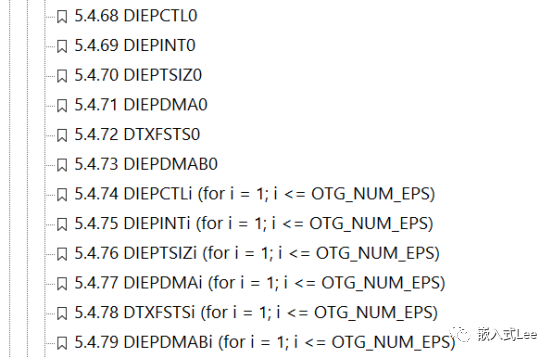

所有寄存器如下

可以看到就是分為G開頭,H開頭和D開頭的。

總結

本文對控制器的寄存器有了一個整體上的概覽,先了解各大概,了解寄存器的組織結構,大致了解一下常用的寄存器。后面編程時再一個個對照每一個寄存器的描述去編寫代碼。

-

寄存器

+關注

關注

31文章

5343瀏覽量

120348 -

usb

+關注

關注

60文章

7945瀏覽量

264639 -

存儲

+關注

關注

13文章

4314瀏覽量

85842 -

驅動開發

+關注

關注

0文章

130瀏覽量

12077 -

DWC2

+關注

關注

0文章

35瀏覽量

131

發布評論請先 登錄

相關推薦

基于DWC2的USB驅動開發-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅動開發-0x04 DWC2 USB2.0 IP 架構介紹

基于DWC2的USB驅動開發-0x07 DWC2 USB2.0 IP 配置參數

基于DWC2的USB驅動開發-IAD描述符詳解

RK3399平臺上USB控制器和PHY的連接方式和配置說明

如何對基于hal庫的DWC2 USB IP進行調試呢

基于DWC2的USB驅動開發-抽絲剝繭再論切換到狀態階段標志DOEPINTn.StsPhseRcvd

基于DWC2的USB驅動開發-0x05 DWC2 USB2.0 IP 寄存器介紹

基于DWC2的USB驅動開發-0x05 DWC2 USB2.0 IP 寄存器介紹

評論