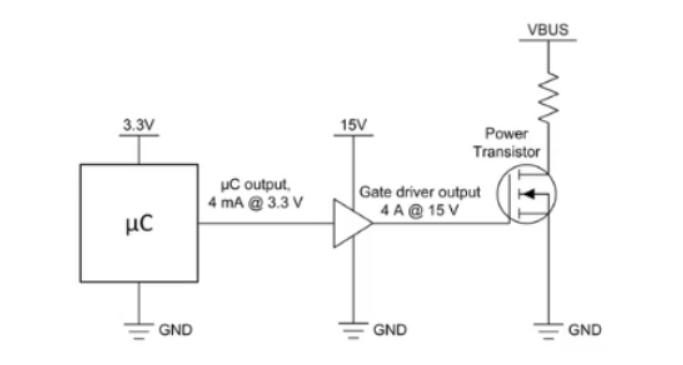

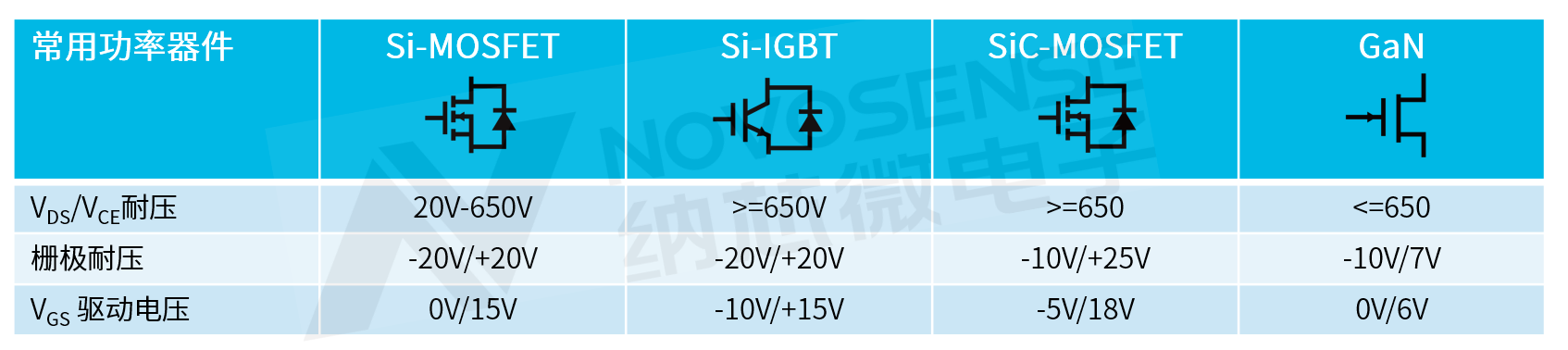

柵極驅(qū)動(dòng)器是一個(gè)用于放大來自微控制器或其他來源的低電壓或低電流的緩沖電柵極驅(qū)動(dòng)器的原理及應(yīng)用分析用中,微控制器輸出通常不適合用于驅(qū)動(dòng)功率較大的晶體管。

GBT/功率MOSFET的結(jié)構(gòu)使得柵極形成一個(gè)非線性電容。給柵極電容充電會(huì)使功率器件導(dǎo)通,并允許電流在其漏極和源極引腳之間流動(dòng),而放電則會(huì)使器件關(guān)斷,漏極和源極引腳上就可以阻斷大電壓。

當(dāng)柵極電容充電且器件剛好可以導(dǎo)通時(shí)的最小電壓就是閾值電壓(VTH)。為將IGBT/功率MOSFET用作開關(guān),應(yīng)在柵極和源極/發(fā)射極引腳之間施加一個(gè)充分大于VTH 的電壓。

考慮一個(gè)具有微控制器的數(shù)字邏輯系統(tǒng),其I/O引腳之一上可以輸出一個(gè)0 V至5 V的PWM信號(hào)。這種PWM將不足以使電源系統(tǒng)中使用的功率器件完全導(dǎo)通,因?yàn)槠溥^驅(qū)電壓一般超過標(biāo)準(zhǔn)CMOS/TTL邏輯電壓。

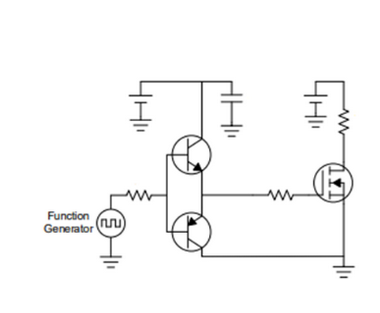

過去,使用雙極結(jié)型晶體管(BJT)圖騰柱驅(qū)動(dòng)低側(cè)配置中的電源開關(guān)。但是,由于柵極驅(qū)動(dòng)器IC的諸多優(yōu)勢(shì)及其附加特性,它日益取代了這些分立式解決方案。典型BJT圖騰柱配置與典型柵極驅(qū)動(dòng)器IC。

分立式電路的一個(gè)顯著缺點(diǎn)是它不提供保護(hù),而柵極驅(qū)動(dòng)器IC集成了對(duì)于確保可預(yù)測(cè)和穩(wěn)定的柵極驅(qū)動(dòng)非常重要的功能。相比之下,BJT圖騰柱允許MOSFET產(chǎn)生壓降,但漏極電流會(huì)顯著上升。電流上升會(huì)導(dǎo)致功耗過大,并可能損壞MOSFET。

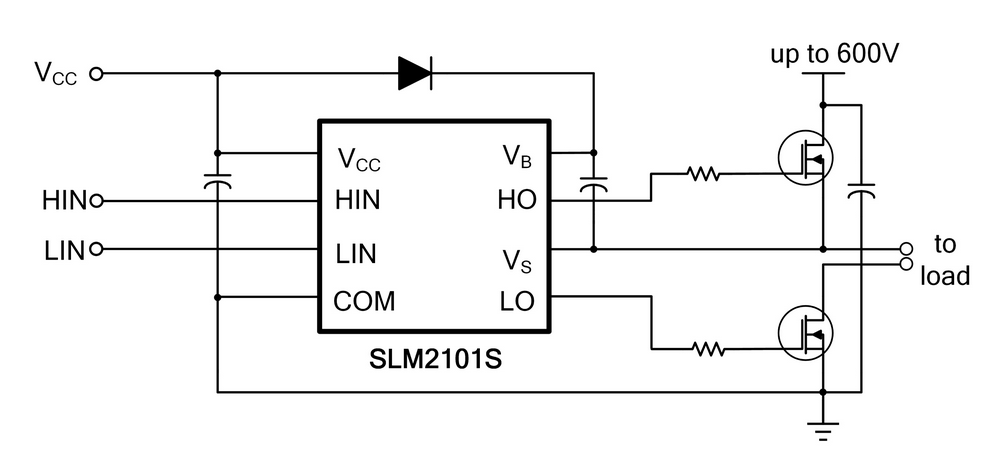

上海數(shù)明HVIC柵極驅(qū)動(dòng)器SLM2304S用于驅(qū)動(dòng)最高600V的N溝道MOSFET或IGBT,兼容IR2304(S)系列,廣泛應(yīng)用于BLDC,大功率DC-DC電源,家電,步進(jìn)驅(qū)動(dòng)器,逆變器等領(lǐng)域。

VS腳?產(chǎn)負(fù)壓的原因和對(duì)策

VS腳生產(chǎn)負(fù)壓的原因

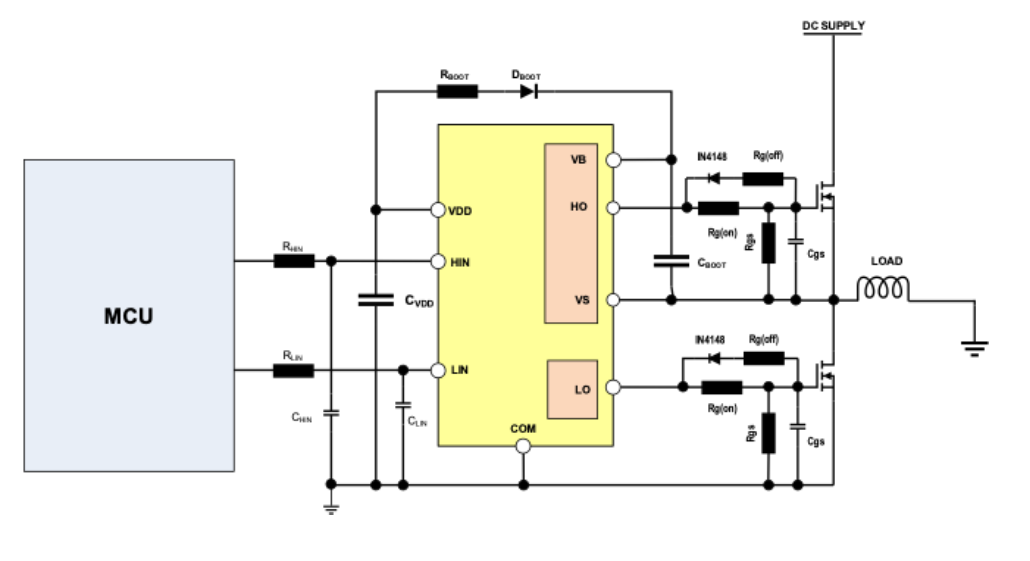

自舉式電源是一種應(yīng)用廣泛,給高邊柵極驅(qū)動(dòng)電路供電的方法,用來驅(qū)動(dòng)高邊N溝道的MOS 或者IGBT。自舉式電源技術(shù)具有結(jié)構(gòu)簡單,成本低的優(yōu)點(diǎn),但也存在缺點(diǎn),其一是占空比無 法做到100%,受到自舉電容刷新電荷所需時(shí)間,VBS欠壓保護(hù)閾值的限制,其二是會(huì)導(dǎo)致 開關(guān)器件的源極看到負(fù)壓,可能導(dǎo)致HVIC的輸出錯(cuò)誤。

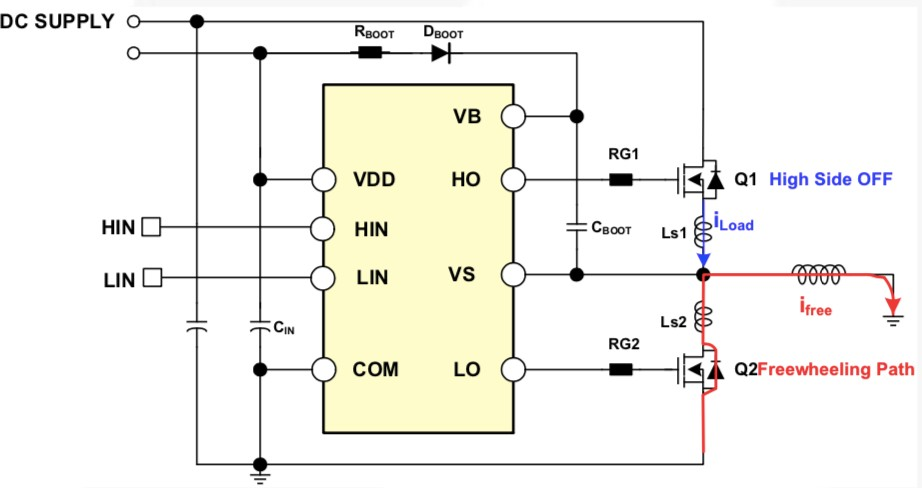

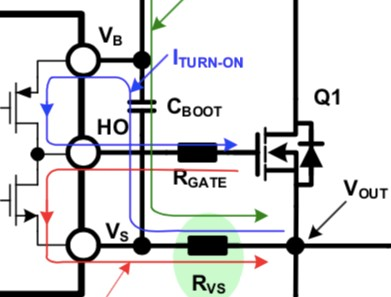

自舉式驅(qū)動(dòng)電路最大的難點(diǎn)在于:當(dāng)開關(guān)器件關(guān)斷時(shí),其源極 的負(fù)電壓會(huì)使負(fù)載電流突然流過續(xù)流二極管,如圖 1所示。該負(fù)電壓會(huì)給柵極驅(qū)動(dòng)電路的輸出端造成麻煩,因?yàn)樗苯佑绊戲?qū)動(dòng)電路或 PWM 控制集成電路的源極 VS 引腳,可能會(huì)明顯地將某些內(nèi)部電壓下拉到地以下,如圖 2所示。另外一個(gè)問題是,自舉電容 CBOOT,通過自舉二極管 DBOOT, 被電源 VDD 瞬間充電。由于 VDD 電源以地作為基準(zhǔn),自舉電容產(chǎn)生的最大電壓等于VDD 加上源極上的負(fù)電壓振幅,可能會(huì)使自舉 電容處于過壓狀態(tài),會(huì)有打壞電容甚至導(dǎo)致芯片VB/HO被打壞,短路到VS的風(fēng)險(xiǎn)。所以設(shè)計(jì)中應(yīng)盡量減小VS的負(fù)壓。

圖1 半橋應(yīng)用電路

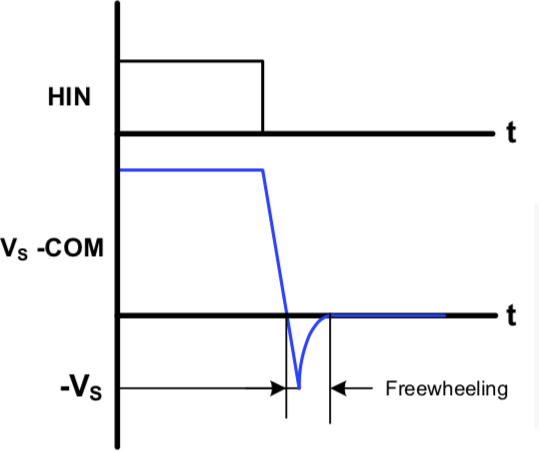

圖 2 關(guān)斷期間的 VS 波形

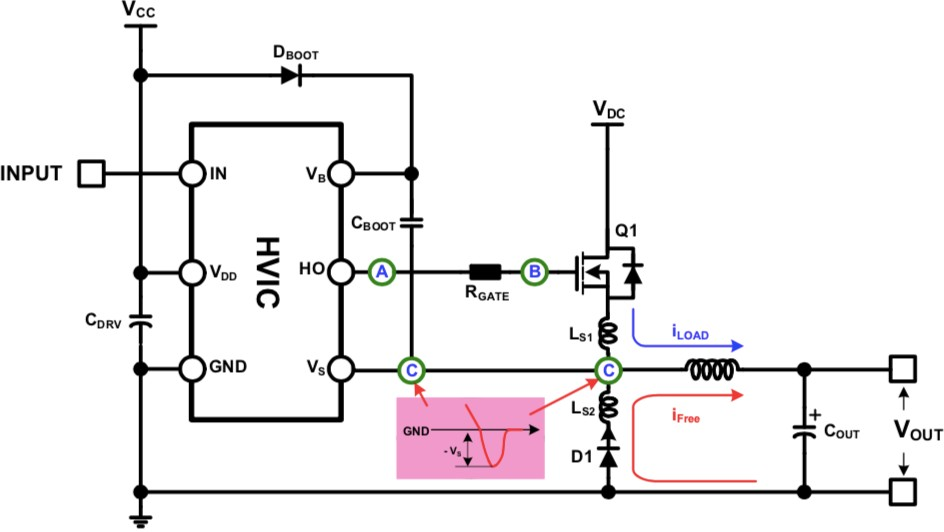

圖 3 DC-DC 電源

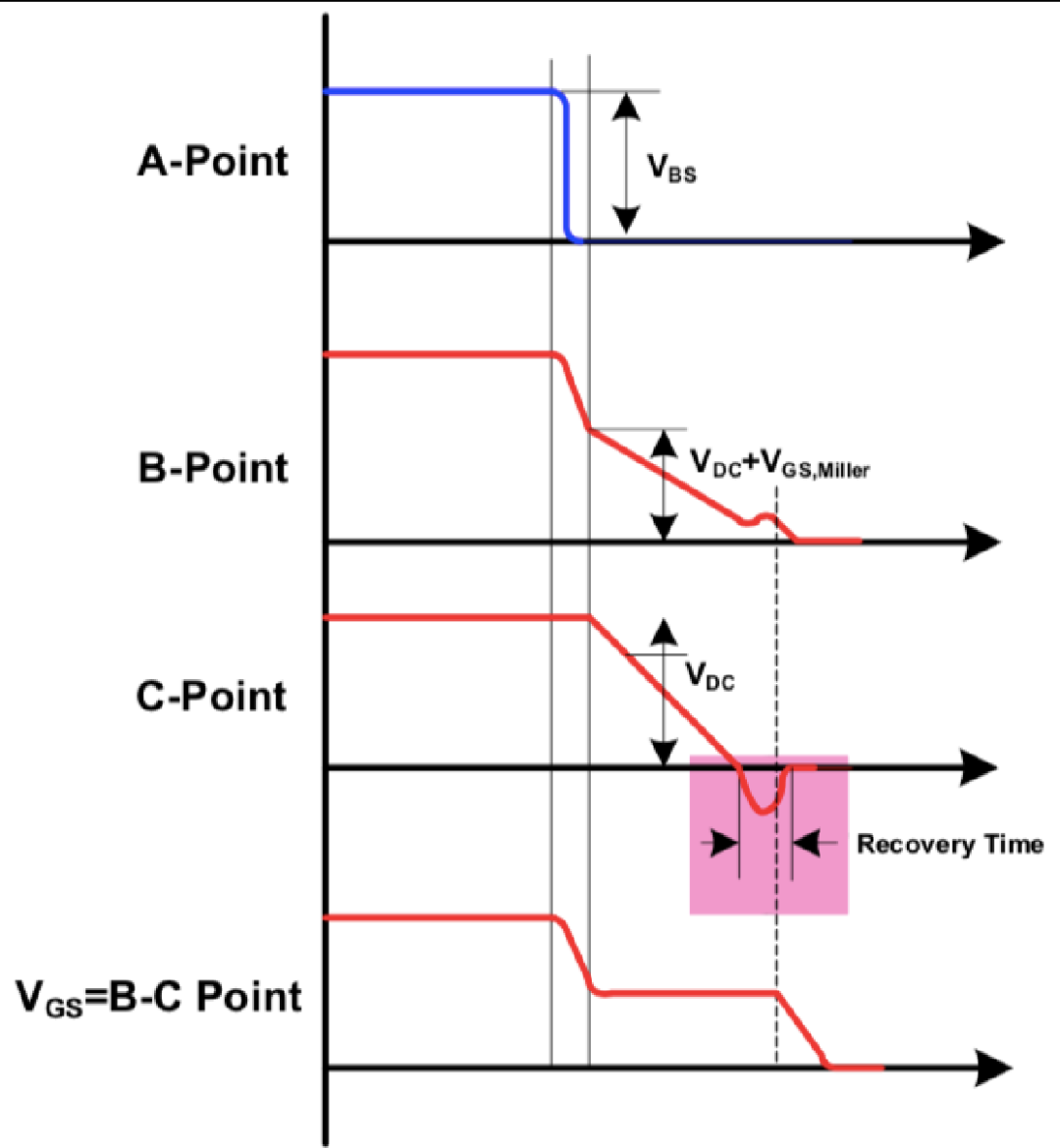

圖 4 關(guān)斷期間的波形

如圖 3 所示,低邊續(xù)流二極管的前向偏置是已知的將 VS 下拉到 COM(地) 以下的原因之一;圖 4 描述了高邊 N 溝道 MOSFET 關(guān)斷期間的電壓波形。主要問題出現(xiàn)在整流器換向期間,僅僅在續(xù)流二極管開始箝壓之前。在這種情況下,電感 LS1 和 LS2 會(huì)將 VS 電壓壓低到 COM 以下,該負(fù)電壓的振幅是:

VS?COM=?(VRBOOT +VFDBOOT)?(LS1+LS2)di/dt

(1)

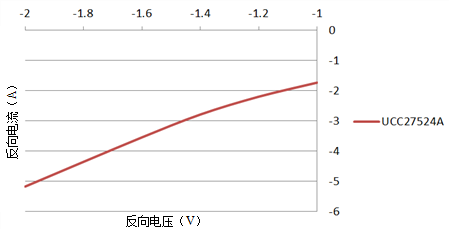

從等式(1)可以看到,該負(fù)電壓的放大倍數(shù)正比于寄生電感和開關(guān)器件的關(guān)斷 速度, di/dt ;它由柵極驅(qū)動(dòng)電阻, RGATE 和開關(guān)器件的輸入電容,Ciss 決定。Ciss 是 Cgs 與Cgd 的和,稱為米勒電容。

如何降低 VS 負(fù)壓?

? layout 上減小寄生電感 LS1/LS2

? 降低開關(guān)器件的開關(guān)速度

? 在開關(guān)節(jié)點(diǎn)串一個(gè)小電阻,如下圖中的 RVS 電阻(幾歐姆以內(nèi)),接自舉電容后再到,和自舉電容形成 RC 濾波,可以限制 VS 腳的下沖電壓。不過需要注意這個(gè)電阻串在開關(guān)器件開啟和關(guān)閉的路徑上,計(jì)算門級(jí)電阻時(shí)需要考慮此阻值

? 如在 VS 串電阻后仍不足以限制 VS 負(fù)壓,則可以在靠近 SLM2304S 芯片的 COM 和 VS腳之間并聯(lián)一個(gè)快恢復(fù)二極管,朝向 VS,來鉗位 VS 的負(fù)壓

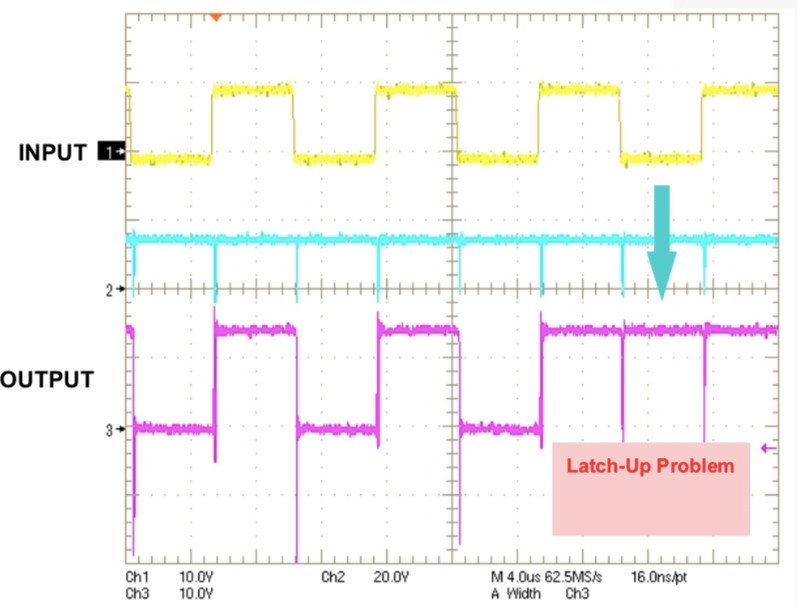

圖 5 閉鎖情況下的波輸入輸出形

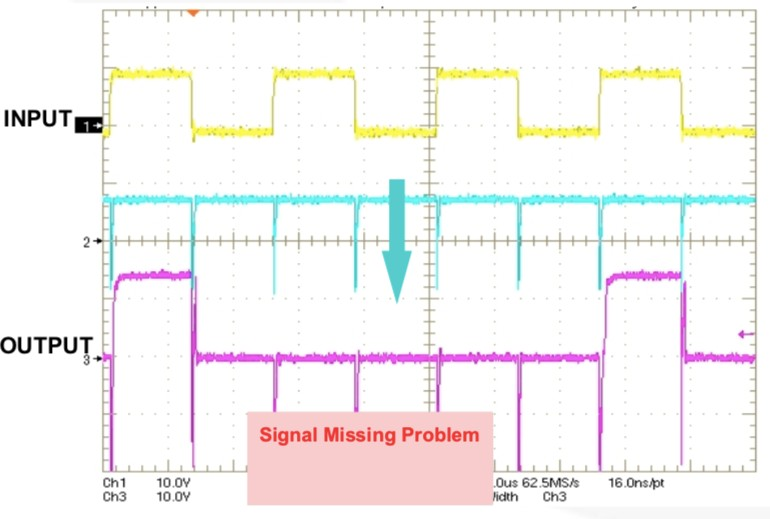

如果 VS 下沖超過規(guī)格書中標(biāo)稱的規(guī)格,則柵極驅(qū)動(dòng) IC 將損壞,或者高邊輸出暫時(shí)無法對(duì)輸入轉(zhuǎn)換做出響應(yīng),如圖 5 和圖 6 所示。建議設(shè)計(jì)中留一定余量,保證系統(tǒng)的可靠性。圖 5 顯示閉鎖情況,即高邊輸出無法通過輸入信號(hào)改變。這種情況下,半橋拓?fù)涞耐獠俊⒅麟娫础⒏哌吅偷瓦呴_ 關(guān)中發(fā)生短路。圖 6 顯示遺漏情況,即高邊輸出無法對(duì)輸入轉(zhuǎn)換做出響應(yīng)。這種情況下,高邊柵極驅(qū)動(dòng)器的電平轉(zhuǎn)換器將缺少工作電壓余量。需要注 意的是,大多數(shù)事實(shí)證明高邊通常不需要在一個(gè)開關(guān)動(dòng)作之后立即改變狀態(tài)。

圖 6 信號(hào)丟失情況下的波形

自舉電路的設(shè)計(jì)

選擇自舉電容值

自舉電容 (CBOOT) 每次都被充電,此時(shí),低邊驅(qū)動(dòng)器導(dǎo)通,輸出電壓略低于柵極驅(qū)動(dòng)器的電源電壓 (VDD)。自舉電容僅當(dāng)高邊開關(guān)導(dǎo)通的時(shí)候放電。自舉電容給高邊電路提供電源(VBS),首先要考慮的參數(shù)是高邊開關(guān)處于導(dǎo)通 時(shí),自舉電容的最大電壓降。允許的最大電壓降 (VBOOT) 取決于要保持的最小柵極驅(qū)動(dòng)電壓 ( 對(duì)于高邊開關(guān) )。如 果 VGSMIN 是最小的柵 - 源極電壓,電容的電壓降必須是:

ΔVBOOT = VDD ? VF ? VGSMIN

(2)

其中:

VDD= 柵極驅(qū)動(dòng)器的電源電壓

VF=自舉二極管正向電壓降計(jì)算自舉電容為:

CBOOT=QTOTAL/ΔVBOOT

(3)

其中 QTOTAL 是電容器的電荷總量。自舉電容的電荷總量通過等式 4 計(jì)算:

QTOTAL=QGATE+(ILKCAP+ILKGS+IQBS+ILK+ILKDIODE)*tON+QLS

(4)

其中:

QGATE = 柵極電荷的總量

ILKGS = 開關(guān)柵 - 源級(jí)漏電流

ILKCAP = 自舉電容的漏電流

IQBS =自舉電路的靜態(tài)電流

ILK = 自舉電路的漏電流

QLS= 內(nèi)部電平轉(zhuǎn)換器所需要的電荷,對(duì)于所有的高壓 柵極驅(qū)動(dòng)電路

tON = 高邊導(dǎo)通時(shí)間

ILKDIODED = 自舉二極管的漏電流

另外一般的,可以根據(jù)經(jīng)驗(yàn)公式粗略估算自舉電容值:

CBOOT>10*Ciss

選擇自舉電阻值

自舉電阻起到限制自舉電容充電電流的作用,可防止電容過充,特別在一些 VS 負(fù)壓較大的情況下,能降低 VS-VB 以及電容過壓的風(fēng)險(xiǎn)。該電阻典型值 5~10ohm,會(huì)增加 VBS 時(shí)間常數(shù)。當(dāng)計(jì)算最大允許的電壓降 (VBOOT) 時(shí),必須考慮該自舉電阻引入的電壓降。如果該電壓降太大或電路不能提 供足夠的充電時(shí)間,我們可以使用一個(gè)快速恢復(fù)或超快恢復(fù)二極管。

自舉二極管的選擇

在高邊器件開通時(shí),自舉二極管必須能夠阻止高壓,并且應(yīng)是快恢復(fù)或超快恢復(fù)二極管,以 減小從自舉電容向電源VCC的回饋電荷。如果電容需要長期貯存電荷時(shí),高溫反向漏電流指 標(biāo)也很重要。一般建議自舉二極管的反向耐壓值和所選MOS/IGBT的電壓規(guī)格一致, trr<100ns.

VDD供電

VDD電壓一般在12~15V左右,輸入電容要靠近芯片VDD和COM腳。一般輸入電容配置為一 個(gè)電解(10~100uF)+100nF瓷片電容,電解電容提供能量,100nF瓷片濾波,吸收可能的 電壓尖峰。

邏輯輸入

一般的,邏輯輸入腳可以直接連接前級(jí)控制器的輸出。但如空間允許,或應(yīng)用環(huán)境干擾大且邏輯輸入高電平比較低(如3.3V),還是建議在邏輯輸入前加RC濾波,電阻串在控制器輸出和邏輯輸入之間,邏輯輸入腳對(duì)地并一個(gè)電容,如100R,100pF。

另外,需要注意一些MCU或者軟件中,如果輸入控制器只輸出高電平以及高阻態(tài),低電平需 要靠HIN/LIN內(nèi)部的下拉電阻來實(shí)現(xiàn),則建議在HIN/LIN預(yù)留一個(gè)下拉電阻的位置。因SLM2304S HIN/LIN內(nèi)部下拉電阻為500K歐姆左右,在一些噪聲干擾比較大的應(yīng)用中,可能出現(xiàn)HIN/LIN被誤觸發(fā)高電平的情況,此時(shí)外部加一個(gè)10K以內(nèi)的下拉電阻即可解決。

門級(jí)電阻值的選取

門級(jí)電阻在柵極驅(qū)動(dòng)路徑上會(huì)影響真實(shí)的驅(qū)動(dòng)電流,開關(guān)損耗以及上升/下降沿,合適的阻值可以有效限制降低噪聲和振鈴,避免EMI問題。理論上,驅(qū)動(dòng)輸出可以直接和開關(guān)器件的gate直接連接,但如果沒有選取一個(gè)合適的門級(jí)電阻值,由于layout和和器件本身的寄生電 感,電容,高速的dv/dt,di/dt,體二極管的反向恢復(fù)時(shí)間等因素,會(huì)導(dǎo)致驅(qū)動(dòng)電路面臨EMI, 以及高度dv/dt導(dǎo)致的共通等問題。

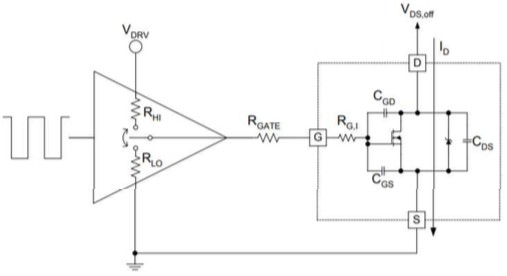

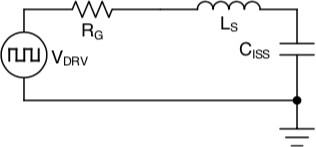

圖7

圖8

圖7,圖8兩圖分別為驅(qū)動(dòng)電路元件示意圖以及等效電路圖,門級(jí)電阻值RGATE可以通過如下 步驟計(jì)算:

LS=1/[CISS*(2pifR)2]

(6)

RG=XL/Q=w*LS/Q=1/(CISS*2*pi*fR*Q)

(7)

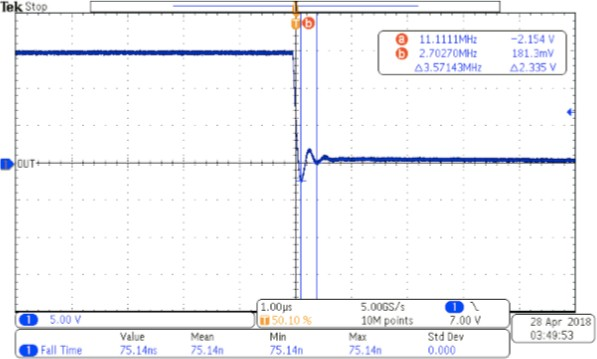

LS是柵極驅(qū)動(dòng)線路上的寄生電感Ciss=CGS+CGD,規(guī)格書可查fR 是 RGATE=0 時(shí) 實(shí) 測(cè) 出 來 的 VS 振 鈴 頻 率 , 如 下 示 意 圖 9,fR 測(cè) 得 為 3.75MHz RG=RGATE+ROH or LO+RG,I,ROH or LO是HVIC輸出級(jí)上拉/下拉電阻值,規(guī)格書可以查, RG,I是開關(guān)器件內(nèi)寄生的柵極網(wǎng)狀電阻,一般在~1歐姆左右,較小可忽略,部分規(guī)格書中沒有提到此參數(shù)Q是諧振電路中的Q值,一般取值0.5~1之間,Q越小,RGATE越大,柵極電壓上升/下降越 慢根據(jù)等式7,即可算出理論上的RGATE,但一般實(shí)際情況中,還需要在開關(guān)速度,開關(guān)器件 溫度,dv/dt,EMI等因素上折中,再確定合適的門級(jí)電阻值。

圖9 RGATE=0R

快關(guān)電路

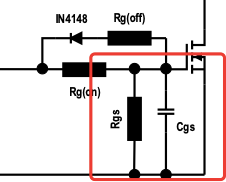

如下圖,如希望快速關(guān)斷來提升效率,或擔(dān)心關(guān)斷太慢導(dǎo)致共通,則可以在輸出門級(jí)電阻并 一個(gè)開關(guān)二極管+一個(gè)電阻的路徑,來提高關(guān)斷速度,此時(shí)關(guān)斷速度由二極管的反向恢復(fù) 時(shí)間決定,還可通過Rg(off)來調(diào)整關(guān)斷速度。

Rgs和Cgs的作?

Rgs一般選10K阻值,用作電荷泄放路徑,防止未工作時(shí)開關(guān)器件GS之間電荷累計(jì)導(dǎo)致VGS過壓,打壞器件。Cgs一般可作預(yù)留,非必要器件,主要用來降低Cgd/Cgs比例,防止開關(guān)過程中的米勒效應(yīng) 導(dǎo)致gate被Cgd耦合起來,半橋開關(guān)器件共通,鉗住gate電壓。該電容若需要的話,典型值 一般在1~2.2nF,注意如果太大會(huì)導(dǎo)致開關(guān)器件開啟慢,開關(guān)損耗大,器件溫度變高。

PCB 布局?線建議

考慮所有功率開關(guān)的配合放置,減少驅(qū)動(dòng)輸出線路以及開關(guān)器件電流路徑,走線長度CVDD/CBOOT 去耦電容和柵極電阻的布局和布線,應(yīng)盡可能靠近驅(qū)動(dòng)芯片管腳避免互連鏈路。它會(huì)顯著增加電 降低封裝體距離 PCB 板的高度,以減少引腳電感效應(yīng)自舉二極管應(yīng)盡可能靠近自舉。

SLM2304S有兩路輸入,HIN和LIN,分別控制高邊輸出HO以及低邊輸出LO。HIN和HO同相 位,LIN和LO同相位。為防止輸入控制出錯(cuò),例如輸入同為高,輸出也同為高,從而導(dǎo)致MOS/IGBT共通的情況,SLM2304S采用了互鎖設(shè)計(jì),即當(dāng)兩路輸入均為高時(shí),輸出均為低, 確保輸出端的安全。當(dāng)然,如果客戶的應(yīng)用就是需要輸出HO和LO同為高的情況,我們推薦 去掉了互鎖功能的SLM2106B來滿足這類特殊的應(yīng)用。

-

微控制器

+關(guān)注

關(guān)注

48文章

7552瀏覽量

151406 -

晶體管

+關(guān)注

關(guān)注

77文章

9690瀏覽量

138167 -

柵極驅(qū)動(dòng)器

+關(guān)注

關(guān)注

8文章

743瀏覽量

38985

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

柵極驅(qū)動(dòng)器是什么,為何需要柵極驅(qū)動(dòng)器?

柵極驅(qū)動(dòng)器是什么

了解您的柵極驅(qū)動(dòng)器

使用隔離式柵極驅(qū)動(dòng)器的實(shí)用設(shè)計(jì)指南

柵極驅(qū)動(dòng)器電流多少正常啊,柵極驅(qū)動(dòng)器電流怎么計(jì)算

柵極驅(qū)動(dòng)器芯片有哪些作用

柵極驅(qū)動(dòng)器芯片的原理是什么

柵極驅(qū)動(dòng)器的選型標(biāo)準(zhǔn)是什么

隔離式柵極驅(qū)動(dòng)器的影響

什么是柵極驅(qū)動(dòng)器?柵極驅(qū)動(dòng)器的工作原理

技術(shù)分享 柵極驅(qū)動(dòng)器及其應(yīng)用介紹

了解智能柵極驅(qū)動(dòng)器

柵極驅(qū)動(dòng)器的原理及應(yīng)用

柵極驅(qū)動(dòng)器的原理及應(yīng)用

評(píng)論