為你的FPGA設(shè)計(jì)加加速,NIC、Router、Switch任意實(shí)現(xiàn)

副標(biāo)題:優(yōu)秀的IC/FPGA開源項(xiàng)目(二)-NetFPGA

《優(yōu)秀的IC/FPGA開源項(xiàng)目》是新開的系列,旨在介紹單一項(xiàng)目,會(huì)比《優(yōu)秀的 Verilog/FPGA開源項(xiàng)目》內(nèi)容介紹更加詳細(xì),包括但不限于綜合、上板測試等。兩者相輔相成,互補(bǔ)互充~

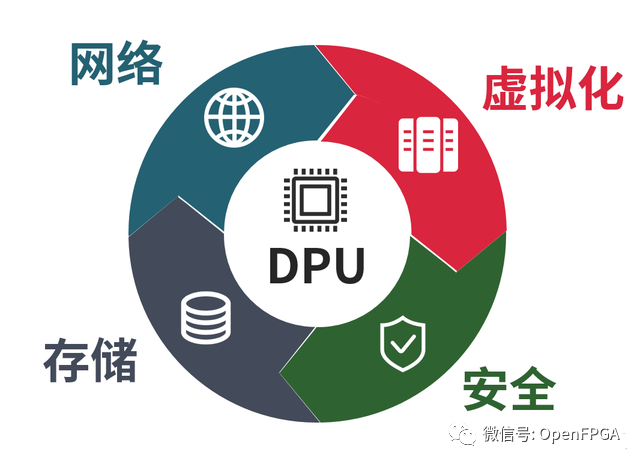

這幾年DPU的概念越來越火,有和CPU、GPU并駕齊驅(qū)的勢頭,通俗的講DPU分擔(dān)的工作為虛擬化、網(wǎng)絡(luò)、存儲(chǔ)以及安全。

從上面的工作可以看出DPU的核心是:網(wǎng)絡(luò)。所以我們今天講一個(gè)未來的發(fā)展核心之一:用FPGA實(shí)現(xiàn)NIC(network interface controller,網(wǎng)絡(luò)接口控制器),從該項(xiàng)目出發(fā)可以實(shí)現(xiàn)數(shù)據(jù)可控制化,進(jìn)而實(shí)現(xiàn)DPU功能。

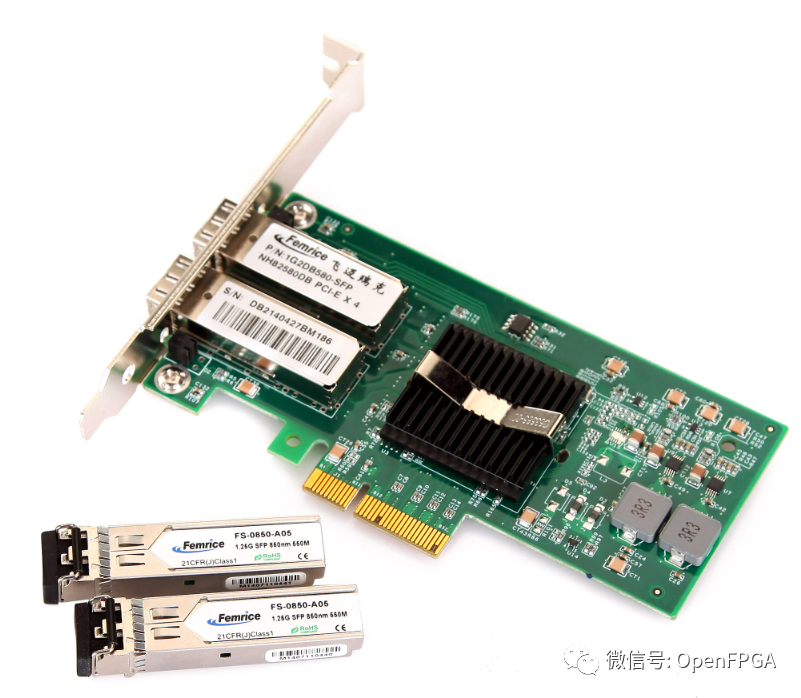

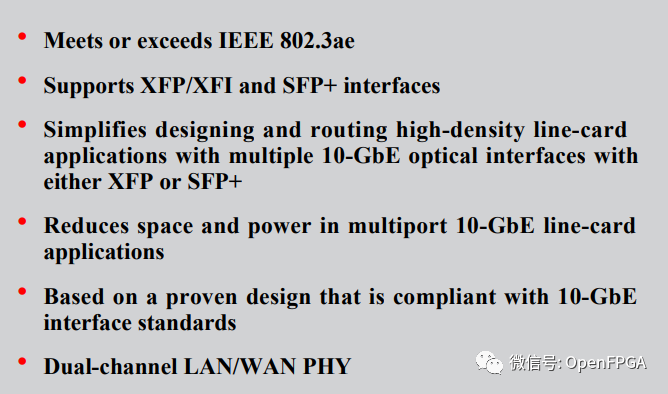

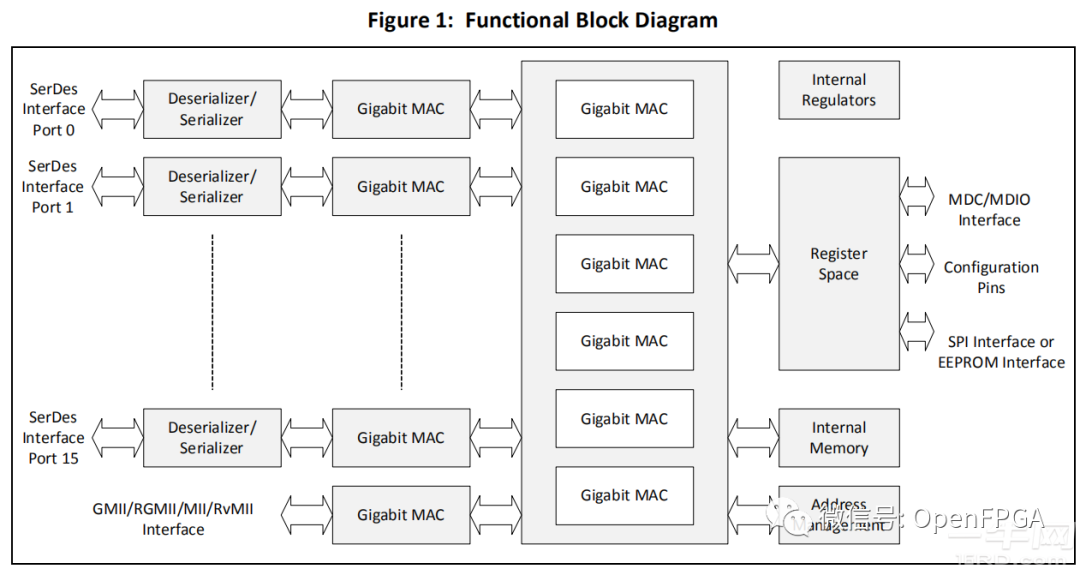

當(dāng)然,本項(xiàng)目的基本就是一個(gè)NIC、router、switch等子項(xiàng)目的集合,可以看做目前ASIC-Intel 82580、BCM8724、BCM5396的功能的FPGA實(shí)現(xiàn)。

基于Intel 82580網(wǎng)卡

BCM8724特點(diǎn)

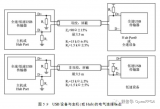

BCM5396內(nèi)部架構(gòu)圖

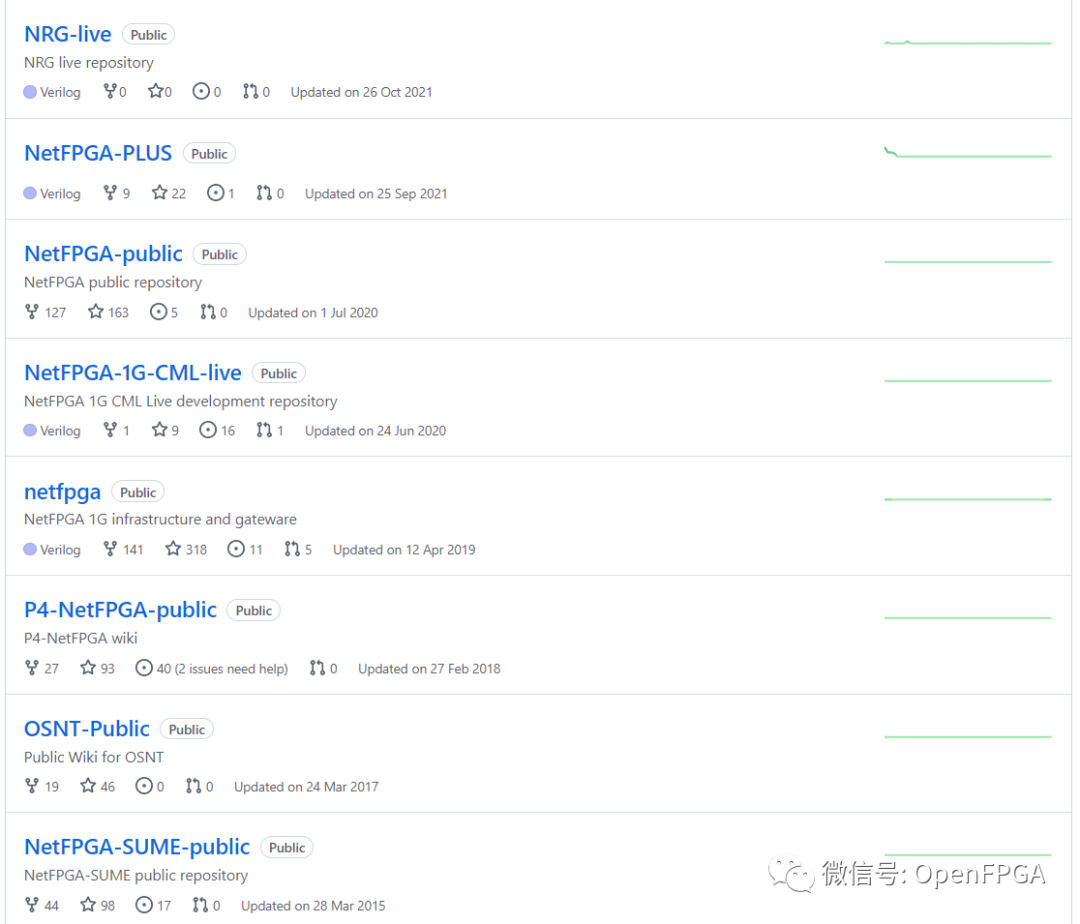

今天項(xiàng)目的核心項(xiàng)目地址如下:

https://github.com/NetFPGA

www.netfpga.org

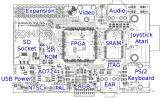

這個(gè)項(xiàng)目已經(jīng)發(fā)展了很多年了,從V5 FPGA到現(xiàn)在V7 FPGA,從官方板卡到各種自制板卡,應(yīng)有盡有。

netfpga官方V7 板卡

核心的架構(gòu)都可以在上面的板卡上實(shí)現(xiàn)。

整個(gè)項(xiàng)目包括如下幾個(gè)平臺(tái)的子項(xiàng)目:

上面的項(xiàng)目是根據(jù)不同板卡實(shí)現(xiàn)的功能類似的項(xiàng)目。

接下來我們以AMD Xilinx VC709位核心,簡單說明一下怎么移植NetFPGA到我們的板卡上,本次實(shí)現(xiàn)的參考項(xiàng)目為NetFPGA-SUME(架構(gòu)類似)。

NetFPGA移植

開發(fā)環(huán)境:

win10+Ubuntu虛擬機(jī)

vivado 2016.4

第一步在下面鏈接下載源碼:

https://github.com/junganghu/NetFPGA-SUME-live

可以使用下面命令:

gitclonehttps://github.com/junganghu/NetFPGA-SUME-live

PS:是不是覺得奇怪,為啥不是官方源碼?這是因?yàn)楣俜綆焓撬接袔欤枰ㄟ^官網(wǎng)申請,上面鏈接應(yīng)該源開發(fā)者上傳的,能使用。

第二步修改/NetFPGA-SUME-live/tools/settings.sh:

主要修改一些路徑,方便調(diào)用工具,主要修改SUME_FOLDER(庫的路徑)、XILINX_PATH(vivado的安裝路徑)、NF_PROJECT_NAME(測試的demo,可選nic,route,swich)

進(jìn)入$SUME_FOLDER(庫的路徑)執(zhí)行:

make

如果使用上面的版本vivado,應(yīng)該不會(huì)出什么問題,其他版本需要修改tcl里的IP版本(出錯(cuò)命令行會(huì)詳細(xì)提示問題,按照提示修改即可,但是IP間的差異會(huì)導(dǎo)致綜合失敗,建議先按照源vivado版本編譯,后續(xù)GUI界面再修改)。

上面步驟時(shí)間較久,根據(jù)電腦性能需要一個(gè)小時(shí)左右。

第三步進(jìn)入Reference_nic目錄再次執(zhí)行下面命令:

make

就會(huì)生成reference_nic.bit

PS:SDK部分官方提供了源碼,可以自己新建SDK工程,把源碼拷貝進(jìn)去也是可以的。

第四步固化文件到FPGA。

第五步就是將板卡插到測試主板上,在主板主控上加載驅(qū)動(dòng)。

第六步加載驅(qū)動(dòng)(驅(qū)動(dòng)源文件在DRIVER_FOLDER目錄下,執(zhí)行

makeall makemakeinstall

修改驅(qū)動(dòng)文件權(quán)限。

接下來:

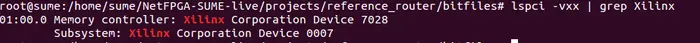

lcpsi-vxx|grepXilinx

查找系統(tǒng)有沒有找到PCIe設(shè)備,正常會(huì)出現(xiàn)下面:

注意ID:7028 0007,如果不是證明FPGA下載的文件有問題。

載入sume_riffa模塊

modprobesume_riffa

查看有沒有加載成功

lsmod

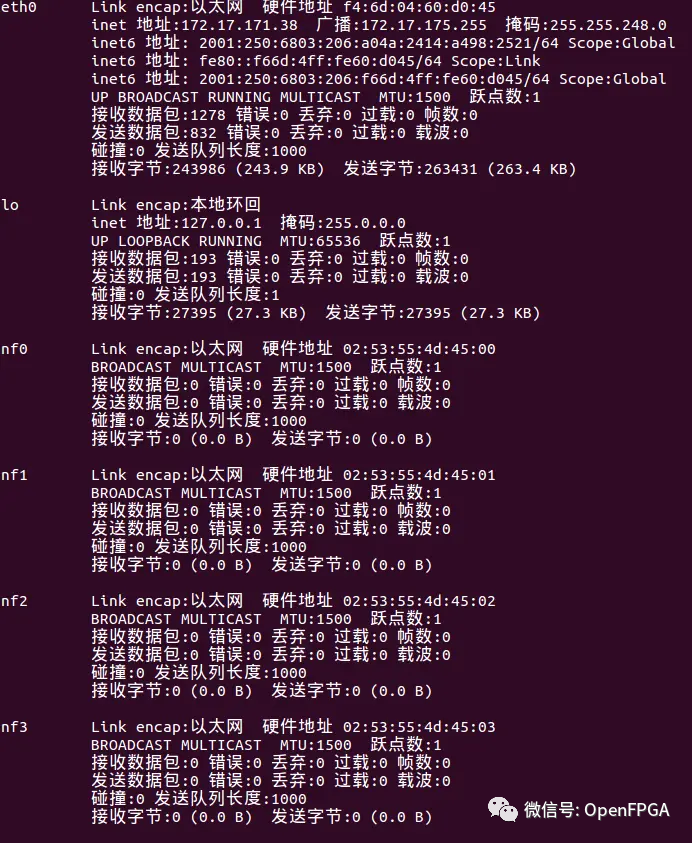

查看有沒有識(shí)別到網(wǎng)卡:

ifconfig-a

接下來就按照自己需求進(jìn)行測試了。

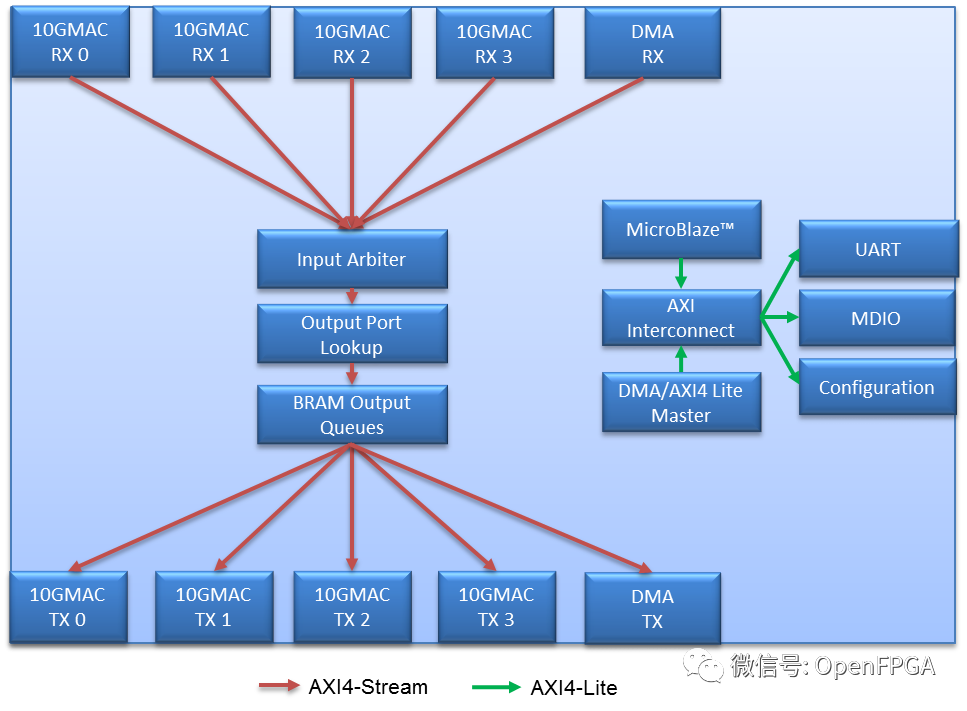

最后總結(jié)一下這個(gè)架構(gòu):

sume_riffa的這個(gè)nic架構(gòu)PCIe部分使用了基于Scatter-Gather DMA的riffa PCIe開源模塊,其他IP基本都是xilinx官方IP,使用AXI-stream和AXI-lite的比較廣泛的架構(gòu),值得學(xué)習(xí)。

總結(jié)

今天的項(xiàng)目簡單優(yōu)化后基本就可以應(yīng)用到項(xiàng)目里了,開頭說的可能比較“繞”,簡單說就是如果你想用FPGA實(shí)現(xiàn)網(wǎng)絡(luò)相關(guān)的功能(包括但不局限于NIC、Route、Swich、OSNT等),那么你就可以到這個(gè)項(xiàng)目里找一個(gè)相接近的子項(xiàng)目移植即可,這樣這個(gè)項(xiàng)目的功能就清晰明了了。

最后說一下,項(xiàng)目整體移植非常非常簡單,幾天時(shí)間就能讓你快速實(shí)現(xiàn)一個(gè)網(wǎng)絡(luò)相關(guān)項(xiàng)目的功能驗(yàn)證,同時(shí)這個(gè)該項(xiàng)目的架構(gòu)也是比較先進(jìn)的,也是值得學(xué)習(xí)的。還想什么?動(dòng)手干吧~

最后,還是感謝各個(gè)大佬開源的項(xiàng)目,讓我們受益匪淺。后面如果大家想要分享什么項(xiàng)目,可以在后臺(tái)留言或者加微信留言,溝通轉(zhuǎn)載事宜。今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603432 -

asic

+關(guān)注

關(guān)注

34文章

1200瀏覽量

120507 -

cpu

+關(guān)注

關(guān)注

68文章

10863瀏覽量

211786

原文標(biāo)題:總結(jié)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

關(guān)于FPGA項(xiàng)目外包

購買NetFPGA SUME板后,我可以獲得Vivado許可嗎?

NetFPGA主要組成部分有什么?

NetFPGA-SUME開發(fā)板測試時(shí)顯示回送測試失敗

為你的FPGA設(shè)計(jì)加加速,NIC、Router、Switch任意實(shí)現(xiàn)

基于Xilinx FPGA的HDUSec-網(wǎng)絡(luò)行為分析監(jiān)控系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)(含源代碼)

優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(一)

優(yōu)秀的 Verilog/FPGA開源項(xiàng)目之 USB通信

Verilog/FPGA開源項(xiàng)目介紹

TTL FPGA開源項(xiàng)目

使用FPGA做的開源示波器

關(guān)于FPGA的開源項(xiàng)目介紹

優(yōu)秀的IC/FPGA開源項(xiàng)目(二)-NetFPGA

優(yōu)秀的IC/FPGA開源項(xiàng)目(二)-NetFPGA

評(píng)論