驗證生產力的關鍵之一是在一個合適的抽象級別上考慮驗證問題。也就是說,在驗證DUT時應該創建一個支持適當抽象級別的驗證環境。雖然DUT實際接口都是信號級的,但有必要在transaction level管理絕大多數的驗證任務,如激勵生成、功能比對和覆蓋率收集等。

UVM提供了一組transaction level通信接口,你可以使用它們來連接transaction level的組件。TLM接口的使用將每個驗證組件與驗證環境中其他組件隔離開。TLM+factory機制通過支持組件替換來促進重用,因為替換前和替換后的驗證組件具有相同的接口。

TLM還允許UVM驗證環境與驗證開發的transaction-levelmodel進行組合(而不是DUT本身)。

例如可以用驗證開發的model1(functional model)去驗證model2(cycle-accuratemodel),也可以同時使用model1+model2驗證DUT。model1和model2分別是在不同階段以不同精細度對RTL的建模。在前期可以通過驗證環境+model1+model2,保證驗證環境的穩定,等到RTL ready后使用model1和model2驗證RTL,快速實現驗證收斂。當然,這其中同樣存在著transaction-level和pin-level轉換的事情要去做。

組件之間定義清晰的TLM接口語義也為實現mixed-language驗證環境提供了支持。此外,可以理解任何帶有TLM接口的驗證組件(verification components)都可以非常方便地集成到已有的驗證環境。

?

審核編輯:理清

-

RTL

+關注

關注

1文章

385瀏覽量

59853 -

UVM

+關注

關注

0文章

182瀏覽量

19189 -

TLM

+關注

關注

1文章

32瀏覽量

24761 -

DUT

+關注

關注

0文章

189瀏覽量

12423

原文標題:UVM Transaction-Level Modeling (TLM)概述

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

談談UVM中的uvm_info打印

Modeling and Implementation of

Modeling and Implementation of

TLM通信中常用的術語

UVM sequence機制中response的簡單使用

為什么不是uvm_transaction構建UVM事務呢?

典型的UVM Testbench架構

UVM Transaction-Level Modeling (TLM)介紹

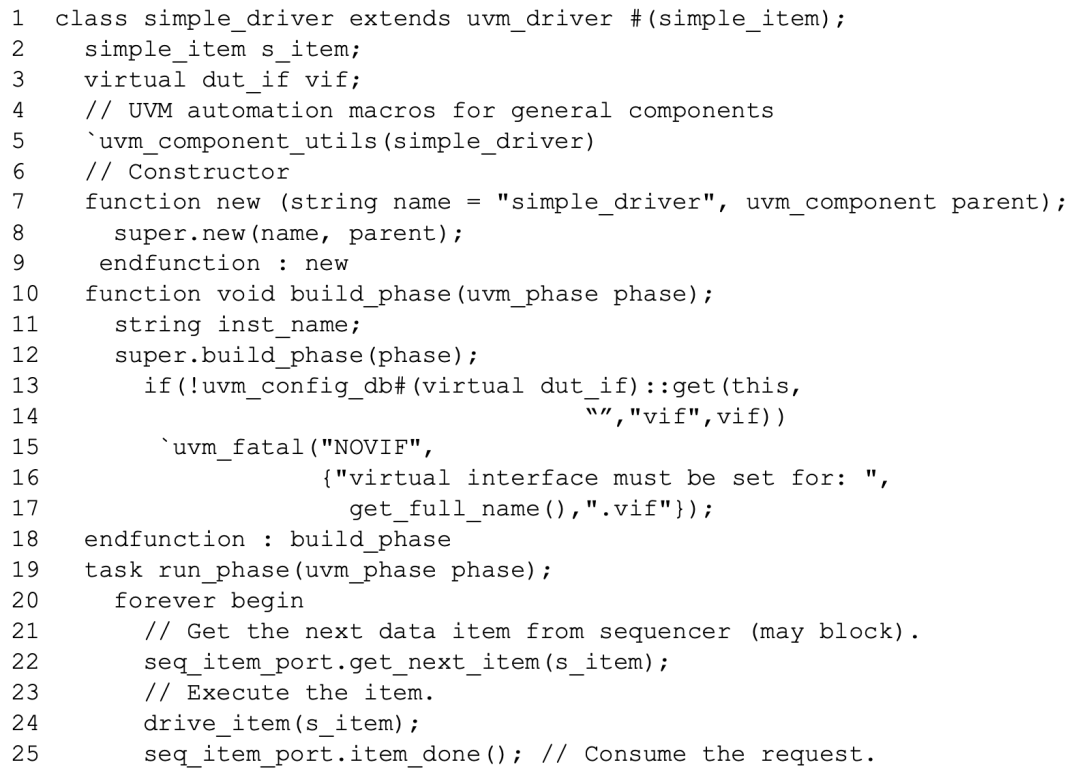

創建UVM Driver

數字IC驗證之基本的TLM通信

UVM Transaction-Level Modeling (TLM)概述

UVM Transaction-Level Modeling (TLM)概述

評論