作者:Rahul Singhal 和 Giri Podichetty

部署在汽車(chē)、醫(yī)療和航空航天等安全關(guān)鍵應(yīng)用中的集成電路 (IC) 或芯片的運(yùn)行故障可能會(huì)產(chǎn)生災(zāi)難性后果。這些故障可能源于芯片中逃脫制造測(cè)試的缺陷,或者由于操作環(huán)境等因素在系統(tǒng)運(yùn)行期間可能發(fā)生的暫時(shí)性故障。為了避免此類故障,這些IC需要最高質(zhì)量的制造測(cè)試,以實(shí)現(xiàn)低于百萬(wàn)分之一(DPPM)的缺陷率和系統(tǒng)內(nèi)測(cè)試功能,以確保芯片在ISO 26262標(biāo)準(zhǔn)定義的系統(tǒng)運(yùn)行期間的安全功能。IC設(shè)計(jì)人員通常基于高級(jí)故障模型(如單元感知、路徑延遲、轉(zhuǎn)換等)生成掃描測(cè)試模式。以滿足 激進(jìn) 的 測(cè)試 質(zhì)量 目標(biāo), 并 添加 可 測(cè)試 性 設(shè)計(jì) (DFT), 例如 邏輯 BIST 用于 系統(tǒng) 內(nèi) 測(cè)試。

邏輯BIST是系統(tǒng)內(nèi)測(cè)試的關(guān)鍵DFT組件,用于測(cè)試設(shè)計(jì)的非存儲(chǔ)器部分。與使用帶有掃描測(cè)試引腳的自動(dòng)測(cè)試設(shè)備(ATE)施加模式的掃描測(cè)試不同,邏輯BIST測(cè)試圖案是使用偽隨機(jī)碼型生成器(PRPG)在芯片上生成的,并且測(cè)試模式響應(yīng)使用多輸入移位寄存器(MISR)累積到簽名中。將MISR簽名與片內(nèi)或片外的預(yù)期簽名進(jìn)行比較,以確定測(cè)試通過(guò)/失敗狀態(tài)。除了要求高測(cè)試覆蓋率外,安全關(guān)鍵應(yīng)用中IC的在系統(tǒng)測(cè)試必須具有較短的測(cè)試時(shí)間,因?yàn)闇y(cè)試是在芯片的功能操作期間進(jìn)行的。影響邏輯BIST測(cè)試時(shí)間和測(cè)試覆蓋率的主要因素之一是設(shè)計(jì)中的路徑生成未知(即X)仿真值,因?yàn)閄會(huì)破壞在多個(gè)測(cè)試模式或測(cè)試間隔中累積的MISR特征。這會(huì)導(dǎo)致測(cè)試覆蓋率丟失或需要更多的測(cè)試模式來(lái)實(shí)現(xiàn)目標(biāo)測(cè)試覆蓋率,從而增加測(cè)試時(shí)間。標(biāo)準(zhǔn)邏輯BIST解決方案需要X-clean設(shè)計(jì)來(lái)避免此問(wèn)題。

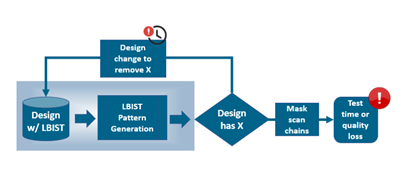

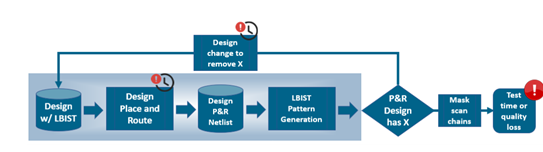

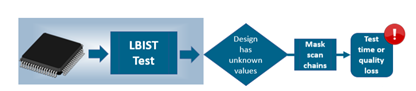

由于各種原因,X出現(xiàn)在設(shè)計(jì)開(kāi)發(fā)周期的不同階段,包括未建模的電路行為,缺少設(shè)計(jì)初始化以及靜態(tài)時(shí)序分析(STA)中未考慮的時(shí)序路徑。使用標(biāo)準(zhǔn)邏輯 BIST,設(shè)計(jì)人員遵循一種通過(guò)設(shè)計(jì)更改或通過(guò)在模式生成期間屏蔽掃描鏈來(lái)處理 X 的方法,以犧牲設(shè)計(jì)進(jìn)度或測(cè)試質(zhì)量為代價(jià)。為了在布局布線過(guò)程之前消除X,設(shè)計(jì)人員通常會(huì)選擇設(shè)計(jì)更改而不是屏蔽掃描鏈,因?yàn)樵诖穗A段設(shè)計(jì)更改的周轉(zhuǎn)時(shí)間很短(如圖1所示)。但是,在放置和路由過(guò)程之后,通常會(huì)在添加計(jì)時(shí)信息的情況下出現(xiàn)新的 X。這種情況如圖 2 所示,設(shè)計(jì)人員被迫在設(shè)計(jì)更改/重新旋轉(zhuǎn)導(dǎo)致的顯著延遲和鏈掩蔽導(dǎo)致的測(cè)試質(zhì)量降低之間做出權(quán)衡。未知的邏輯值對(duì)硅后提出了更嚴(yán)峻的挑戰(zhàn)。隨著當(dāng)今激進(jìn)的設(shè)計(jì)實(shí)踐和技術(shù)節(jié)點(diǎn),由于復(fù)雜的故障模型、時(shí)序邊際和工作參數(shù)變化等因素,幾乎不可能預(yù)測(cè)硅后出現(xiàn)的未知值。如圖3所示,在硅片中不可能進(jìn)行設(shè)計(jì)更改,唯一的選擇是通過(guò)屏蔽鏈來(lái)在測(cè)試覆蓋率和測(cè)試時(shí)間上妥協(xié)。由于這些因素,設(shè)計(jì)人員必須犧牲標(biāo)準(zhǔn)邏輯BIST的設(shè)計(jì)進(jìn)度或測(cè)試質(zhì)量。

圖 1:在布局布線過(guò)程之前消除 X 的設(shè)計(jì)流程。

圖 2:在布局布線過(guò)程后消除 X 的設(shè)計(jì)流程。

圖 3:在硅后設(shè)計(jì)中處理未知值的流程。

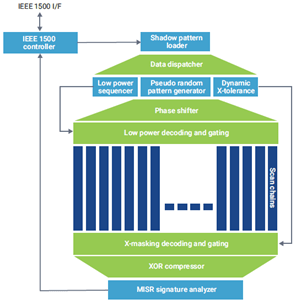

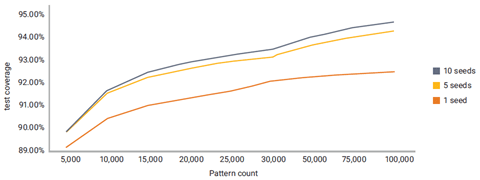

X容忍邏輯BIST(如TestMAX XLBIST)使設(shè)計(jì)人員能夠避免這些權(quán)衡,最大限度地減少Xs對(duì)整個(gè)鏈掩碼造成的測(cè)試質(zhì)量的影響,同時(shí)還消除了設(shè)計(jì)更改的需要。TestMAX XLBIST可以對(duì)包含Xs的掃描單元執(zhí)行動(dòng)態(tài)屏蔽,而不是屏蔽導(dǎo)致高測(cè)試覆蓋率損失的整個(gè)掃描鏈。 掃描單元掩碼允許鏈可觀察性,并在大多數(shù)場(chǎng)景中實(shí)現(xiàn)與X-clean設(shè)計(jì)相似的測(cè)試時(shí)間和覆蓋范圍,而無(wú)需相關(guān)的開(kāi)銷(xiāo)。TestMAX XLBIST 通過(guò)智能地使用其 PRPG 重新播種功能、動(dòng)態(tài) X 容忍解碼器和 X 掩碼解碼邏輯來(lái)實(shí)現(xiàn)測(cè)試目標(biāo)(如圖 4 所示)。圖 5 顯示了給定數(shù)量的模式種子的測(cè)試覆蓋率與模式計(jì)數(shù)的示例比較。

圖 4:TestMAX XLBIST 架構(gòu)。

圖5:TestMAX XLBIST通過(guò)多個(gè)種子實(shí)現(xiàn)了高覆蓋率。

除了測(cè)試時(shí)間和覆蓋范圍要求外,安全關(guān)鍵應(yīng)用中使用的IC還需要在其功能操作的不同階段進(jìn)行測(cè)試,以確保及早發(fā)現(xiàn)和減輕任何潛在缺陷及其影響。TestMAX XLBIST支持系統(tǒng)內(nèi)測(cè)試的三個(gè)主要階段:上電系統(tǒng)測(cè)試(POST),功能操作期間的測(cè)試和斷電系統(tǒng)測(cè)試。TestMAX XLBIST架構(gòu)還設(shè)計(jì)用于支持用于制造測(cè)試的確定性測(cè)試模式生成,當(dāng)芯片需要制造和系統(tǒng)內(nèi)測(cè)試時(shí),無(wú)需單獨(dú)的編解碼器邏輯。除了X容差功能外,TestMAX XLBIST還可以生成硬件,為系統(tǒng)內(nèi)測(cè)試和制造測(cè)試啟用功耗感知模式。它還支持基于高級(jí)故障模型(包括單元感知、路徑延遲和轉(zhuǎn)換)的系統(tǒng)內(nèi)測(cè)試模式。

在當(dāng)今充滿復(fù)雜設(shè)計(jì)的競(jìng)爭(zhēng)格局中,設(shè)計(jì)人員不能在IC的設(shè)計(jì)進(jìn)度和測(cè)試質(zhì)量之間做出妥協(xié),尤其是在安全關(guān)鍵型應(yīng)用中。通過(guò)進(jìn)行設(shè)計(jì)更改迭代或按照標(biāo)準(zhǔn) LBIST 的要求添加更多測(cè)試模式來(lái)實(shí)現(xiàn) X-clean 設(shè)計(jì)以滿足測(cè)試目標(biāo)是不可接受的解決方案。TestMAX XLBIST 在 X-clean 設(shè)計(jì)上以最佳方式執(zhí)行,同時(shí)還能夠處理具有 X 值的設(shè)計(jì),而無(wú)需更改設(shè)計(jì)或屏蔽整個(gè)掃描鏈,從而滿足設(shè)計(jì)進(jìn)度和測(cè)試質(zhì)量目標(biāo)。

審核編輯:郭婷

-

芯片

+關(guān)注

關(guān)注

456文章

50908瀏覽量

424486 -

集成電路

+關(guān)注

關(guān)注

5389文章

11567瀏覽量

362163 -

解碼器

+關(guān)注

關(guān)注

9文章

1143瀏覽量

40785

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于BIST利用ORCA結(jié)構(gòu)測(cè)試FPGA邏輯單元的方法

DFT和BIST在SoC設(shè)計(jì)中的應(yīng)用

BIST測(cè)試是否正確

數(shù)字BIST的基本原則

ZC706 BIST編譯在Linux上失敗

S32K BIST當(dāng)sw調(diào)用api Bist_Run() 以啟動(dòng)bist時(shí),mcu重置了怎么處理?

基于LFSR優(yōu)化的BIST低功耗設(shè)計(jì)

基于BIST的編譯碼器IP核測(cè)

針對(duì)FPGA可編程邏輯模塊的離線BIST測(cè)試方法

電源技巧:不要讓USB電壓下降減慢充電器的速度資料下載

不要讓X成為邏輯BIST的問(wèn)題

不要讓X成為邏輯BIST的問(wèn)題

評(píng)論