ASIC設計流程繼續變得越來越復雜,進度壓力繼續增加,看不到盡頭。與權力相關的考慮越來越不那么事后才想到。在過去,在實現設計目標時,滿足性能和面積目標通常是設計周期早期階段的主要目標。一旦獲得一些信心,電源規劃細節就變得更加重要,通常在流程的后期。事實上,過去芯片的電源完整性和可靠性在設計周期的最后階段得到了照顧,因為它可以這樣完成 - 有更多的時間和電源問題可以輕松解決 - 沒什么大不了的。因此,電源完整性留給了“電源簽核”專家。不幸的是,時代變了。隨著對高功率器件的需求不斷增加,以及不斷縮小的幾何形狀和對激進先進工藝的支持,越來越需要更早地將電源完整性和可靠性設計到設計流程中。授權設計師盡早解決這些問題變得至關重要。

他們提到,他們通常在設計周期結束時執行電源完整性檢查。但是,他們上一次的設計存在問題,因此他們需要重新思考和優化設計流程。他們錯過了流片期限,需要重新啟動芯片,因為與IR壓降相關的電源完整性問題使幾乎完成的ASIC設計無法正常工作。他們驚恐萬分地得出結論,他們需要找到一種方法來進行早期的功率分析和修復。他們以前不這樣做的原因是什么?這是因為沒有好的實用解決方案來輕松進行設計中的軌道分析。

傳統用戶的流被打破。在沒有設計內電源完整性分析且結果依賴于獨立電源完整性檢查的流程中,存在太多的痛苦,可歸因于兩個組件。

首先,分析步驟很痛苦,因為所需的數據需要從后端工具輸出,然后輸入到獨立的電源簽核工具中。設置很痛苦。第二個問題與獲取這些結果并以有意義的方式將它們反饋到后端工具有關。為什么會痛呢?根據客戶的投訴,他們最終要做的是編寫腳本來解析和利用該信息來做一些有意義的事情,并在從日志和報告中提取和處理信息后做一些手動工作。用戶一直說的是,這種痛苦是如此之大——“請創建一個設計中的解決方案。

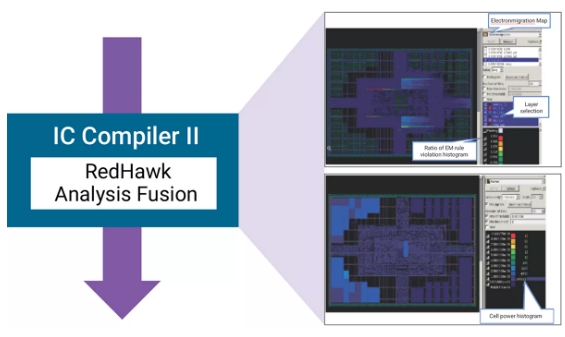

IC Compiler II的新功能是在引擎蓋下調用RedHawk Analysis Fusion以運行設計中的軌道分析,就是為了解決這個問題而創建的。使用簽核質量引擎,物理設計環境中的用戶現在可以更早、更頻繁地輕松執行分析,以幫助建立強大的電力網絡基礎,這樣后期階段就不會出現可能無法修復的缺陷。

通過與 IC 編譯器 II 的無縫集成,自動設置可在后臺創建必要的環境。由于物理設計和簽核使用相同的引擎,因此相關性是完美的。此外,對于物理設計師來說,它易于學習和使用,因此可以毫不費力地盡早運行并經常運行。這種新的流程是設計團隊的完美配方 - 這確實是一件多么美好的事情。

審核編輯:郭婷

-

IC

+關注

關注

36文章

5964瀏覽量

175788 -

asic

+關注

關注

34文章

1204瀏覽量

120560 -

編譯器

+關注

關注

1文章

1636瀏覽量

49173

發布評論請先 登錄

相關推薦

[原創]每天做好一件事

太奇葩!值班室里的“保安”,竟是由一件綠色雨衣偽裝

了解一下stm32中的外部中斷

中國VR江湖2016年最后一件大事:中國VR體驗店聯盟成立

來看看Pythoner志朋的爬蟲實驗

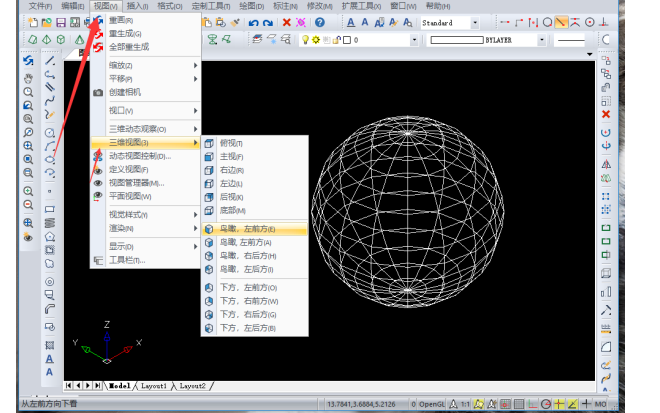

CAD教程之如何使用CAD編輯器中怎么繪制一個立體的彩色球體

挖礦到底是一件什么樣的事情

軍用萬用表,一件70年前的古董資料下載

設計中的軌道分析是一件美麗的事情

設計中的軌道分析是一件美麗的事情

評論