PVD篇

PVD是通過濺射或蒸發靶材材料來產生金屬蒸汽,然后將金屬蒸汽冷凝在晶圓表面上的過程。應用材料公司在 PVD 技術開發方面擁有 25 年以上的豐富經驗,是這一領域無可爭議的市場領導者。

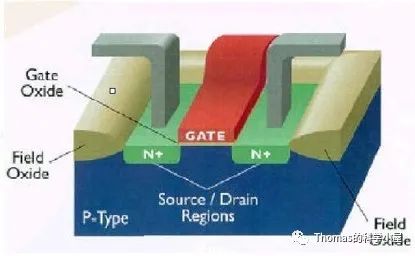

PVD 沉積工藝在半導體制造中用于為各種邏輯器件和存儲器件制作超薄、超純金屬和過渡金屬氮化物薄膜。最常見的 PVD 應用是鋁板和焊盤金屬化、鈦和氮化鈦襯墊層、阻擋層沉積和用于互連金屬化的銅阻擋層種子沉積。

PVD 薄膜沉積工藝需要一個高真空的平臺,在這個平臺上,將 PVD 沉積工藝與脫氣和表面預處理技術相集成,以獲得最佳的界面和薄膜質量。應用材料公司的 Endura 平臺是當前 PVD 金屬化的業界黃金標準。

EnduraPVD

當前 200mm 物理氣相沉積 (PVD) 面臨的挑戰在于,要能夠沉積更厚的高度均勻低溫兼容性薄膜。在功率器件市場中,能夠高速切換且形狀系數和空間占用小的器件,正推動對先進散熱技術的需求,如厚度范圍為 4μm 到超過 100μm 的 Al 層。

微機電系統 (MEMS)、CMOS 圖像傳感器和封裝技術(如硅通孔 (TSV))領域的新興應用,正在推動氮化鋁 (AlN)、氧化銦錫 (ITO)、氧化鋁 (Al2O3) 和鍺 (Ge) 等薄膜的 PVD 發展。

Endura PVD 200mm

應用材料公司的 Endura 平臺是半導體行業有史以來最成功的金屬化系統。憑借跨越前段金屬化(如鈷、鎢、鋁和銅互連)以及凸點下金屬化等封裝應用的沉積功能,過去 20 年制造的大多數微芯片均由 Endura 系統生產,目前,Endura 系統在全球的銷量已超過 4,500 套。

Endura 能夠以嚴格的薄膜厚度控制、出色的底部覆蓋率和高共形性沉積多種超純薄膜,這一能力是制造尖端器件的關鍵。該系統最多可容納九個工藝腔室,從而能夠混搭腔室,以創建集成的多步工藝序列。高度可配置的 Endura 平臺支持兩個可去除原生氧化物的預清潔腔室、多達六個 PVD 腔室以及兩個 MOCVD 腔室(可選),以確保滿足客戶薄膜沉積和器件性能要求。

升級

目前有數千臺 Endura 已投入使用,其中許多還是采用原始配置,因此我們提供了很多產品改進方案,可用于提升工藝性能和提高設備生產效率。例如,可通過將腔室 A 從流通腔室轉換為冷卻腔室,消除冷卻腔室的產能瓶頸。通過 EZ LCF 可避免晶圓放置錯誤,同時通過嚴格的邊緣排除來提升夾緊工藝的性能,并消除與多腔室工藝序列有關的層疊錯誤。此外,腔室升級可用于包括 TxZ 在內的許多腔室,以提升在片均勻性和減少維護工作。

EnduraVenturaPVD

隨著二維 (2D) 器件微縮達到物理和電氣極限,TSV 技術成為了一種向緊湊型、三維 (3D) 架構過渡的方法,在當前激增的移動技術中,該架構能夠以較低的功耗實現更快的性能和更強大的功能。TSV 技術使產品設計師能夠創建 3D 互連,通過連接堆疊芯片或晶圓的垂直路徑將各個節點的電路元件相集成。

應用材料公司的 Endura Ventura PVD 系統專為 TSV 金屬化而設計,是公司在物理氣相沉積(PVD) 領域的最新創新,使客戶能夠將其 2D 鑲嵌集成基礎設施和專門技術擴展到深寬比 ≥10:1 的 TSV 和 2.5D 中介層應用。它也是首個面向 TSV 的 PVD 系統,可實現具有量產價值的鈦阻擋層沉積。面向后段制程 (BEOL) 應用的現有 PVD 系統并不是專為此類高深寬比 (HAR) 特征而設計,這些系統需要高沉積率,以滿足生產效率的要求,并實現無孔洞間隙填充和良好的可靠性。為確保間隙填充和器件可靠性所必需的連續階梯覆蓋,這些系統必須沉積相對較厚的層。除了成本更高以外,厚薄膜增加了可能降低最終良率的應力缺陷風險。

Ventura 系統可應對這些 TSV 挑戰,顯著降低了大規模采用這一技術的技術與成本障礙。該系統采用了改進的離子密度、方向性和可調能量,以便在 HAR TSV 內部沉積比 BEOL 系統中的層薄 50% 的連續鉭或鈦阻擋層和銅種子層,并大大降低了生產成本。較薄的薄膜與較高的沉積速率使 Ventura 系統的產能超過現有的 BEOL PVD 系統的一倍以上。

該系統使我們的客戶能夠加工他們所選擇的材料。盡管應用材料公司并不出售這些材料,但 Ventura 腔室可在 Endura 平臺上與銅種子層工藝相集成,靈活處理鉭和鈦阻擋層。這兩種材料都展現出了高可靠性,但鈦具有更高的成本效益。

EnduraVersaXLR2 W PVD

隨著集成電路及其組件繼續微縮,組件之間的金屬互聯線和接觸件的尺寸也在縮小。其中一個結果為,這些連接器中的電阻越來越高。為生產更緊湊、更快速的電子器件,必須最大限度地降低電阻,以便能夠進一步地微縮。

這種更高的電阻所造成的慢化效應通常被稱做阻容延遲(或 RC 延遲),并以多種方式影響著電路。除這種不良效應以外,RC 延遲還會降低通過位線從 DRAM 結構讀寫數據的速度。此外,更高的電阻還會引起更高的功耗,這會為移動技術帶來不良的副作用。

降低線電阻的最簡單方法是增加導電金屬的體積,即使導線更寬和更高。但是,更寬的導線會限制微縮,更高的導線會增加電容,并帶來更大的刻蝕挑戰。因此,降低尖端器件的導線電阻側重于提升導電材料(DRAM 位線采用鎢 (W))的性能。

導體電阻是電子在穿過導體時所遇散射點密度的函數。薄膜中的雜質、晶粒邊界和表面粗糙度是減緩電子移動速度的某些障礙。Versa XLR2 W PVD 腔通過沉積更純凈和更光滑的鎢膜來降低互聯電阻,該鎢膜比使用當前技術所沉積的鎢的電阻率低 10-15%。

新系統借助關鍵硬件組件的創新實現了這一質量增強,如微波源磁控管、新穎的工藝化學和等離子體特征調制。Versa XLR2 W 系統所生產的電阻率更低的鎢是微縮的促成者,它將擴展作為位線金屬的鎢在用于 1xnm 節點的 DRAM 技術中的用途。以下動畫解釋該系統的出色薄膜如何提升器件的性能。

RC 延遲舉足輕重,因為這可能成為繼續向下微縮邏輯和存儲器設備的重大障礙,而該項技術對于提升當前的多功能、移動消費電子設備的性能至關重要。

邏輯和存儲芯片中的有源器件(晶體管)均通過金屬線以電氣方式連接彼此或芯片的其他區域。這些導線通過不導電(絕緣)介電層彼此分離。在邏輯和存儲芯片中,互聯線的作用為將信號從芯片的一個區域傳輸到另一個區域。能盡快完成信號傳輸,并能最大限度地降低幾何尺寸縮小所造成的信號損失,這一點對器件微縮至關重要。在邏輯芯片中,微縮是指面積縮小,即借助于材料和設計創新,在更小的面積中封裝越來越多的電路。在對價格敏感的 DRAM 制造領域,必須大幅控制成本,所以微縮側重于從現有的材料和設計中獲得逐步增強的性能。總之,邏輯和存儲器導線中的信號傳輸速度受相同的基本原理支配,并取決于電阻和電容 (RC) 的乘積。同時降低電阻和電容是理想的方法。但是,對于存儲器制造商而言,開發電容較低的絕緣材料并將其集成到制造流中的成本特別高。因此,降低電阻成為保證微縮后的性能的首選方法。根據電荷是垂直穿過不同的布線層,還是沿導體的長度橫向通過,需要使用各種解決方案來應對 RC 挑戰。盡管,無論對于哪種情況,其目標都在于最大限度地降低金屬線的電阻。在垂直尺寸中,解決方案旨在最大限度地減小界面電阻。電接觸件將有源區連接到第一級金屬布線層。半導體-金屬界面(或歐姆接觸層)形成了有源區和金屬接觸層之間的接面。其目標在于,確保電荷能夠從有源區通過接觸件前往上層布線層,然后返回。為在歐姆接觸層之間實現最快速和最大化的電荷傳輸,應形成低電阻率材料層。低電阻率硅化鈷已作為此用途的行業標準被采用,其有效性依賴于能否沉積均勻的一層,以形成堅固的歐姆接觸層。

EnduraiLBPVD/ALD

隨著器件尺寸縮小,而集成式襯墊/阻擋層 (iLB) 厚度消耗更多的鎢插頭體積,接觸電阻在不斷增加,造成相應的困難;應用材料公司配備 Centinel沉積室的 Endura iLB PVD/ALD 系統解決了這一難題。

該系統以低成本高效的方式利用 ALD(原子層沉積)技術,通過 90% 以上覆蓋超薄、均勻、優質的阻擋膜,將客戶現有的 iLB PVD/CVD 安裝基礎擴展至 32nm 及之上。它在沉積 TiN 膜時將等離子損傷或高介電材料屬性不利變化的風險降到最小,從而支持先進的內存應用。

Centinel 技術通過 RE-ALD 室(經原子團增強的原子層沉積室)增強了 Endura iLB 集成式 PVD/CVD(物理氣相沉積/化學氣相沉積)工藝平臺,通過實現 32nm 以下邏輯器件中更小的接觸電阻而優化鎢體積。它也設計用于 4X 節點嵌入式 DRAM、DRAM 電極和掩埋字線應用。

Centinel 工藝實現的出色階梯覆蓋能使阻擋層厚度最小化,從而優化均勻沉積的內部特性。除了使鎢填充可用的體積最大化之外,阻擋層的極限厚度減少了加工每枚硅片所需的時間,并有助于提高生產率。由于不發生背面沉積,生產率不受背面清潔的不利影響。另一項好處是沉積室工作的加工溫度更低,從而減少對高介電材料的再結晶損害。

PikaPVD

應用材料公司的 Pika PVD 系統是當今業界體積最小、速度最快的單晶圓 PVD 設備,設計用于以較低的擁有成本開展高性能研發和小批量生產。該系統設計緊湊 (1657mm x 755mm x 1822mm),包含脫氣、預清潔和濺射沉積模塊,并配備高真空機械手傳送室和完整的盒對盒自動化功能。它具有很高的可靠性,正常運行時間超過 92%。

該設備支持選擇各種 PVD 濺射源,包括直流電、脈沖直流電、射頻濺射,其金屬或反應性濺射工藝能夠共濺射金屬和氧化物的合金。D 源磁控管技術的工藝流程經過驗證,可在硅、玻璃、有機材料、金屬和砷化鎵或其他 III-V 化合物的襯底上沉積各種單層膜和多層膜。Pika 系統的即插即用設計可最大程度地減少設置時間。

TopazPVD

應用材料公司的 Applied Topaz PVD 系統可滿足市場對 PLP (面板級封裝)不斷增長的需求,憑借領先的技術能力,可處理最大尺寸為 600mm x 600mm 的襯底。市場需要更低成本、更高性能的電子產品,而這種需求促使半導體行業從 WLP (晶圓級封裝)轉向 PLP。在標準化固定成本支出上,PLP 不到晶圓級封裝的一半。

針對扇出型晶圓級封裝(FOWLP)、LCD 和印刷電路板所開發的制程技術和設備的融合,使扇出型封裝技術變得非常實惠。成本的降低將使該技術能夠廣泛應用于移動電子設備(例如,系統級封裝、處理器、射頻和電源管理)、汽車和物聯網等多種半導體封裝應用中。

除了 PLP,Topaz 系統還可以處理玻璃和有機中介層以及在襯底中嵌入裸片等應用。它獨特的模塊化架構可實現低接觸電阻;將最小所需粘合強度加倍;低壓力;更低的襯底溫度 (<120C°);在刻蝕或激光鉆孔中形成具有極佳側壁覆蓋率的共形種子層。

Axcela PVD

在過去十年的應用中,堪稱同類最佳的 應用材料公司 Axcela PVD 系統已證明了其工藝優越性和穩定性,非均勻度小于 2% 1σ。每個濺射腔室在設計上都盡量降低設備擁有成本,方便保養維護,可形成厚達 8μm 的厚膜,標配沉積三種不同材料的能力,并且可以選擇共濺射以提高沉積速率。該系統結構緊湊,可采用 150、200、300 或 330mm 等多種組合配置。系統包括脫氣、預清潔和 PVD 腔室模塊,可滿足多種應用需求,以及最優的工藝和產量要求。這種簡單易行的系統配置能力,使客戶可為特定的應用來選擇最理想的配置。

Axcela 系統的小批量集群架構使這種高度可靠的 PVD 工具成為大多數金屬化應用(包括 EMI 屏蔽、背面金屬化、MEMS、TSV、UBM 和 RDL)的絕佳選擇。它可以嚴格控制薄膜的沉積厚度,從而幫助工藝和制造工程師以滿足苛刻的設計要求。

D 源磁控管可通過全面腐蝕來提高標靶利用率。腔室和靶材的架構,使其可以最大效率收集從靶材濺射出來的原子,而不是將其浪費在屏蔽罩上。磁控管和屏蔽罩的設計方便了系統的超低顆粒計數。

200mm 和 300mm 腔室中帶封裝的 EMI 環

ChargerUBM PVD

應用材料公司的 Charger UBM PVD 系統在芯片封裝金屬沉積工藝的生產效率和可靠性方面樹立了新的標準。Charger 系統專為 UBM、RDL 和 CMOS 影像傳感器應用而設計,它采用線性架構,其晶圓產量是其他同類設備的兩倍以上,達到市面上最高的生產效率。此外,系統集成最新的 Volaris預清洗技術,在兩次保養間隔期內可處理更多的晶圓,達到極長的無故障運行時間,并實現目前最低的單位晶圓成本。

Volaris 預清洗腔室在設計上能最大程度減少有機膜除氣所帶來的污染物,與傳統的電感耦合等離子體濺鍍反應腔室相比,可將傳統應用中的同類最佳接觸電阻性能擴展到最先進的技術節點。這種獨特的原位清洗技術延長了工藝套件的使用壽命,降低了預防性維護保養的頻率,從而降低了生產成本,提高了產量,最大程度減少了客戶的封裝沉積系統擁有成本。

優良的磁控和 PVD 反應腔室經過改進,對于 UBM 和 RDL 應用中使用的各種金屬(如 Ti、TiW、Cu 和 NiV),可滿足嚴格的薄膜沉積均勻性規格。

Charger 系統模組架構增強了配置靈活性,可在極短的停機時間內,將緊湊的三反應腔室配置輕松擴展為五反應腔室的大規模量產制造系統。

EnduraALPSPVD (ALPS Co & Ni)

應用材料公司的 Endura ALPS(先進低壓源)Cobalt PVD(物理氣相沉積)系統為高深寬比結構的柵極和接觸孔應用提供簡單的高性能金屬硅化物解決方案。ALPS 技術將鈷延伸至 90nm 技術節點以下,可提供優良的鈷底部覆蓋,且不會對器件造成等離子損傷,缺陷數量極少。Endura ALPS Co 提供出色的電阻率、低漏電流和熱穩定性,解決了鈦凝聚、接觸孔電阻變化和摻雜物吸出等難題。

對于 65nm/55nm 及以下節點的邏輯和存儲應用,鈷的硅消耗和硅化鈷/硅界面的粗糙度變得更加關鍵。Endura ALPS Ni PVD 系統可沉積穩定的硅化鎳薄膜,使硅消耗量減少 2 倍,薄膜界面更平滑,電阻率更低。ALPS Ni 可實現 100? 底部覆蓋,不對器件造成等離子損傷,同時還能最大程度減少微粒數量。

應用材料公司的 Endura ALPS Ni PVD 系統采用單腔室 Siconi Preclean 界面處理技術,解決了硅化鎳 (NiSi) 沉積前硅表面清洗準備的難題。Siconi Preclean 可提供高選擇比清洗 (>20:1 SiO2:Si, >5:1 SiO2:SiN),無需傳統 HF 清洗工藝所必需的清洗與鎳沉積之間的嚴格等候時間控制。通過遠程等離子源生成刻蝕劑,可減少對襯底的損壞,最大程度減少對氮化硅間隔層和硅柵等結構的刻蝕。此外,器件研究表明,與傳統 HF 浸洗法相比,Siconi Preclean 能減少 NiSi2尖峰缺陷,改善結漏電。

EnduraAmberPVD

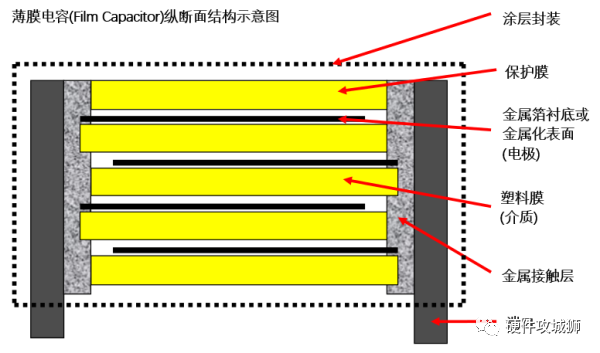

可靠及完整地用銅填充互連溝槽和通孔結構,對于微電子制造的器件可靠性非常重要。該工藝的必要步驟為沉積阻擋層(防止銅擴散至周圍絕緣材料)和銅種子層[方便隨后的電化學沉積(或電鍍)],使其不會出現孔洞和縫隙。

迄今為止,電離物理氣相沉積 (PVD)已能在所有電鍍表面達到所需的覆蓋厚度和連續性。但是,當節點小于 2xnm 時,即使采用最優化的阻擋層/種子層工藝,覆蓋完好無任何凸懸,也無法控制特征深寬比來滿足電鍍要求。

獨特的 Endura Amber PVD 系統通過成熟的集成化方法,將冷沉積工藝與高溫熱銅回流工藝相結合,取代了 EnCoRe II RFX 銅晶種技術,一舉解決了這一難題。在 1xnm 技術節點下,超小通孔開口周圍會出現銅凸懸,使得無法采用常規的 PVD 工藝達到最佳電鍍所需的側壁和種子層覆蓋。新系統擴展了當前技術的應用,通過銅回流,增強了 PVD 沉積工藝,實現自底向上的填充。這個兩步驟工藝通過減少通孔的有效深寬比(應用一次)或完全填充通孔(重復應用),簡化了電鍍過程,使無孔洞填充更有保障,從而確保器件的可靠性。沉積/回流工藝中的每一步都能獨立控制溫度,可靈活地與各種襯墊材料結合使用。

這一創新的銅晶種技術與預清潔和 EnCoRe II Ta(N) 阻擋層技術在高度真空條件下整合至 Endura 平臺,在量產中可達到高的器件良率。

EnduraAvenirRF PVD

對于高縱橫比 Ni(Pt) 邏輯接觸硅化,該系統在高壓電容耦合等離子體模式下運行,可產生更高的金屬電離密度,從而實現更好的底部覆蓋。

隨著器件尺寸縮減,特征變得更加脆弱,深寬比不斷增加,使當前的 PVD(物理氣相沉積)技術在填充較深的狹窄結構、避免等離子損傷方面的難度升高。使用基于 RF 的低功率等離子體可最大限度地減輕損傷風險,并取得更均勻的等離子體密度分布,從而能夠實現更好的底部覆蓋和更高的均勻度。

Endura Avenir 系統的 RF PVD 解決了 22nm 及以下節點的高 K / 金屬柵極應用以及邏輯接觸硅化物問題。

對于高 K / 金屬晶體管,Avenir 系統為前柵極和后柵極集成方案提供了各種解決方案,從而使芯片制造商能夠在這兩種方法之間輕松轉換。對于前柵極,RF PVD 技術能夠實現可控的高均勻度連續薄膜沉積 (<10?)。對于后柵極,高壓力電容耦合等離子體操作可用于確保良好的底部覆蓋率和最小的懸突。該系統的 RF PVD 技術不僅可以沉積超薄覆蓋層和金屬柵極薄膜,還可以最大限度地降低損傷風險,從而形成無電荷陷阱的突變界面。該系統的調優能力能夠實現精確的 TiN 薄膜化學計量控制,以便在不犧牲薄膜均勻度的前提下實現整體 Vt 控制。就有效功函數而言,該需求可轉換為 <4.2eV(對于 NMOS)和>5.0eV(對于 PMOS),以便實現高性能。對于NMOS和> 5.0eV用于高性能的PMOS。

對于高深寬比的 Ni(Pt) 邏輯接觸硅化物,該系統在高壓力電容耦合等離子體模式下運行,以便實現更高的金屬電離密度和底部覆蓋率。

RF PVD 硅化腔室所實現的底部覆蓋率比傳統的 PVD Ni(Pt) 工藝高一倍,它可以在深寬比為 5:1 的特征層底部實現大于 70% 的場厚度,并在特征層之內以及晶圓的中心到邊緣之間實現一致的底部覆蓋率。一致的底部覆蓋率 (3%, 1σ) 可轉化為一致的電阻和更低的泄漏率,而高鉑組分均勻度可轉化為高器件成品率。相比傳統的 PVD Ni(Pt) 技術,該系統在提供這一性能的同時將耗材成本降低了 30%。

在生產中久經考驗的 Endura 平臺可為高 K / 金屬柵極和邏輯接觸硅化物應用提供了獨特的集成能力。對于柵極應用,它提供了全套 PVD、CVD 和 ALD 技術。對于接觸層,它將 Siconi 預清潔、硅化和氮化鈦覆蓋工藝結合在一起。

EnduraCirrusHT CO PVD

隨著集成電路及其組件繼續微縮,組件之間的金屬互聯線和接觸件的尺寸也在縮小。其中一個結果為,這些連接器中的電阻越來越高。為生產更緊湊、更快速的電子器件,必須最大限度地降低電阻,以便能夠進一步地微縮。

這種更高的電阻所造成的慢化效應通常被稱做阻容延遲(或 RC 延遲),并以多種方式影響著電路。除這種不良效應以外,RC 延遲還會降低通過位線從 DRAM 結構讀寫數據的速度。此外,更高的電阻還會引起更高的功耗,這會為移動技術帶來不良的副作用。

微縮的另一個副作用為,深寬比隨著先進電路中的特征密度增加而增加。結果,以足夠的底部覆蓋率沉積薄膜變得越來越具挑戰,而足夠的覆蓋率是最終器件達到適當的電氣性能所必需的。DRAM 結構中尤為重要的是有源區和第一級金屬互聯層之間的半導體-金屬界面。為在這些界面之間實現最快速和最大化的電荷傳輸,應使用低電阻率材料(硅化鈷),其有效性取決于適當的沉積厚度和均勻的界面層。

Endura Cirrus HT Co PVD 系統可通過增強功能來實現所需的硅化物覆蓋率,以應對縮小的接觸面積和增加的深寬比所帶來的挑戰。相比其他來源技術,使用高頻 RF 源可產生金屬離子濃度更高的等離子體,該系統可在高深寬比特征層的底部實現出色的厚度和一致性。晶圓上的負電壓用于將正金屬離子引入窄孔中,由于存在更多的金屬離子,所以高深寬比接觸孔底部的覆蓋度比當前技術所實現的覆蓋度厚兩倍或三倍。因此,形成了堅固的硅化鈷層,以降低電荷在金屬和半導體之間的傳輸壁壘。

該系統將 Siconi 硅化物預清潔與用于 DRAM 外圍電路中的直接接觸應用的 PVD 鈷和氮化鈦蓋帽沉積結合在一起。

歐姆接觸層的挑戰

在存儲設備中,歐姆接觸層(半導體-金屬界面)將有源區與金屬布線層連接在一起。隨著存儲器繼續微縮,節點之間的歐姆接觸層面積縮小了約 70%,特征層中的深寬比增加,在特征層中必須沉積低電阻率硅化物,以形成該接觸層。在 1xnm DRAM 中,這兩個因素使形成足夠厚的硅化鈷層日益困難,而足夠的厚度是為了確保電荷能夠快速、可靠地從有源區通過接觸件前往上層布線層,然后返回。

以下動畫闡明了歐姆接觸層的概念以及 Endura Cirrus HT Co PVD 系統所產生的厚硅化物覆蓋層對設備性能的有利影響。

RC 延遲舉足輕重,因為這可能成為繼續向下微縮邏輯和存儲器設備的重大障礙,而該項技術對于提升當前的多功能、移動消費電子設備的性能至關重要。

邏輯和存儲芯片中的有源器件(晶體管)均通過金屬線以電氣方式連接彼此或芯片的其他區域。這些導線通過不導電(絕緣)介電層彼此分離。在邏輯和存儲芯片中,互聯線的作用為將信號從芯片的一個區域傳輸到另一個區域。能盡快完成信號傳輸,并能最大限度地降低幾何尺寸縮小所造成的信號損失,這一點對器件微縮至關重要。在邏輯芯片中,微縮是指面積縮小,即借助于材料和設計創新,在更小的面積中封裝越來越多的電路。在對價格敏感的 DRAM 制造領域,必須大幅控制成本,所以微縮側重于從現有的材料和設計中獲得逐步增強的性能。總之,邏輯和存儲器導線中的信號傳輸速度受相同的基本原理支配,并取決于電阻和電容 (RC) 的乘積。同時降低電阻和電容是理想的方法。但是,對于存儲器制造商而言,開發電容較低的絕緣材料并將其集成到制造流中的成本特別高。因此,降低電阻成為保證微縮后的性能的首選方法。根據電荷是垂直穿過不同的布線層,還是沿導體的長度橫向通過,需要使用各種解決方案來應對 RC 挑戰。盡管,無論對于哪種情況,其目標都在于最大限度地降低金屬線的電阻。在垂直尺寸中,解決方案旨在最大限度地減小界面電阻。電接觸件將有源區連接到第一級金屬布線層。半導體-金屬界面(或歐姆接觸層)形成了有源區和金屬接觸層之間的接面。其目標在于,確保電荷能夠從有源區通過接觸件前往上層布線層,然后返回。為在歐姆接觸層之間實現最快速和最大化的電荷傳輸,應形成低電阻率材料層。低電阻率硅化鈷已作為此用途的行業標準被采用,其有效性依賴于能否沉積均勻的一層,以形成堅固的歐姆接觸層。在橫向尺寸中,解決方案旨在優化導線金屬材料的導電性。所謂的線性電阻表示導線尺寸(寬、高、長)與導線制備材料(通常為鎢或銅)的特定性能的函數。降低線電阻的最簡單方法是增加導電金屬的體積,即使導線更寬和更高。但是,更寬的導線會限制微縮,更高的導線會增加電容,并帶來更大的刻蝕挑戰。因此,降低尖端器件的導線電阻側重于提升導電材料的性能。

EnduraCirrusHTX PVD

通過革新用于氮化鈦 (TiN) 薄膜的物理氣相沉積 (PVD) 技術,Endura Cirrus HTX TiN 解決了下一代設備的硬掩膜可擴展性挑戰。隨著芯片特征尺寸的進一步縮小,硬掩膜創新對于更復雜微小互連結構的精確圖形化至關重要。借助在 PVD 領域多年的專門技術,新系統可生產能夠在 10nm 以下的節點中確保圖案保真度的突破性硬掩膜。

隨著芯片設計的發展,芯片的特征尺寸逐漸變小、深寬比變得更高、封裝越來越密集,以便生產先進的集成電路。結果,在創建電路(或互聯線)時,用于定義刻蝕的和金屬化的圖形的材料對保持這些圖形的完整性極其重要。輕微的缺陷可能造成無法適當地金屬化器件,使其不可靠或無功能。

在互連線制造工藝中,氮化鈦 (TiN) 一直是低 K 介電質圖形化的標準硬掩膜材料。然而,在先進節點,為降低器件電容,將介電質逐漸制作得更加多孔,使其變得更脆弱,并且在疊加的 TiN 掩膜的壓縮應力影響下,容易在刻蝕后變形(線路彎曲和圖形坍塌)。盡管消除這一自然壓縮應力會降低薄膜密度,但這對耐受刻蝕工藝是必須的。

在一項重大突破中,Endura Cirrus HTX PVD 系統采用了頻率極高的 RF 源,以產生便于修改薄膜的結晶定向的高度電離化等離子體,從而解決了應力和密度之間的棘手權衡。最終形成的 TiN 達到了抗張應力性與高密度的理想結合,從而帶來極佳的刻蝕選擇比、出色的 CD 線寬控制和通孔堆疊對準,以及密集復雜圖形的高保真度。出色的薄膜厚度均勻性與低缺陷率使新系統能夠減少變異性和產生非常精確的圖形。

EnduraCloverMRAM PVD

應用材料公司的 Endura Clover MRAM PVD s系統是用于磁性隨機存取存儲器 (MRAM) 器件大規模量產 (HVM) 的首款具有生產價值的集成材料解決方案(Integrated Materials Solution)。閃存基于電荷的運行特性使其面臨著縮放限制;MRAM 最有望成為其替代品,因為其基于電阻的運行更具可縮放性,同時還提供了存儲器半導體應具備的關鍵特性:非易失性、隨機訪問和強大的耐用性。

EnduraCuBS RFX PVD

應用材料公司的 Endura CuBS(銅阻擋層/種子層)RF XT PVD 系統用于 3x/2x 及更先進節點的邏輯和存儲器件應用。SIP(自離子化等離子體)EnCoRe II Ta(N) 阻擋層和 EnCoRe II RFX 銅晶種層處理室采用高電離 PVD 技術,該技術能夠以最小的懸突和光滑的形態實現完全覆蓋的低溫薄膜沉積。

EnCoRe II Ta(N) 腔的厚度調優功能使客戶能夠降低阻擋層的厚度,以便將線性電阻微縮到 3x/2x 節點的水平,同時通過出色的底部和側壁覆蓋層減少電遷移和應力遷移。對于銅晶種層,EnCoRe II RF XT Cu 腔采用了創新的磁控運動、磁通量控制和高再濺射比機制,以進一步增強同形覆蓋。

這些技術緩解了會降低金屬空隙填充品質的問題,如晶圓邊緣的線端孔隙或 CMP 處理后的缺陷。

為解決隨幾何尺寸縮小而日益重要的界面問題,應用材料公司提供了各種預清潔技術,以便在不影響關鍵尺寸或材料特性的前提下,確保界面完整性。Endura CuBS RF XT 系統采用了新型 Aktiv Preclean [腔體或工藝] 方法,該方法提供了突破性的預清潔技術,以便有效地去除聚合物殘留和減少 CuO,同時保護多孔的低 k 級間介電薄膜,如Black Diamond II。和傳統的反應性預清潔方法不同的是,Aktiv Preclean 工藝不會明顯改變 k 值,所以這便于向下一代低 k 介電層過渡。

應用材料公司的 Endura CuBS RF XT PVD 系統在高真空條件下依次沉積 Ta(N)/Ta 阻擋層,然后沉積銅種子層。通過在 Endura 平臺上整合全系產品(包括新型 Aktiv Preclean),可確保出色的膜層附著力和無氧化物界面,同時保持 k 值完整性,以實現低通孔電阻和高器件可靠性。

EnduraImpulsePCRAM PVD

應用材料公司的EnduraImpulsePVD系統是用于相變隨機存取存儲器 (PCRAM) 和電阻式隨機存取存儲器 (ReRAM) 器件大規模量產 (HVM) 且具有生產價值的集成材料解決方案(Integrated Materials Solution)。PCRAM 和 ReRAM 是新興的非易失性存儲器,可填補 DRAM(用于數據處理)和 NAND(用于數據存儲)之間不斷擴大的性價比差距。PCRAM 和 ReRAM 可以提高存儲和檢索的速度、用電效率和可靠性,即使在斷電時也能保留軟件和數據。

EnduraIoniqW PVD

隨著集成電路及其組件不斷微縮,組件之間的金屬互聯線和導線的尺寸也在縮小。由此帶來的一個結果是,這些互連結構的電阻越來越高。

這種高電阻會造成慢化效應,通常稱為阻容延遲(或 RC 延遲),它會降低傳導速度,增加功耗,從而影響芯片性能。為了制造結構更緊湊、速度更快的電子器件,必須最大限度降低這些連接結構的電阻,使其能進一步微縮。

應用材料公司新推出的 Endura Ioniq PVD 系統是一種 Integrated Materials Solution(集成材料解決方案),它在一個高度真空的平臺上將先進的制造工藝與 CVD 技術和預處理腔室相結合,可在各種導線應用中實現純鎢(W)材料金屬化。它取代了需要多臺設備來完成的、具有高電阻的單一的氮化鈦襯底、鎢成核層和大塊鎢填充物,代而采用融合 CVD 大塊鎢填充物的單一 PVD 鎢層。Ioniq PVD 腔室增強的電離功能和定向流量控制打造出極佳的均勻階梯式覆蓋純鎢膜,用作低電阻的阻隔層和襯墊層。持續的高真空環境可保持薄膜的完整性,進一步提高了金屬界面的純度和電導率。

應用材料公司的 Endura Ioniq PVD 系統將鎢(W)在邏輯應用中的關鍵導線處的使用擴展到了 5 納米以下,同時也為 DRAM 和 NAND 器件的低電阻連接提供了一種獨特的金屬化方法,有助于進一步推進器件微縮。

-

晶圓

+關注

關注

52文章

4912瀏覽量

127988 -

邏輯器件

+關注

關注

0文章

88瀏覽量

20099 -

PVD

+關注

關注

4文章

49瀏覽量

16979

原文標題:Applied Materials產品庫----PVD篇

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺談薄膜沉積

第三代半導體熱潮“帶貨”沉積設備需求,供應鏈與服務本地化成關鍵考量

芯片薄膜工藝是什么

物理氣相沉積及濺射工藝(PVD and Sputtering)

半導體設備行業跟蹤報告:ALD技術進行薄膜沉積工藝優勢

韞茂科技獲數億元融資,加快薄膜沉積設備量產

沉積氮化硅薄膜的重要制備工藝——PECVD鍍膜

基于PVD 薄膜沉積工藝

基于PVD 薄膜沉積工藝

評論