最近基于cortex-M0/M0+的mcu增多了,學習了大佬凌煙慕魚的作品,這里記下來,以便以后學習。

Cortex M0+保留了Cortex-M0的全部56個指令。

根據功能可以將Cortex-M0+處理器的指令化為以下幾組

在處理器內移動數據

MOV,MRS(move special register to register),MSR

存儲器訪問

LDR(LDR,LDRH,LDRB),STR(STR,STRH,STRB),LDM,LDMIA(基地址寄存器會更新),STMIA

棧空間訪問

PUSH,POP(都可以用來操作多個寄存器,SP的值=棧頂的數據的地址值+4)

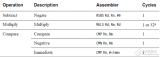

算數運算

ADD,ADDC(帶進位的加法),SUB,SBC(帶借位的減法),MUL,CMP,CMN(負數比較)

邏輯運算

AND,ORR(邏輯或),EOR(邏輯亦或),BIC(邏輯位清除),MVN(邏輯位取反),TST(位與)

移位和循環操作

ASR(最高位不變,最后一位移出位到APSR中的進位標志),LSL,LSR,ROR(循環右移)

展開和順序反轉操作

REV(字節反轉),REV16(半字內的反轉),REVSH(低半字內的字節順序反轉,并進行有符號展開)這些反轉指令通常用于大小端系統之間數據轉換。

SXTB(對字數據中的最低字節進行有符號展開),SXTH,UXTB(對字數據中的最低字節進行無符號展開),UXTH

符號根據第7位或者第15位來決定

程序流控制

B(無條件跳轉),B< cond ><標號> (條件跳轉,有14個可選cond后綴),BL(跳轉并將返回地址存儲到LR),BX(跳轉并根據寄存器的值第0位修改處理器狀態)

一般使BL調用子函數,BX LR返回

存儲器屏障指令

DMB,DSB,ISB

這些指令用于復雜的存儲器系統。Cortex-M0只有一個存儲器接口連接到存儲器系統,并且系統總線接口上沒有緩存,所以這些指令一般用不到。但是還是支持3個存儲器屏障指令

異常相關指令

SVC 請求管理調用,一般用于系統服務的入口或者API

CPS 使能或者禁止中斷

其他功能

NOP,BKPT(斷點)

偽指令

發布評論請先 登錄

相關推薦

ARM Cortex-M0+中斷機制和中斷編程步驟

ARM Cortex-M0+內核定時器

ARM Cortex-M0+處理器數據表

thumb指令集是什么_thumb指令集與arm指令集的區別

Cortex-M系列處理器指令集_指令集特性比較總結

學習 Cortex-M0+指令集

學習 Cortex-M0+指令集

評論