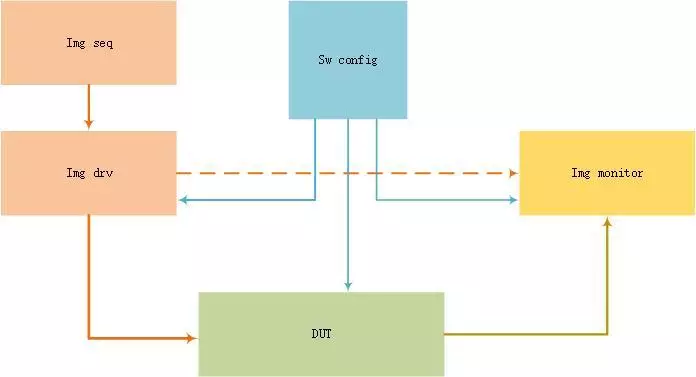

在許多驗證環境中,我們在不同的測試用例中重復使用相同的配置周期。這些周期可能涉及從不同的配置和狀態寄存器寫入和讀取、加載程序存儲器和其他類似任務,以為其目標激勵設置DUT。在許多此類環境中,這些配置周期所花費的時間非常長。此外,由于驗證工程師必須為不同的測試用例運行同一組經過驗證的配置周期,因此存在大量冗余,從而導致生產力下降。對于具有多個接口的復雜驗證環境尤其如此,這些接口需要配置不同的組件。

Verilog 提供了在特定時間點保存設計及其測試平臺狀態的選項。我們可以將模擬恢復到相同的狀態,然后從那里繼續。這可以通過從Verilog代碼添加適當的內置系統調用來完成。VCS 提供與統一命令行解釋器 (UCLI) 相同的選項。

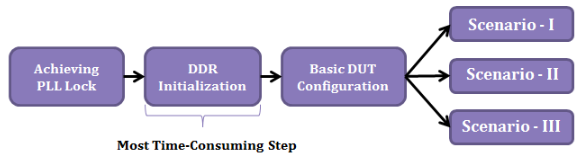

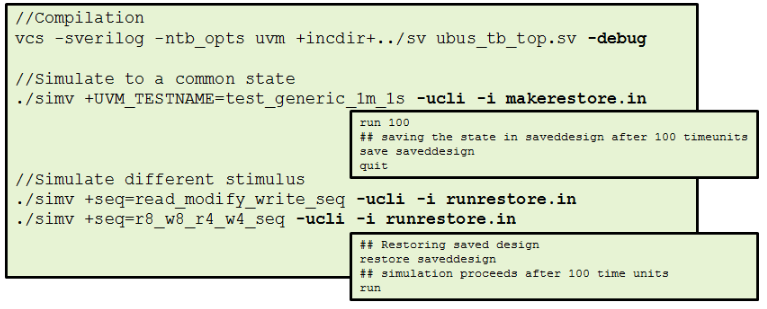

但是,我們僅從保存的狀態恢復仿真是不夠的。對于不同的模擬,我們可能希望對DUT應用不同的隨機激勵。在 UVM 的上下文中,最好從保存的狀態運行不同的序列,如下所示:

在上面的例子中,除了最后一步在很大程度上變化之外,其余步驟一旦建立就不需要迭代。

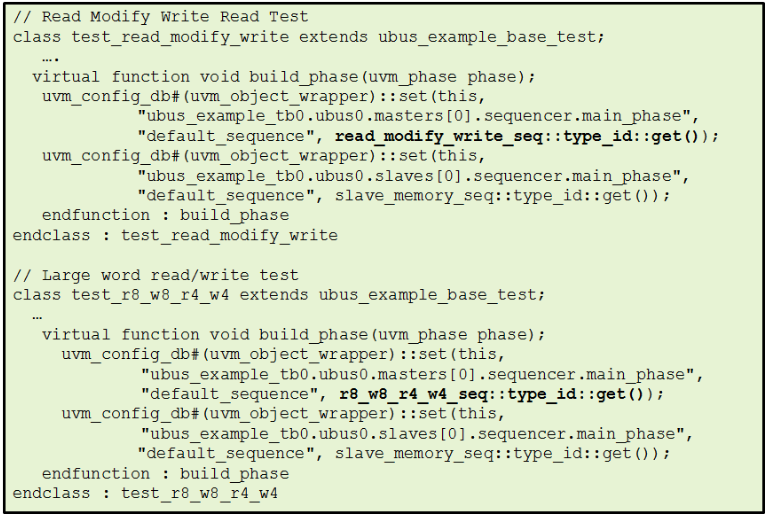

在這里,我們將解釋如何使用標準UVM安裝中可用的簡單現有UBUS示例來實現上述策略。在環境中進行了簡單的更改,以顯示引入此附加功能需要執行的操作。在現有的測試集中,它們中的兩個,“test_read_modify_write”和“test_r8_w8_r4_w4”,僅在執行的主序列上有所不同:“read_modify_write_seq”和“r8_w8_r4_w4_seq”。

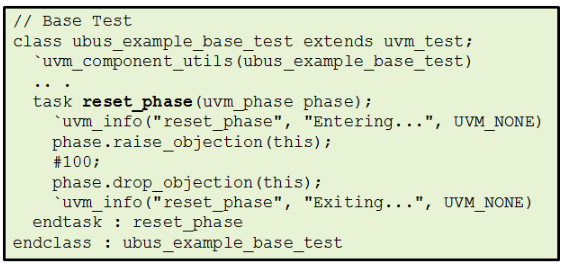

假設我們有一個場景,我們希望在reset_phase完成后保存模擬,然后在恢復的模擬reset_phase后開始執行不同的序列。為了通過UBUS測試演示類似的場景,我們在基本測試的reset_phase中引入了延遲(在實際測試中,這可能對應于PLL鎖,DDR初始化,基本DUT配置)。

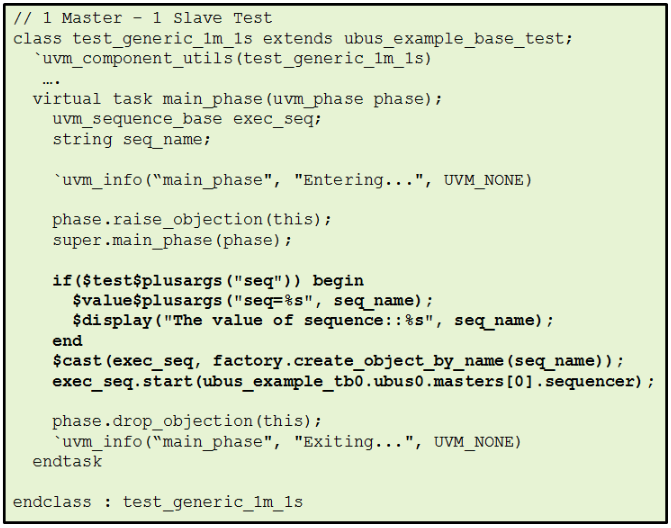

以下代碼片段顯示了如何修改現有測試,以引入在不同“還原”模擬中運行不同測試的功能:

在這里,我們進行了兩個主要修改:

將階段default_sequence的設置從構建階段轉移到主階段的開始。

從命令行獲取序列的名稱作為參數,并在代碼中適當地處理字符串,以在相關排序器上執行序列。

如您所見,更改保持在最低限度。有了這個,上面的通用框架就可以進行了仿真。在 VCS 中,啟用保存/恢復流程的一種方法是:

因此,上述策略有助于通過驗證流程中的簡單更改來優化計算資源。希望這很有用,并且您可以輕松地在驗證環境中進行更改以采用此流程并避免冗余的模擬周期。

審核編輯:郭婷

-

存儲器

+關注

關注

38文章

7518瀏覽量

164080 -

Verilog

+關注

關注

28文章

1351瀏覽量

110187 -

代碼

+關注

關注

30文章

4808瀏覽量

68812

發布評論請先 登錄

相關推薦

vcs和xrun搭配uvm1.1/uvm1.2版本庫的使用情況

UVM環境的看門狗怎么沒看住超時了?

IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(六)

什么是uvm?uvm的特點有哪些呢

請問一下在UVM中的UVMsequences是什么意思啊

如何使用Xilinx AXI VIP對自己的設計搭建仿真驗證環境的方法

我的第一個UVM代碼——Hello world

NetScreen防火墻策略與冗余配置指南

集成級的UVM寄存器模型

Modelsim uvm庫編譯及執行

基于最大信息系數與冗余分攤策略的特征選擇方法

通過簡單的保存-恢復策略避免UVM VIP的冗余仿真周期

通過簡單的保存-恢復策略避免UVM VIP的冗余仿真周期

評論