對于高速信號的匹配和對接,從電氣來考慮的話,主要考慮兩個方面的問題:

1、AC信號的擺幅和回路

2、DC電平的幅度和回路

如果從實際設計的方便和合理的角度來考慮的話,要把握幾個基本原則:

1、容易布板

2、功耗最小

3、匹配方式最簡單(阻容個數最少)

一般情況下,如果是同一種電平信號的對接,基本上都是采用直流耦合方式對接就可以了。

但是對于不同信號電平之間的對接來說,AC的幅度和DC的幅度不一定能夠完全對應得上,所以必須考慮好AC和DC的幅度。

在這種情況下,采用交流耦合的方式比較常見,當然也可以直流耦合(一般情況下要用電阻分壓等方式來實現AC和DC的幅度相匹配)。

| 參數 | RS-422 | PECL | LVDS |

| 差分驅動輸出電壓 | ±2.5V | ±500~1000mV | ±250~450mV |

| 接收器輸入閾值 | ±100mV | ±200~300mV | ±100mV |

| 數據速率 | <30Mbps | >400Mbps | >400Mbps |

| 參數(以DS90C031/2為例) | RS-422 | PECL | LVDS |

| 電源電流四路驅動器(無負載,靜態) | 60mA | 32~65mA(Max) | 3.0mA |

| 傳輸延遲驅動器 | 11ns(Max) | 4.5ns(Max) | 3.0ns(Max) |

| 傳輸延遲接收器 | 30ns(Max) | 7.0ns(Max) | 5.0ns(Max) |

| 電源電流四路接收器(無負載,靜態) | 23mA(Max) | 40mA(Max) | 10mA(Max) |

| 畸變(驅動器或接收器) | N/A | 500ps | 400ps |

高速信號匹配和對接

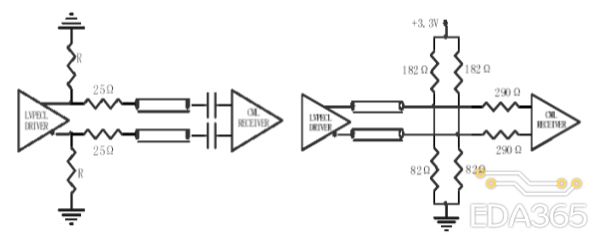

a LVPECL&LVPECL(PECL同理)

方式一:

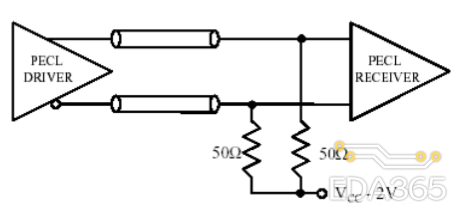

圖 1

圖 1 的匹配方式是 PECL電路的基本匹配模型,其中:2 個 50 歐姆的作用,既是交流匹配的電阻, 所以應該在離輸入端很近的地方,同時充當直流回路的偏置電阻。

由于是同一種電平對接, AC擺幅和DC電平當然沒有問題(符合下表):

缺點:

1、只有二個匹配電阻, 電阻個數最少, 但是二個電阻都必須靠輸入端比較近的地方放置, PCB布板可能有點困難。

2、最大的缺點就是需要 VCC-2V的電源,如果這種電路的路數很多,為此提供 VCC-2V還是可以的,如果路數不多,那么就不值得了。

經過演化變化成圖2。

方式二:

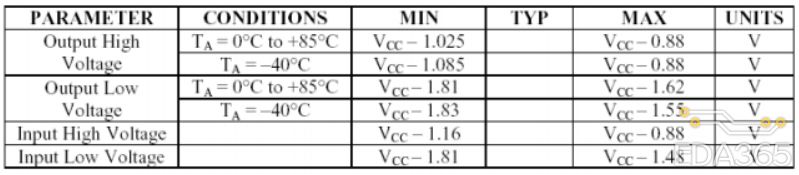

圖2

圖2 是從圖1 演化而來,R1=130,R2=82( 3v3);R1=82,R2=130( 5v)。其中 R1//R2 既充當交流匹配電阻( 50 歐姆),也充當直流偏置電阻。

缺點:

1、4個電阻都必須放在離輸入端很近的地方,對 PCB布板造成困難。

2、匹配電阻功耗比較大, 如果路數很多的話, 對單板的功耗來說是一個比較大的問題(靜態電阻很小) 。

在實際的布板過程中,我們并不提倡使用這種電路 。

方式三:

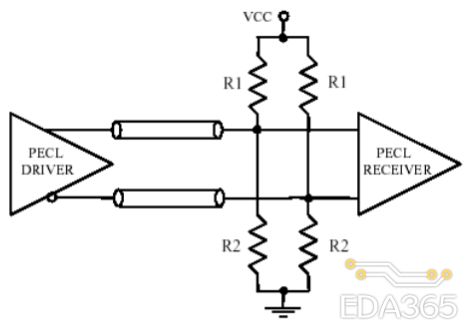

圖3

圖3 是一種資料上很少提,但是卻很有用的電路方式,其中 R1=140~200 歐姆( 3v3), R1=270~330歐姆( 5V), R2=100 歐姆。R1為輸出門提供偏置電流, R2 為交流信號提供匹配。輸入門的直流電平直接利用輸出門的直流電平,并不需要外來的上下拉電阻來提供。

優點:

1、電阻個數很少,只有 3 個。

2、只有 R2一個電阻必須放在離輸入門比較近的地方, R1放置的地方可以比較隨便,只要不引入過長的線頭(過長的線頭會導致反射)就可以了。

3、PCB布板比較容易處理。

這種電路的功耗比圖2小得多,是一個優選電路 。

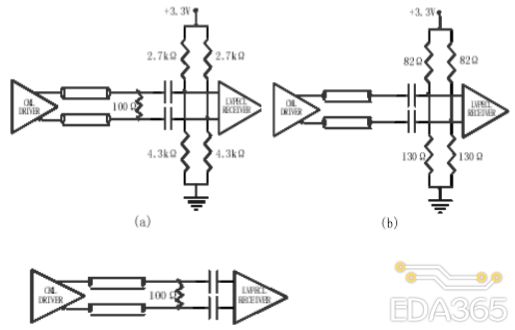

b LVPECL&PECL

對于 LVPECL和 PECL來說,雖然 AC 的擺幅相同( 800mV),但是直流電平不一樣,所以無法之間用 DC耦合對接起來。在這種情況下,我們可以考慮用 AC耦合方式來處理。

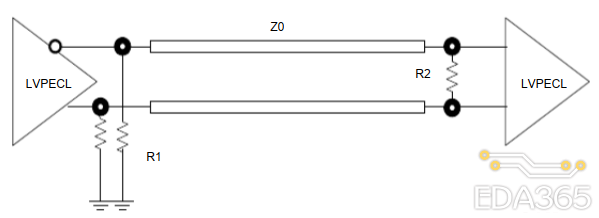

方式一:

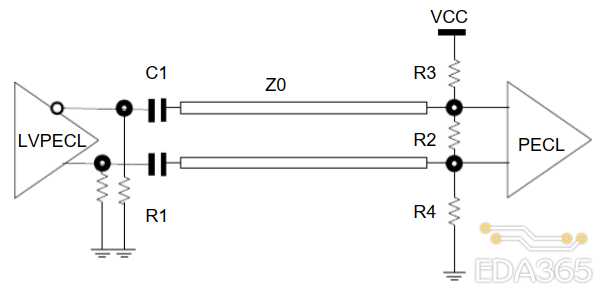

圖4

其中:R1=140~200 歐姆 屬于直流偏置電阻,C1為耦合電容, 可以放在線上的任何一個地方, 不一定在源端, 也不一定要在末端。R2=100 歐姆 屬于交流匹配電阻,一定要放在末端。

R3、 R4 為 K 級別的電阻, 必須滿足R4/(R3+R4)=(VCC-1.3V)/VCC的比值就可以了。R3/R4 是為輸入端提供直流電平,所以對 PCB上的位置沒有特殊要求,只需要不引入長線頭就可以了。

優點:

1、對于交流耦合來說,器阻容器件的個數算是比較少的了;

2、只對一個電阻的位置( R2)有要求,其他的沒有要求;

3、功耗也比較小。

4、當 LVPECL輸出沒有交流信號的時候,那么輸入端卻可以依靠 100 歐姆的電阻,使得 P/N 維持一個電壓差,從而保證輸入端的穩定(恒為“ 0”或者“ 1”)。

大家可以聯想到芯片 LOS信號的檢測機制――看輸入的信號是否為長“ 0”或者長“ 1”。為芯片的正確檢測 LOS提供了保證。而圖5 的匹配方式是無法解決這個問題的。該電路屬于優選電路類型。這種方式可以推廣到 LVPECL&LVDS;LVDS&LVPECL等電平的對接。

方式二:

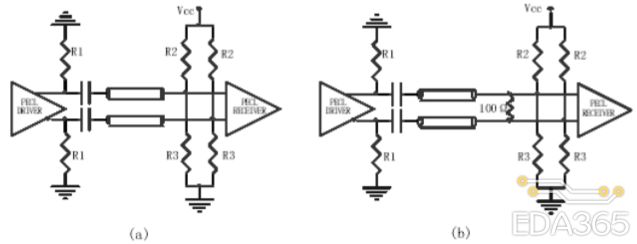

圖5

圖5 電路是很多資料推薦使用的, 從原理上分析沒有錯, 但是從實用的角度來說并不是最佳方案。

缺點:

1、電路( a)種的 R2/R3 既做為交流匹配電阻,又做為輸入直流電平,由于 R2/R3共 4 個電阻必須放在輸入引腳附近,所以可能導致 PCB布板困難。同時功耗也比較大。

2、電路( b)應該說有比( a)比較大的改進,雖然從電阻的個數上來說還多了一個,但是 PCB布板容易,并且功耗比較小。其 R2/R3 阻值可以是 K 級別的。

此方案不提倡使用。

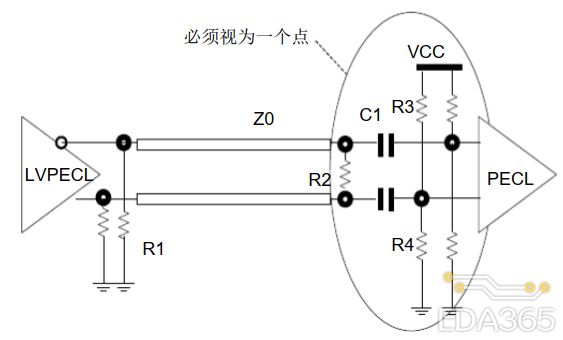

方式三:

圖6

圖6 從原理上來說也沒有錯,但是 R2/C1/R3/R4 等 7 個阻容必須放輸入端很近,布局相當困難,對于 PCB 布局來說還不如方式一和方式二。

此方案不推薦使用 。

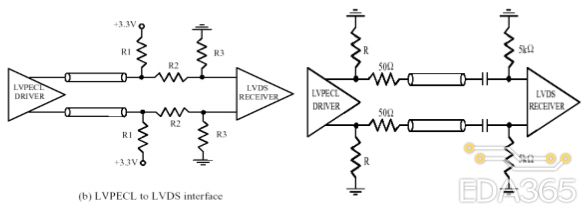

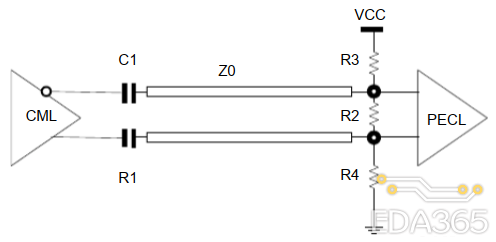

c LVPECL&LVDS

對于 LVPECL輸出, LVDS輸入的信號來說, LVPECL的直流輸出電平為 2V 左右,而 LVDS的直流輸入可以為 0.2V~2.2V, 所以直流電平本身不是關鍵。

對于交流電平來說 LVPECL輸出最大為 800mV,甚至超過 1V,而 LVDS的輸入交流電平一般不能承受 800mV 的輸入(具體還得看芯片資料的說明) ,一般是認為最大在 400mV 左右。

所以如何把交流幅度調整到 LVDS能夠接受的范圍才是關鍵。

圖 7

以上是 LVPECL到 LVDS的 DC和 AC二種耦合的示意圖。具體的電阻值請參考其他資料,自行計算。

d LVPECL&CML

對于 LVPECL輸出 CML 輸入的信號來說, LVPECL的輸出交流擺幅比較大,可能會超過 CML 電平的最大輸入擺幅,所以一般情況下應該加衰減,同時也要關注直流電平。同樣,有 AC耦合和 DC耦合二種。

圖 8

一般情況下, 二種不同直流電平的信號 (即輸出信號的直流電平與輸入需求的直流電平相差比較大) ,提倡使用 AC 耦合 ,這樣輸出的直流電平與輸入的直流電平獨立。

e CML&LVPECL

對于 CML 輸出, LVPECL輸入來說,由于直流電平相差很大,所以一般采用交流耦合方式。

而 CML輸出的交流幅度一般不會大于 LVPECL接收的交流幅度,所以交流方面只需要考慮匹配就可以了,不需要考慮幅度。有些資料提供的匹配電路圖如下:

圖 9

本人認為,圖( a)( b)存在圖5、圖6 所描述的相同弊病,最好采用如圖10 結構的電路 。同樣,圖( c)的 100 歐姆電阻放在電容后面對于 PCB布板來說更方便一些,從匹配的角度來說更好一些。

圖10

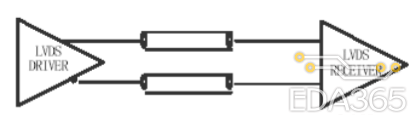

f LVDS&LVDS

應該說 LVDS之間的對接是最簡單的對接了。

圖 11

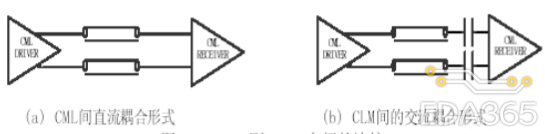

g CML&CML

圖 12

CML 電平一般情況下使用直流耦合就可以了。當然如果二個芯片的供電電源不同就必須用交流耦合了。因為此時二個芯片直接的直流電平不同, 不能直接對接。

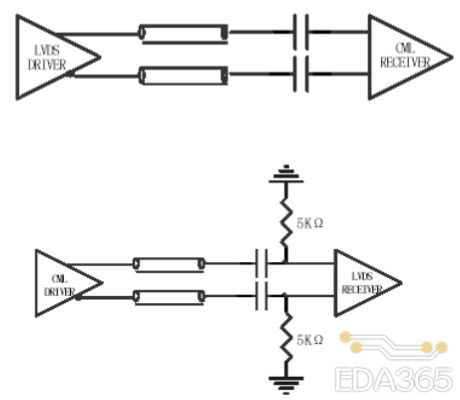

h LVDS&CML;CML&LVDS

一般情況下, 不會存在 LVDS與 CML 之間的對接, 因為 CML 電平一般用在高速信號,如 2.5G/10G 等場合。

而 LVDS一般很難用在那么高的速率。在這里要注意的是,輸出交流幅度是否落在輸入交流幅度之內

圖13

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8598瀏覽量

151157 -

DC

+關注

關注

9文章

3648瀏覽量

679689 -

AC

+關注

關注

1文章

588瀏覽量

84360 -

數字電路

+關注

關注

193文章

1605瀏覽量

80622 -

交流耦合

+關注

關注

0文章

32瀏覽量

12177

原文標題:高速數字電路設計通關五部曲(二):接口信號匹配與對接

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速數字電路設計:接口信號匹配與對接

高速數字電路設計:接口信號匹配與對接

評論