國香港城市大學(xué)Cheng Wang副教授、美國哈佛大學(xué)Marko Lon?ar教授和諾基亞貝爾實驗室的研究人員合作,利用納米微加工技術(shù)開發(fā)出一種微型、高效的新型鈮酸鋰電光調(diào)制器,與傳統(tǒng)電光調(diào)制器相比,其數(shù)據(jù)傳輸速度更快、能耗和成本更低,有望促進(jìn)5G產(chǎn)業(yè)的發(fā)展。相關(guān)工作以“Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages”為題,發(fā)表在《Nature》上。

背景介紹

電光調(diào)制器是現(xiàn)代通信產(chǎn)業(yè)的核心部件,用來將計算機設(shè)備中的高速電子信號轉(zhuǎn)化為光信號,從而能夠在光纖中實現(xiàn)信息的遠(yuǎn)距離高速傳輸;同時,它們還有望成為量子光子學(xué)和非互易光學(xué)等新興應(yīng)用的基礎(chǔ)模塊。所有這些應(yīng)用都要求使用芯片級的集成電光調(diào)制器,其工作電壓需要與CMOS半導(dǎo)體技術(shù)兼容,且具有超高的信號帶寬和非常低的光學(xué)損耗。盡管硅、磷化銦或聚合物等材料具有優(yōu)異的可擴展性和獨特的性能優(yōu)勢,但是目前為止基于這些材料的集成調(diào)制器還不能同時滿足所有期望性能的要求。

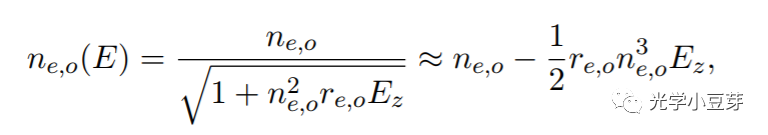

近年來,科學(xué)家發(fā)現(xiàn)鈮酸鋰(LiNbO 3 )材料具有極其優(yōu)異的電光特性,非常適合作為電光調(diào)制器的基礎(chǔ)材料,可同時實現(xiàn)調(diào)制器的超快速調(diào)制、低電壓操作和較低的光損耗要求。但是,鈮酸鋰微結(jié)構(gòu)的加工制備技術(shù)一直沒有較大的突破,限制其關(guān)鍵性能指標(biāo)的優(yōu)化,如降低了鈮酸鋰電光效率、增大了尺寸、減少了電場和光場之間的重疊、不利于微波信號的傳遞,使鈮酸鋰電光調(diào)制器一直難以集成在芯片上。此外,目前使用鈮酸鋰晶體制造的電光調(diào)制器需要3-5 V的驅(qū)動電壓,遠(yuǎn)高于互補式金屬氧化物半導(dǎo)體集成電路的1V電壓,從而使得整套設(shè)備需要加裝電流放大器,設(shè)備笨重、昂貴且耗能高。因此,同時實現(xiàn)鈮酸鋰調(diào)制器較低的開/關(guān)電壓、超高的帶寬和低光損耗仍是一個極具挑戰(zhàn)性的問題。

創(chuàng) 新 研 究

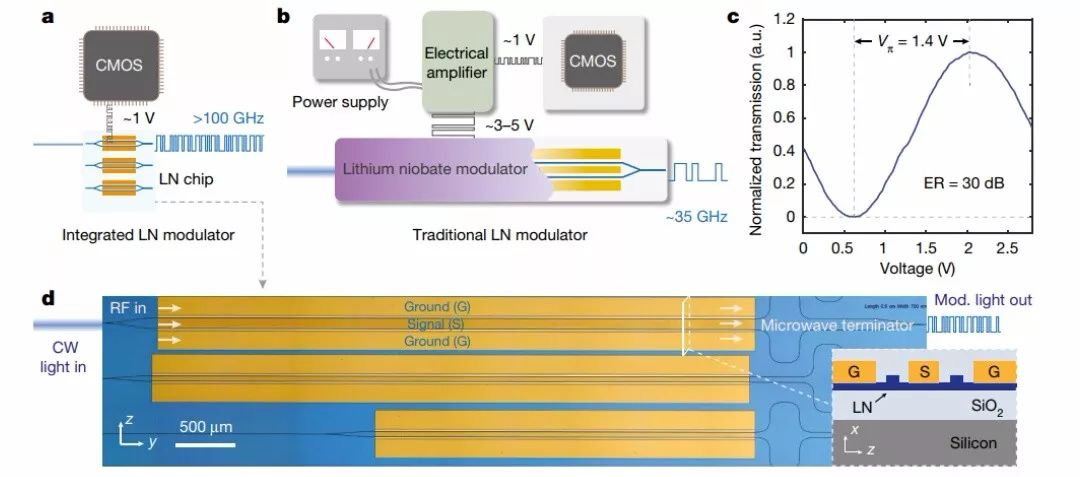

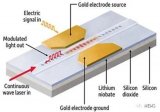

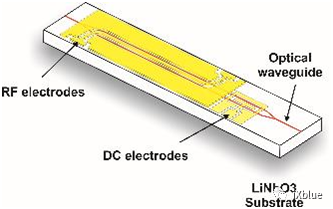

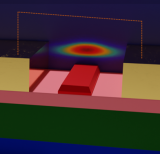

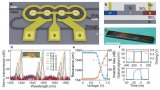

在這個研究中,研究人員首先設(shè)計了單片集成的鈮酸鋰電光調(diào)制器,如圖1所示。納米光子鈮酸鋰調(diào)制器(圖1 a)具有極高的帶寬(>100GHz),能夠直接用CMOS電壓驅(qū)動,而傳統(tǒng)調(diào)制器(圖1 b)需要較大、耗電的電驅(qū)動放大器,且只有有限的帶寬(大約35GHz)。圖 c是20 mm器件的歸一化光傳輸與施加電壓的函數(shù)關(guān)系,單片集成的鈮酸鋰電光調(diào)制器表現(xiàn)出1.4V的低開關(guān)電壓,消光比為30dB。單片集成的鈮酸鋰電光調(diào)制器由三個具有多種微波信號線寬和器件長度的Mach-Zehnder調(diào)制器組成(芯片顯微鏡圖1 d),薄膜型器件配置允許微波和光學(xué)器件之間的最大電磁場重疊和速度匹配。

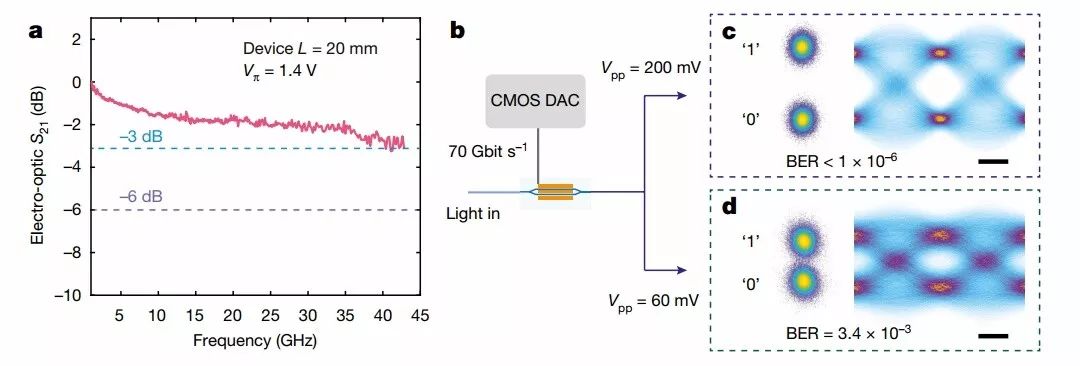

實驗中,研究人員使用CMOS電路直接驅(qū)動納米光子鈮酸鋰調(diào)制器。在有源調(diào)制長度為20 mm的器件中,小信號電光響應(yīng)(圖2a)顯示出大于 45 GHz的帶寬。他們使用集成電光調(diào)制器進(jìn)行數(shù)據(jù)調(diào)制(圖2b),CMOS DAC電路產(chǎn)生的高速電信號能夠直接驅(qū)動調(diào)制器而無需電子放大器,數(shù)據(jù)傳輸速率達(dá)到了70 Gbit/s。圖2c,d分別是來自相干接收器的測量星座圖(constellation diagrams)和眼圖(eye diagrams),在每個數(shù)據(jù)采樣時恢復(fù)輸出光場的幅度和相位。在驅(qū)動電壓Vpp =200 mV(圖2c),測得的誤碼率(BER)為1×10^-6^,調(diào)制器的能量損耗為0.37 fJ bit ^-1^ ;進(jìn)一步降低驅(qū)動電壓Vpp = 60 mV(圖2d),測得的誤碼率(BER)為3.4×10^-3^,調(diào)制器的能量損耗進(jìn)一步減小到37aJ bit ^-1^ 。整個數(shù)據(jù)傳輸系統(tǒng)的總能耗主要由片外組件決定,包括CMOS DAC、激光器、接收器設(shè)置和模數(shù)轉(zhuǎn)換器。在評估整個系統(tǒng)的能量消耗時,需要考慮整個系統(tǒng)。

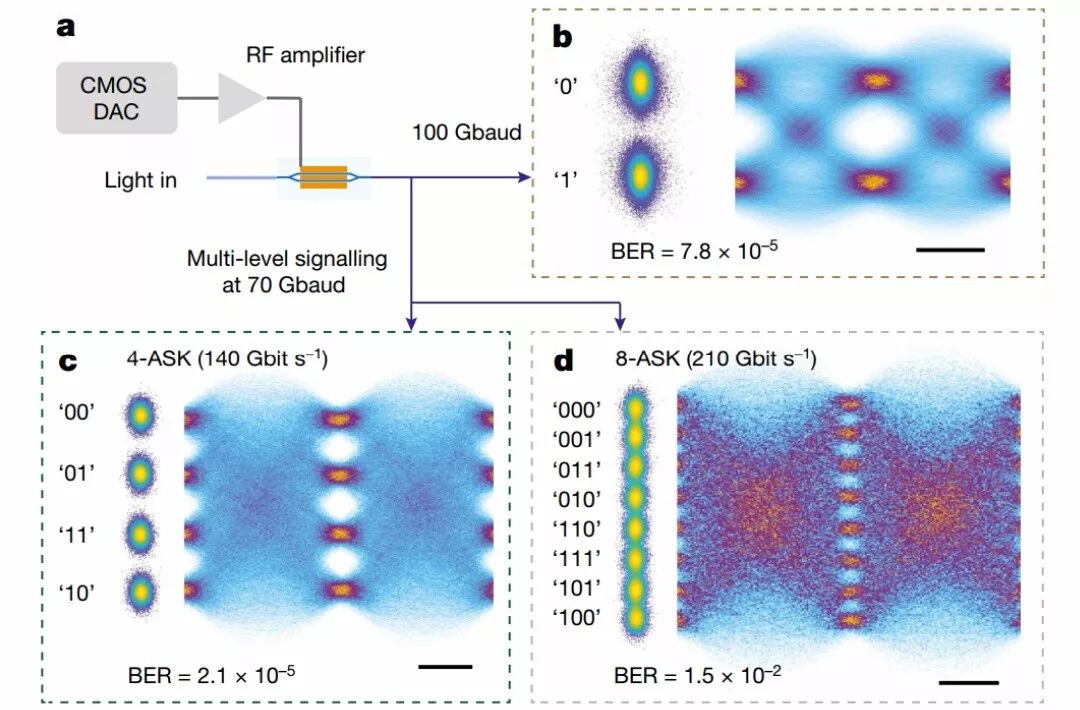

鈮酸鋰調(diào)制器具有較高的電光帶寬和優(yōu)異的信號保真度,可實現(xiàn)更高速率的數(shù)據(jù)傳輸,其數(shù)據(jù)帶寬達(dá)100 GHz,數(shù)據(jù)傳輸速度提升到每秒210千兆比特。 為實現(xiàn)這一目標(biāo),將來自CMOS DAC的電信號放大到約2.5 V(圖3a),驅(qū)動集成調(diào)制器。首先,以100 G baud的超高符號率生成二進(jìn)制信號,以測試調(diào)制器(圖3b)。在BER為7.8×10^-5 ^的情況下,受到電源高頻失真的限制:在100 G baud沒有任何光電互轉(zhuǎn)換下,BER是 3.6 × 10 ^?5^ 。然后,在70 Gbaud下,使用多級調(diào)制碼型來進(jìn)一步提高數(shù)據(jù)速率并查詢信噪比(signal-to-noise ratio,SNR)。在4 -ASK下,調(diào)制器數(shù)據(jù)傳輸速度為140 千兆比特,且誤比特率只有2.1 × 10^?5^。在8- ASK(每個符號3比特)下,調(diào)制器數(shù)據(jù)傳輸速度達(dá)210 千兆比特,且BER只有1.5 × 10^?2^。高消光比、低光損耗、線性光電響應(yīng)使得這些特性使調(diào)制器具有較高的信噪比。實驗進(jìn)一步表明,鈮酸鋰調(diào)制器實現(xiàn)了良好的信號保真度。

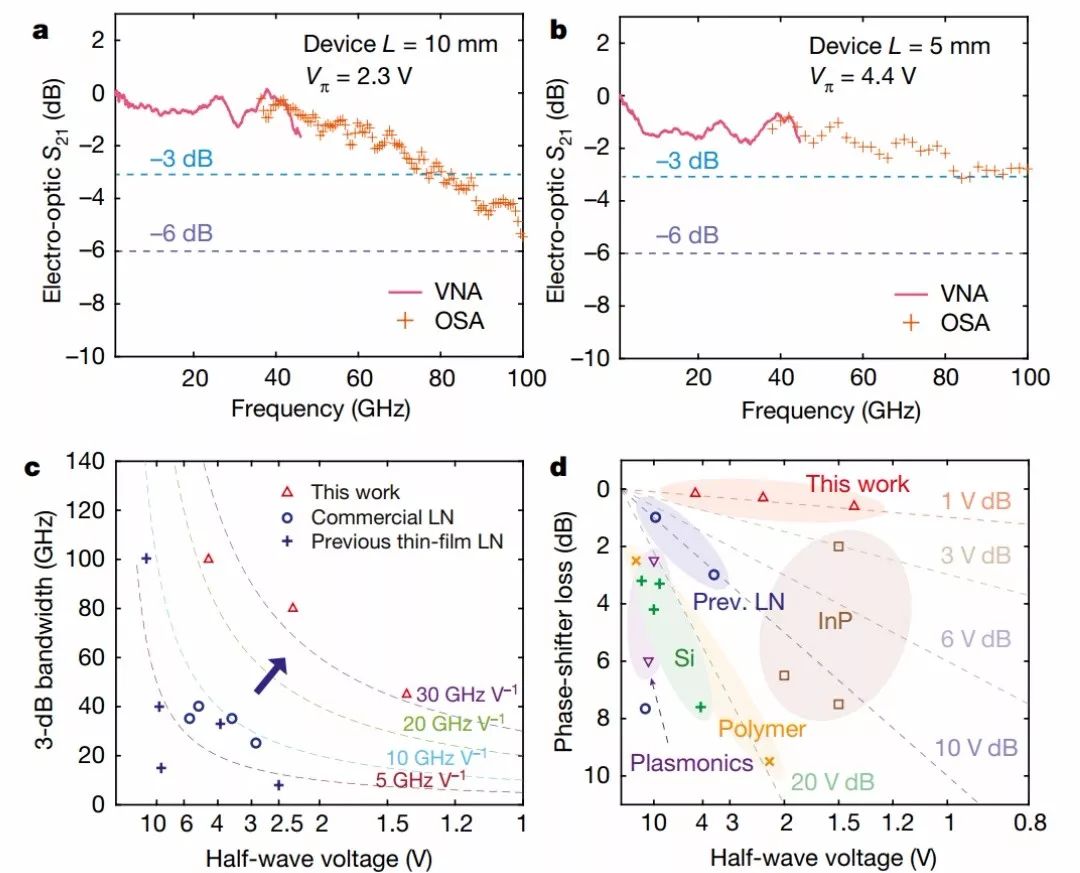

此外,集成的鈮酸鋰調(diào)制器平臺比傳統(tǒng)的鈮酸鋰調(diào)制器和其他材料平臺表現(xiàn)出整體性能(電壓、帶寬和光學(xué)損耗)極大地提高。通過將器件長度減小到10 mm和5 mm,進(jìn)一步將3 dB電光帶寬分別擴展到80 GHz和100 GHz(圖4a,b)。這些器件的測量半波電壓V π (half-wave voltage)分別為2.3 V和4.4 V。進(jìn)一步優(yōu)化傳輸線的微波損耗,可以在保持CMOS電平電壓的同時,實現(xiàn)大于100GHz的電光帶寬。納米級調(diào)制器比商用鈮酸鋰調(diào)制器和之前報道的薄膜鈮酸鋰器件表現(xiàn)出更好的電壓帶寬性能(約30 GHz V^-1^),如圖4c所示。這些調(diào)制器的超高帶寬可以使數(shù)據(jù)在超過200 Gbaud下操作。此外,此外,與其他高速調(diào)制器平臺相比,集成鈮酸鋰平臺打破了調(diào)制電壓和傳播損耗之間的傳統(tǒng)折衷,同時實現(xiàn)了低光學(xué)損耗和低V π (圖4d)。鑒于集成鈮酸鋰平臺的電壓損耗性能,應(yīng)該可以使用更長的器件進(jìn)一步將Vπ降至遠(yuǎn)低于1 V,同時保持片內(nèi)插入損耗低于1 dB。

結(jié)論

研究人員設(shè)計了具有CMOS兼容驅(qū)動電壓的單片集成鋰鈮酸電光調(diào)制器,其大小是傳統(tǒng)電光調(diào)制器的~1/100,可在1伏特電壓下工作,其數(shù)據(jù)帶寬達(dá)100千兆赫,數(shù)據(jù)傳輸速度提升到每秒210千兆比特,而光損耗只有現(xiàn)有器件的約十分之一。通過設(shè)計微波和光子電路,實現(xiàn)了調(diào)制器的高電光效率、超低光損耗和群速度匹配。可擴展的調(diào)制器器件可以為下一代光通信網(wǎng)絡(luò)和微波光子系統(tǒng)提供低成本、低功耗和超高速的解決方案。香港城市大學(xué)太赫茲及毫米波國家重點實驗室計劃將該技術(shù)用于5G通信應(yīng)用中,該技術(shù)在量子光子學(xué)領(lǐng)域也有著良好的應(yīng)用前景。

文章鏈接

https://www.nature.com/articles/s41586-018-0551-y

-

CMOS

+關(guān)注

關(guān)注

58文章

5729瀏覽量

235779 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27578瀏覽量

220528 -

調(diào)制器

+關(guān)注

關(guān)注

3文章

841瀏覽量

45215

發(fā)布評論請先 登錄

相關(guān)推薦

鋰離子電池的最新正極材料:摻錳鈮酸鋰?

電光調(diào)制器,電光調(diào)制器工作原理是什么?

AndyStrongIxblue公司鈮酸鋰調(diào)制器簡介

鈮酸鋰是迄今為止最小的電光調(diào)制器

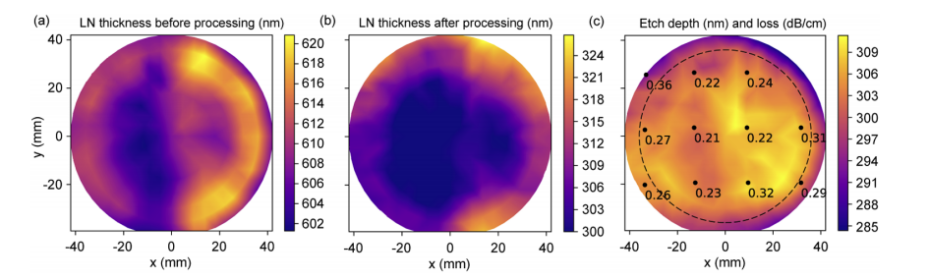

晶圓級低損耗鈮酸鋰光子集成電路

鈮酸鋰是用來做什么的

集成MZI電光調(diào)制器介紹

電光調(diào)制器偏壓控制器介紹

聊一聊鈮酸鋰調(diào)制器

稀缺半導(dǎo)體光電器件商,鈮酸鋰調(diào)制器芯片及器件打開成長空間.zip

一種薄膜鈮酸鋰電光相位調(diào)制器

基于薄膜鈮酸鋰的高性能集成光子學(xué)研究

基于鈮酸鋰的微型集成電光調(diào)制器

基于鈮酸鋰的微型集成電光調(diào)制器

評論