隨著互聯網的普及,手機逐漸成為我們的個人標配。手機的關鍵在于芯片,芯片的質量很大程度上決定了手機的性能,可是手機芯片為什么這么貴呢?

芯片就像手機的大腦,我們將輸入信號作為原材料輸入手機,通過改變芯片內部的走線、邏輯,就能對輸入信號實現不同的處理方式。 也正因此,手機芯片是當今集成度超高的元器件,別看它只有一個指甲蓋的大小,里面可是包含了數十億晶體管呢,蘋果的A15仿生芯片包含了150億個晶體管,每秒可執行15.8萬億次操作。 因此,無論是研發還是制造難度,大家都可想而知。

經常會有新聞講某某公司在芯片方面投了多少億,文檔君覺得好多好多錢呀,可是了解下去發現,這么多錢竟然只夠公司燒一年?今天我們就從芯片的研發與生產兩個方面來看看,手機芯片是如何產生的?為啥那么貴? 一款芯片從無到有,要經歷兩大階段:研發環節和制造環節。

芯片研發 芯片的研發流程大致可分為:

IP(知識產權)采購

前端設計

驗證

DFT(可測試性設計)設計

后端設計

封裝設計

回片測試

其中,前端設計、驗證、DFT設計、后端設計、封裝設計等過程需要大量的研發人員的人力投入和不同團隊的分工合作。

芯片制造 比起芯片的研發,芯片制造的難度更大,技術壁壘更高。 芯片的生產與制造可以大體分為晶圓制造、晶圓光刻顯影和刻蝕、摻加雜質和封裝測試四個步驟。 晶圓制造 晶圓是制造芯片的物質基礎,由石英砂精煉得來,晶圓是從99.99%的純硅圓柱體(也叫“硅錠”)上切下來的(以半導體制造中最常用的尺寸12寸為例,由于芯片的尺寸各不相同,從12英寸的晶圓上可分割出來幾十個到數千個芯片),并被打磨得極為光滑,然后再根據結構需求將導體、絕緣體或半導體材料薄膜沉積到晶圓上。當前我國具備一定的晶圓制造能力,基本上可以實現國產自用。

晶圓光刻顯影和刻蝕

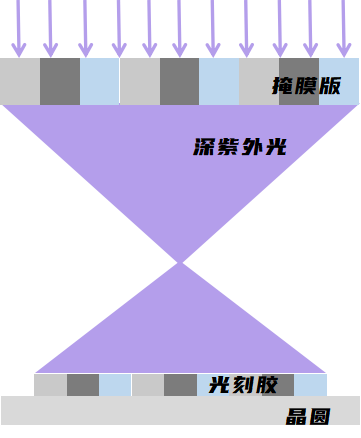

光刻技術決定了芯片上的晶體管可以做到多小。晶圓被放入***中,暴露在深紫外光(DUV)下。光線通過掩模版投射到晶圓上,***的光學系統(DUV系統的透鏡)將掩模版上設計好的電路圖案縮小并聚焦到晶圓上的光刻膠。

光刻膠,又稱光致抗蝕劑,是指通過紫外光、電子束、離子束、X射線等的照射或輻射,其溶解度發生變化的耐蝕劑刻薄膜材料。

當光線照射到光刻膠上時,會產生化學變化,將掩模版上的圖案印制到光刻膠涂層上。

刻蝕是為了去除退化的光刻膠,以顯示出預期的圖案。 在刻蝕過程中,晶圓被烘烤和顯影,光刻膠被洗掉,顯示出一個開放通道的3D圖案。 先進的刻蝕技術使芯片制造商能夠使用雙倍、四倍和基于間隔的圖案來創造出現代芯片設計的微小尺寸。像3D NAND這種高達175層的空腔結構的芯片設計,需要保證空腔深度完全正確,刻蝕過程格外困難。

通過***對指定位置進行刻蝕,這一過程極為精密和復雜,實際上世界上只有荷蘭 ASML 公司有能力制造昂貴的***,其 7nm ***售價高達 1 億美元 。

摻加雜質

摻加雜質可以增加立體結構復雜程度,越是復雜的集成電路,其立體結構就越復雜,摻加雜質的步驟也就越復雜。集成電路的基礎是 PN 結,要想形成 PN 結,就必須在不同的晶圓里摻加不同的雜質(本質上而言是加入 P、N 型雜質,改變其導電性質)。

PN結:采用不同的摻雜工藝,通過擴散作用,將P型半導體與N型半導體制作在同一塊半導體(通常是硅或鍺)基片上,在它們的交界面就形成空間電荷區稱為PN結。PN結具有單向導電性,是電子技術中許多器件所利用的特性,例如半導體二極管、雙極性晶體管的物質基礎。

封裝測試

在封裝過程中,為了把芯片從晶圓上取出來,要用金剛石鋸將其切成單個芯片。從晶圓上分割出來的芯片又稱為“裸晶”,隨后會被放置在“基板”上——這種基板使用金屬箔將裸晶的輸入和輸出信號引導到系統的其他部分。然后我們會為它蓋上具有“均熱片”的蓋子,均熱片是一種小的扁平狀金屬保護容器,里面裝有冷卻液,確保芯片可以在運行中保持冷卻。

經過上述流程,芯片制造商就完成了從版圖到芯片實體的流程,但芯片能否具體工作,其電氣性能是否達標,還需要完成測試才能確定。

因此,芯片制造廠商均需要一批后端測試人員對芯片的性能進行測試。

當然,半導體制造涉及到的步驟遠不止這些,芯片還要經過測量檢驗、電鍍、測試等更多環節,每塊芯片在成為電子設備的一部分之前都要經過數百次這樣的過程。

研發成本 了解了芯片的研發和制造過程,文檔君帶大家繼續了解一下芯片為啥這么燒錢呢?

芯片的研發成本主要包含IP采購、前端設計、驗證、DFT設計、后端設計、封裝設計、回片測試等部分費用。

IP采購

IP采購是芯片研發中不可忽視的一個環節。 費用模式通常分為一次性授權、產品單獨授權,或者兩者疊加起來。

例如,手機處理器芯片、AI芯片等都需要集成CPU模塊,目前國內大部分芯片設計公司都采購ARM的CPU核。 IP核,全稱知識產權核 (intellectual property core),是指某一方提供的、形式為邏輯單元、芯片設計的可重用模塊。

回片測試 回片測試包含測試硬件、RA(Reliability Test,可靠性測試)實驗、ATE(Automatic Test Equipment,集成電路自動測試設備)機臺使用以及研發人力投入等成本。

其他 前端設計、驗證、DFT設計、后端設計、封裝設計支出主要以研發人員的人力投入為主,此外還包含EDA軟件的使用費、FPGA和Zebu等驗證平臺的硬件費用。

生產成本 芯片生產成本主要包括流片、晶圓、CP(Chip Probe,晶圓)測試、封裝、FT(Final Test,最終測試)、SLT(System Level Test,系統級測試)等,其中大部分集中在流片和晶圓。

流片成本

流片,是指像流水線一樣通過一系列工藝步驟制造芯片,在集成電路設計領域,“流片”指的是“試生產”。

一次性費用,按照掩膜版層數計算。 在芯片設計完成后,會生產復雜的圖形文件,一般來說會有幾十層到上百層。這些圖形文件需要在光罩廠做掩膜版。 工藝節點越高,流片價格越貴,因為高工藝需要更多的掩膜版。在16 nm制程上,需要大約60張,而7nm可能就需要上百張。

目前最便宜的ASIC流片成本也需要幾十萬一次,180nm的流片成本大概是50萬元,55nm的成本約200萬元。但是16nm的成本就飆升到了3000萬-5000萬元,到了7nm最低也要過億。

但到了量產階段,尤其是產品的出貨量比較大,一次性流片費用平攤到數十萬顆芯片上時,相對成本就低了很多。

晶圓成本

按照出貨片數每片計算。

晶圓價格也是按照工藝節點區分的。臺積電12寸晶圓40nm成本每片大約在1500~2000美元,16nm成本每片大約在4000~5000美元之間,7nm成本每片大約在9300美元左右,5nm代工價格約為17000美元,3nm價格預計會達到30000美元左右。

審核編輯:劉清

-

晶圓

+關注

關注

52文章

5076瀏覽量

128983 -

晶體管

+關注

關注

77文章

9907瀏覽量

140144 -

DFT

+關注

關注

2文章

232瀏覽量

23151 -

半導體二極管

+關注

關注

0文章

36瀏覽量

10817

原文標題:手機芯片為啥這么燒錢?

文章出處:【微信號:ztedoc,微信公眾號:中興文檔】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論