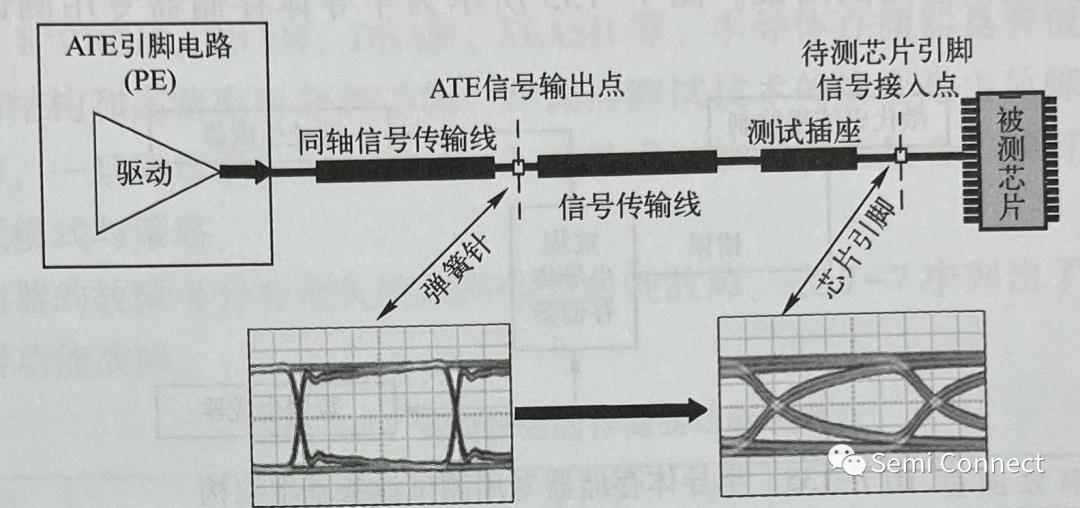

隨著集成電路技術(shù)的發(fā)展,高速信號的設(shè)計技術(shù)指標不斷更新,系統(tǒng)中的數(shù)據(jù)傳輸速率已經(jīng)提高到數(shù)十 Gbit/s 乃至數(shù)百 Gbit/s,這就給測試系統(tǒng)、測試硬件設(shè)計、測試信號傳輸質(zhì)量等帶來了新的挑戰(zhàn)和更高的難度。我國采用的通用方案是通過誤碼率測試分析對高速接口電路性能進行評價,但這種方法測試效率低,且無法系統(tǒng)、全面地評價高速接口的電平和時序特性,以及可靠性等。高效、系統(tǒng)性的測試評價方案是應(yīng)用自動測試裝備 (ATE),結(jié)合高端 ATE 的高質(zhì)量資源、砂件設(shè)計技水及測試算法開發(fā),不儀可以保證高速信號測試位輸?shù)馁|(zhì)量,還可以實現(xiàn)對高速信號芯片智能化,自動化的全面性測試評估。圖所示的是高速信號從ATE輸出端到被測芯片引腳的變化。

通常,測試中評價高速信號的參數(shù)包括誤碼率(BER)、眼圖(EveDiagram)、電壓擺幅(Voltage Swing)、共模電壓 (Gommon Mode Voltage)、輸出偏斜 (Output Skew)、抖動(Jitter) 等。評價高速串行數(shù)據(jù)傳輸端口特性的主要參數(shù)如下所述。

(1) 高速端口電壓特性參數(shù):主要包括共模輸人電壓范圍、差模輸人電壓范圍.預加重電壓和去加重電壓的幅度、共模輸出電壓、端口漏電。

(2)高速端口時間特性參數(shù):主要包括高速信號的頻率范圍、輸出信號的上升/下降時間、發(fā)送/接收時延。

(3)傳輸可靠性特性參數(shù):主要包括本地時鐘抖動容限、高速串行信號輸人抖動容限和高速串行信號輸出抖動幅度。

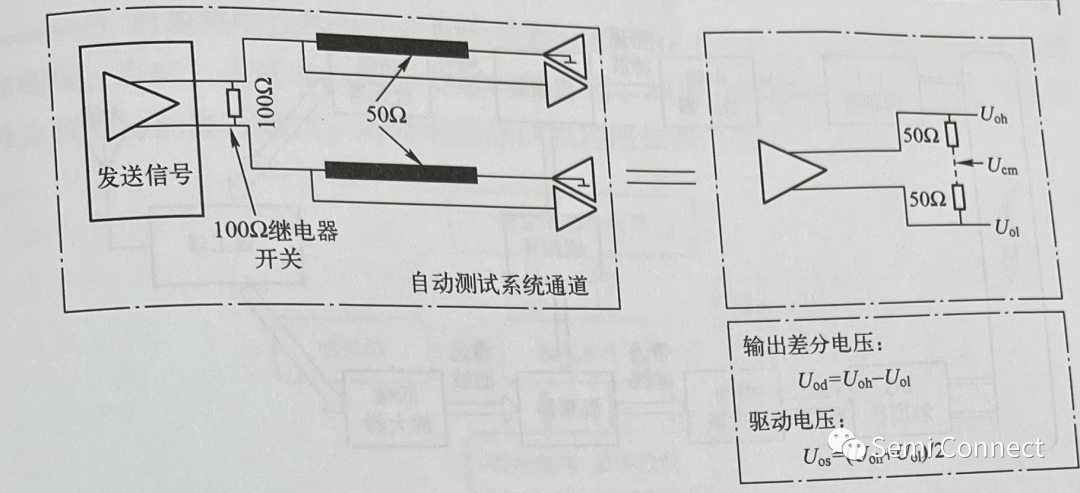

進行高速信號測試時,為解決低電壓差分信號 (Low Voltage DifferentialSignals, LVDS)的測試難點,可以將自動測試系統(tǒng)的兩個差分通道 (DifferentialChannel)與待測芯片的發(fā)射端或接收端相連,并在待測芯片附近設(shè)計 100Ω的電阻作為終端。圖所示的是典型 LVDS 發(fā)射芯片測試方案。

日前,主流高速信號集成電路測試系統(tǒng)驅(qū)動電平的精度可達 10mV,比較器的最小過驅(qū)動(Overdrive) 電平為 50mV,可以滿足 LVDS 高速小信號測試的要求。但末來下一代超高速信號將會給測試帶來更多的挑戰(zhàn),需要從新波形和系統(tǒng)設(shè)計仿真、頻譜和信號分析、光通信和高速測試等方向研發(fā)更加靈活、可靠的測試方案,以期獲得準確、穩(wěn)定的測試結(jié)果。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

455文章

50816瀏覽量

423673 -

集成電路

+關(guān)注

關(guān)注

5388文章

11547瀏覽量

361834 -

測試系統(tǒng)

+關(guān)注

關(guān)注

6文章

822瀏覽量

62133 -

眼圖

+關(guān)注

關(guān)注

1文章

67瀏覽量

21136 -

高速信號

+關(guān)注

關(guān)注

1文章

226瀏覽量

17699

原文標題:高速信號集成電路測試,高速信號積體電路測試,High Speed IC Test

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

集成電路應(yīng)用電路識圖方法

電子元器件基礎(chǔ):集成電路應(yīng)用電路識圖方法

集成電路應(yīng)用電路識圖方法分享

集成電路應(yīng)用電路圖的功能和識圖方法

集成電路可測性設(shè)計方法

集成電路電磁騷擾測試方法

集成電路型號命名方法

大規(guī)模集成電路相關(guān)測試標準

高速信號集成電路測試方法

高速信號集成電路測試方法

評論