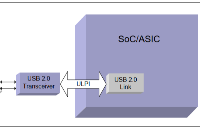

基于DWC2的USB驅動開發-0x09 ULPI接口協議其他工作模式介紹 (qq.com)

ULPI(其他工作模式介紹)

1.1 前言

上一篇講解了ULPI基本的一些概念,這一篇就重點講解其具體的工作模式,同步模式是重點內容比較多放在下一篇,這一篇先講其他模式。

1.2 低功耗模式

當USB總線掛起時,LINK可以選擇性地將PHY置于低功耗模式。PHY可以關閉除接口引腳和全速接收器之外的所有電路。如果存在VBUS,總線電阻器也必須通電。如果設置了相應的寄存器位,則對應功能都必須通電,包括中斷源和電荷泵。如果PLL斷電,則必須停止時鐘而不出現毛刺。

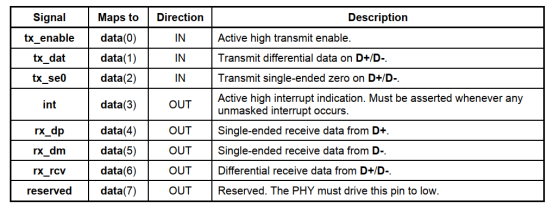

1.2.1 低功耗模式的Data線重定義

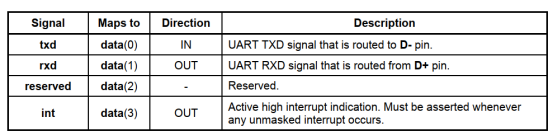

當處于低功耗模式時,PHY使用下表中列出的信號驅動數據線(3:0)。當處于低功耗模式時,必須從FS接收器組合驅動LineState。

每當發生任何未屏蔽的中斷時,都會使得int引腳信號有效。

PHY必須直接從模擬電路鎖存中斷事件,因為時鐘已斷電。

LINK忽略8位數據總線的數據位(7:4)的信號。

輸入時鐘和輸出時鐘模式都必須遵循這些規則。

| 信號 | 映射到 | 方向 | 描述 |

|---|---|---|---|

| nestate(0) | data(0) | OUT | LineState(0) 由FS 模擬接收器直接驅動。 |

| nestate(1) | data(1) | OUT | LineState(1) 由FS 模擬接收器直接驅動。 |

| reserved | data(2) | OUT | 保留,PHY必須拉低該引腳。 |

| int | data(3) | OUT | 高有效,有未屏蔽中斷時PHY拉高該引腳。 |

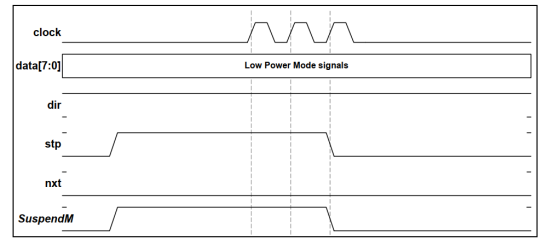

1.2.2 進入低功耗模式

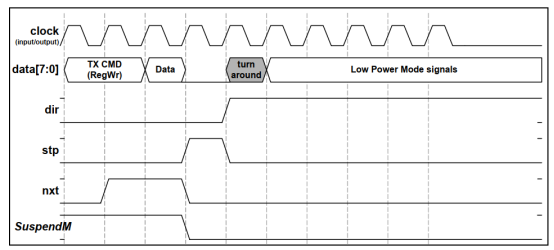

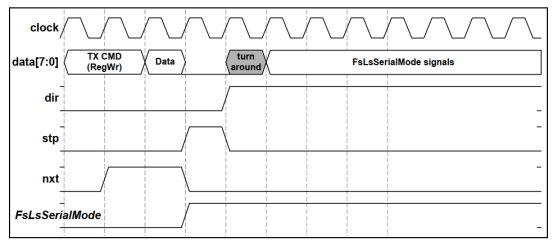

LINK寫Function Control 寄存器的SuspendM 為0b使得PHY進入低功耗模式。

如圖所示LINK或PHY時鐘可以在PHY接受寄存器寫入數據后至少停止五個周期。

當處于低功耗模式時,PHY拉高dir,并保持nxt為低。

在拉高dir之后,提供了一個數據總線周轉周期turn around,在此期間,數據上的值無效。

PHY在turn around周期之后立即開始按照低功耗模式的Data線重定義信號驅動data[3:0]。

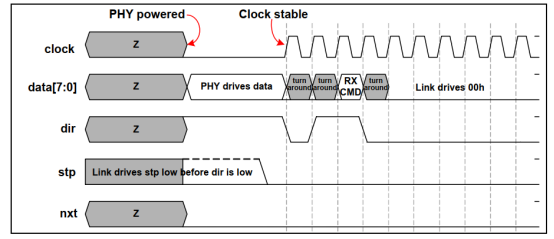

1.2.3 退出低功耗模式

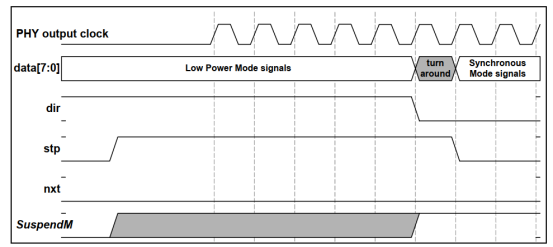

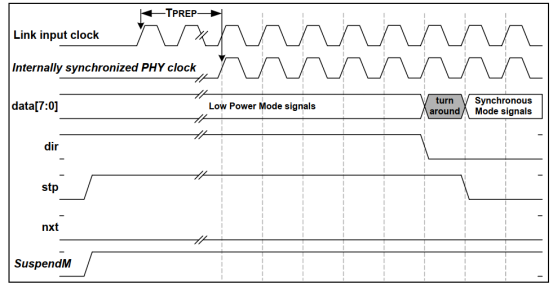

如圖所示,LINK通過異步拉高stp向PHY發出退出低功率模式的信號。PHY立即開始喚醒其內部電路。當PHY時鐘滿足ULPI時序要求時,PHY拉低dir。PHY必須確保在拉低dir之前至少驅動了5個時鐘周期。PHY還必須確保在拉低dir之前將SuspendM寄存器自動設置為1b。

LINK在檢測到dir拉低的一個CLK之后,拉低stp。

在拉低dir之后,提供了一個數據總線周轉周期turn around,在此期間,數據上的值無效。

PHY在turn around之前立即停止按照低功耗模式的Data線重定義信號驅動data[3:0]。

當LINK提供輸入時鐘時,PHY必須在TPREP內同步其內部時鐘TPREP是實現相關的。

PHY提供輸出時鐘時的退出低功耗

LINK提供輸入時鐘時的退出低功耗

1.2.4 拒絕虛假恢復

由于USB環境的噪聲,可能導致低功耗模式下PHY驅動的異步LineState 輸出,有短暫的non-J-state條件或者毛刺。

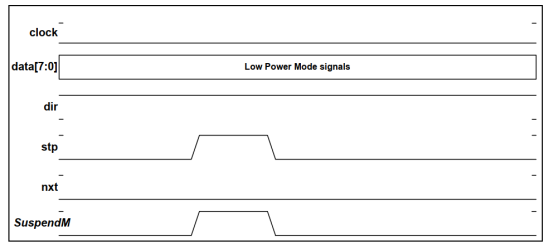

LineState上的毛刺可能導致LINK短暫的拉高stp,這應該要認為是虛假的恢復PHY必須拒絕這個事件。PHY可以在重新啟動時鐘之前選擇性地拒絕stp上的毛刺,如圖所示。PHY必須通過在PHY拉低dir時在時鐘的邊沿去檢查stp是否拉高,來確定是否滿足退出低功耗模式的條件。

如果在dir被拉低的周期中stp沒有被拉高,那么PHY必須重新拉高dir并返回到低功率模式,而無需LINK的進一步操作,如圖所示。

1.3 全速/低速串行模式(可選)

全速/低速串行模式(FsLsSerialMode)使LINK能夠直接訪問FS/LS串行模擬收發器。

ULPI中定義了兩種類型的串行模式:3p FsLsSerialMode和6p FsL sSerialmode。

這兩種模式都是可選的。與低功率模式不同,FS/LS收發器必須通電。

如果設置了相應的寄存器位,則對應功能都必須通電,包括中斷源和電荷泵。

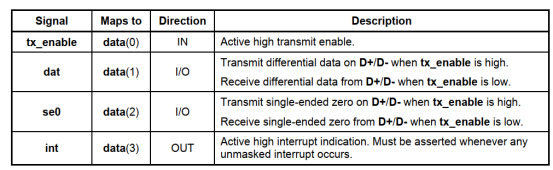

1.3.1 FsLsSerialMode的數據線重定義

6p串行模式為UTMI+中定義的每個串行信號提供一條單獨的數據線。3p串行模式將USB接收和傳輸數據壓縮到雙向數據線上,并提供4位數據總線PHY實現可以支持串行信號。

在任一模式中,UTMI+的低有效tx_enable_n信號被轉換為高有效tx_enable,用于在ULPI總線上傳輸,這允許默認的ULPI總線空閑狀態保持在00h。

在兩種串行模式中,都提供了一個中斷引腳。只要發生未屏蔽的中斷事件,就會拉高int引腳。

當處于6p串行模式時,PHY使用下表中列出的信號驅動數據(7:0)。

當處于3p串行模式時,PHY使用下表中列出的信號驅動數據(3:0)。

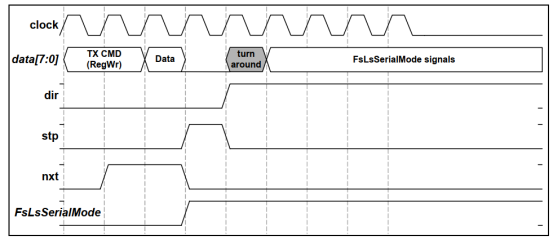

1.3.2 進入FsLsSerialMode模式

為了進入6p串行模式,LINK在接口控制寄存器Interface Control中設置6-Pin FsLsSerialMode位,使數據總線切換到異步操作,并采用新的總線數據定義。

為了進入3p串行模式,LINK在接口控制寄存器Interface Control中設置3-Pin FsLsSerialMode位,使數據總線切換到異步操作,并采用新的總線數據定義。

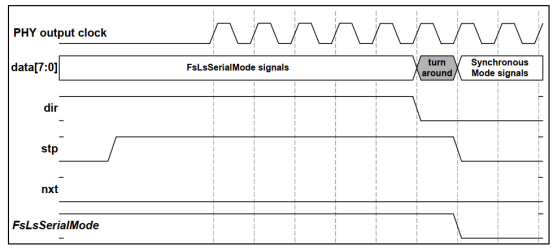

默認情況下,輸出時鐘斷電以減少串行模式下的功耗,如圖所示。進入串行模式后至少5個時鐘周期后,時鐘停止,當時鐘不可用時,PHY必須拉高dir。在拉高dir之后,提供了一個數據總線周轉周期turn around,在此期間,數據上的值無效。PHY在周轉周期之后立即開始驅動串行模式信號。

如果LINK要求時鐘在串行模式下運行,它可以在進入串行模式之前在接口控制寄存器Interface Contro中設置ClockSuspendM信號,如圖所示。

1.3.3 退出FsLsSerialMode模式

當LINK檢測到int為高時,它應該通過拉高stp來退出FsLsSerialMode。

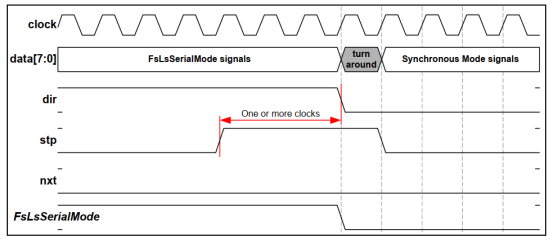

當ULPI接口返回同步模式時,LINK可以讀取USB中斷鎖存寄存器USB Interrupt Latch以確定中斷源。如果時鐘未運行,退出FsLsSerialMode與退出低功率模式相同,如圖所示。

如果時鐘正在運行,則LINK通過拉高stp向PHY發出退出FsLsSerialMode的信號。

PHY在檢測到stp拉高后將拉低dir 1個或多個周期,如圖所示。在拉低dir之后的一個時鐘中,LINK取消拉高stp。與低功率模式一樣,在取消拉高dir之后的周期中,有一個時鐘的總線數據周轉周期,在周轉周期內,數據上的值無效。PHY在緊接周轉周期之前停止驅動串行模式信號。

1.4 Carkit模式(可選)

當設置接口控制寄存器Interface Control中的CarkitMode位時,選擇該模式。

它允許LINK使用UART信號通過PHY與遠程車載套件進行通信。

默認情況下,當PHY進入Carkit模式時,時鐘會斷電。進入和退出Carkit模式與串行模式相同。如果LINK要求時鐘在Carkit模式下運行,它可以在進入Carkit模式之前在接口控制寄存器Interface Control中設置ClockSuspendM信號。

只要發生未屏蔽的中斷事件,就會拉高int引腳。當LINK檢測到int為高時,它應該通過拉高stp來喚醒時鐘(如果斷電)。如果時鐘已經在運行,LINK拉高stp一個周期,將接口切換到同步模式。

當PHY處于同步模式時,LINK可以讀取Carkit中斷鎖存寄存器Carkit Interrupt Latch以確定中斷源。

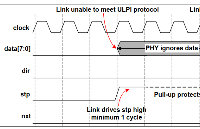

1.5 保護PHY輸入信號

由于包括但不限于硬件復位或緩慢通電的原因,LINK可能無法正確驅動ULPI接口。在這種情況下,當PHY的dir拉低時,LINK無法將數據驅動到空閑00h狀態。PHY數據輸入信號上的未知值可能會啟動未經請求的USB活動、寄存器寫入、串行或Carkit傳輸。

因此,PHY必須始終保護其數據輸入。

為了防止數據輸入上的錯誤命令,PHY必須在stp上包含一個弱上拉電阻器。

任何時候stp出乎意料地高,PHY都認為LINK無法驅動接口,并且必須進入保持狀態。

當處于保持狀態時,PHY不得使用數據上的命令,并且不得拉高dir,除非其內部時鐘不穩定。LINK還被允許在任何時候將stp驅動為高電平,從而迫使PHY停止使用數據上的命令。

當PHY處于保持狀態時,它可以選擇性地在數據上啟用弱下拉電阻器,防止它們浮動。

當PHY處于保持狀態時發生的所有RXCMD更改必須用單個RX CMD更新來替換,當ULPI總線可用時,PHY退出保持狀態時發送該更新。RX CMD更新必須始終傳達當前RXCMD值,而不是以前或舊的值。

如果LINK始終可以將stp和數據驅動到已知值,則可以通過將接口控制寄存器Interface Control中的接口保護禁用位Interface Protect Disable設置為1b來禁用保護功能,這會降低功耗。

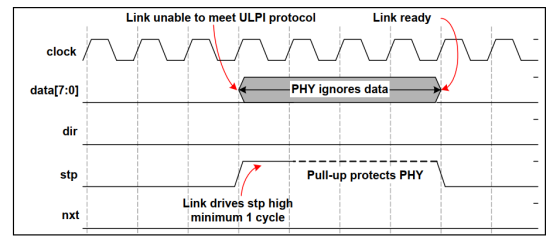

當時鐘運行時,LINK應在停止驅動ULPI接口之前將stp驅動高至少一個時鐘周期,迫使PHY進入保持狀態以保護其數據輸入。PHY中的上拉將在隨后的周期中保持stp為高,如圖所示。

對于LINK在停止驅動ULPI接口之前無法將stp驅動為高電平的實現,無法保證PHY操作的安全性。

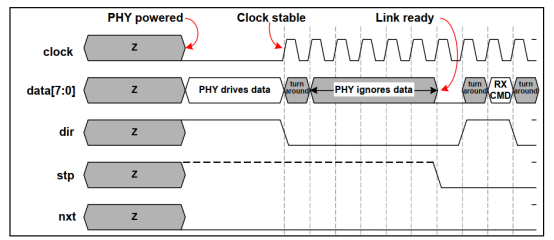

在通電期間或時鐘未運行時,PHY始終拉高dir,以保護其數據輸入,如圖所示。如果當PHY拉低dir時stp為高,則PHY將立即進入保持狀態并保護其數據輸入。當LINK將stp驅動為低時,PHY立即開始處理其數據輸入。

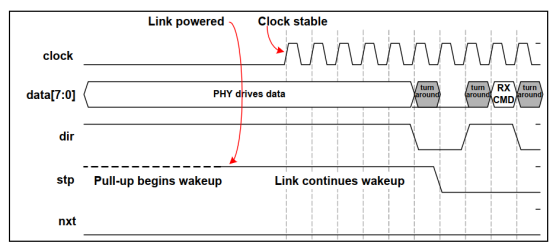

如圖所示,如果當LINK停止驅動ULPI接口時PHY處于低功耗模式,則stp上的上拉將自動喚醒PHY。如果LINK不希望PHY自動喚醒,則它必須將stp驅動為低電平。

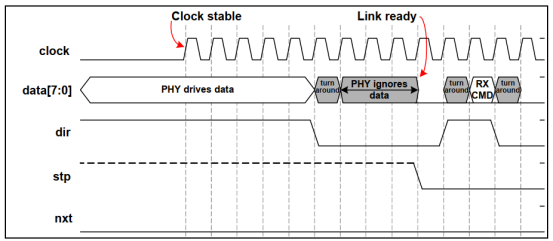

如果當LINK恢復驅動ULPI接口時dir為高,則LINK應當假定PHY處于低功率模式并且驅動stp為高以喚醒PHY,如圖所示,在拉低dir之后的時鐘中,LINK拉低stp。當dir和stp都為低電平時,PHY在當前時鐘周期中開始處理其數據輸入。這也適用于通電期間。

如圖所示,當dir為高時,LINK可以在通電期間將stp驅動為低電平。

當dir被拉低時,PHY在周轉周期之后開始處理其數據輸入。

1.6 總結

本篇講解了低功耗,全速/低速串行模式,Carkit模式,以及PHY輸入信號的保護處理。其中低功耗模式是必須的,其他的是可選實現的。

1.7 參考

《UTMI+ Low Pin Interface (ULPI) Specification Revision 1.1 October 20, 2004》

《MicroChip AN 19.17 ULPI Design Guide》

審核編輯:湯梓紅

-

接口協議

+關注

關注

5文章

41瀏覽量

18541 -

接口

+關注

關注

33文章

8596瀏覽量

151147 -

usb

+關注

關注

60文章

7945瀏覽量

264639 -

總線

+關注

關注

10文章

2881瀏覽量

88082 -

電荷泵

+關注

關注

3文章

238瀏覽量

29589 -

DWC2

+關注

關注

0文章

35瀏覽量

131

發布評論請先 登錄

相關推薦

基于DWC2的USB驅動開發-0x02 DWC2 USB2.0 IP功能特征介紹

基于DWC2的USB驅動開發-0x0D PHY寄存器讀寫代碼編寫與測試

基于DWC2的USB驅動開發-0x0E 使用邏輯分析儀分析ULPI數據

基于DWC2的USB驅動開發-高速設備枚舉為全速設備問題案例分析

基于DWC2的USB驅動開發-發送相關的寄存器DMA寄存器詳解

基于DWC2的USB驅動開發-0x0A ULPI接口同步模式介紹

基于DWC2的USB驅動開發-抽絲剝繭再論切換到狀態階段標志DOEPINTn.StsPhseRcvd

基于DWC2的USB驅動開發-0x09 ULPI接口協議其他工作模式介紹

基于DWC2的USB驅動開發-0x09 ULPI接口協議其他工作模式介紹

評論