鎖存器:組合電路與時序電路的橋梁

在網上看到一個帖子說了這樣一個說辭,我覺得很不錯,分享給大家:鎖存器不就是組合邏輯電路與時序邏輯電路的橋梁么?

其實仔細想想也是,之前功利性的學習根本沒有仔細考慮為什么拿到數電基礎的書后,目錄設計總是按照組合邏輯、鎖存器、時序邏輯去安排章節。

現在思考后我覺得很有道理(聽我開始瞎掰)最初數字電路的組合邏輯解決了很多問題,但是卻沒有很好的解決如何將這個狀態做存儲,有些設計情況下不得不將一些信號的狀態存儲,所以就使用邏輯門構建了鎖存器的概念,設計的靈活性得到進一步提升,但是同時又存在了另外一個問題,鎖存器就像一個閥門,但是由于這個閥門打開后內部是隨時可以變化的,這也給如何檢驗設計的正確性帶來了難度,所以急需一個器件或者設計去解決這個問題,進而有了時序邏輯電路中觸發器的概念,觸發器也就隨著 “需求和發展” 出現。

因此,組合邏輯、鎖存器、時序邏輯,這樣安排更像說明了數字電路的發展和迭代的歷史,雖然鎖存器的一般內容比較少,但不可否認,鎖存器就是組合邏輯電路與時序邏輯電路的橋梁。

鎖存器概念

鎖存器( latch)是電平觸發的存儲單元,數據存儲的狀態取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

鎖存器不同于觸發器,鎖存器在不鎖存數據時,輸出端的信號隨輸入信號變化,就像信號通過一個緩存器一樣;一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。因此鎖存器也稱為透明鎖存器, 指的是不鎖存時輸出對輸入是透明的。

鎖存器的分類包括 RS 鎖存器、門控 RS 鎖存器和 D 鎖存器, 此處介紹下 D 鎖存器。

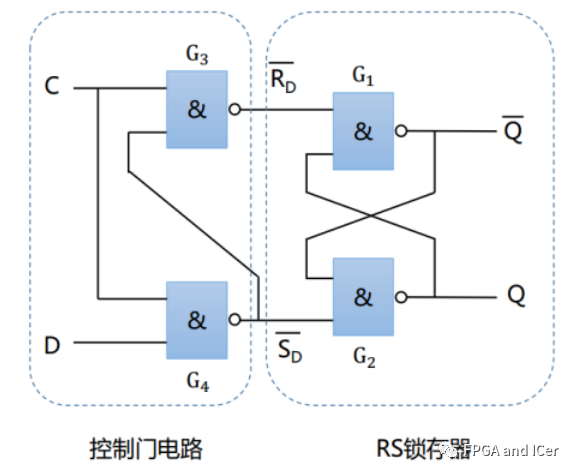

D 鎖存器就是能夠將輸入的單路數據 D 存入到鎖存器中的電路,D鎖存器的電路圖如下圖所示。

從 D 鎖存器的電路圖中可以看出,該電路主要是由兩個部分組成,第一個部分是由 G1、 G2兩個與非門組成的 RS 鎖存器,第二個部分是由 G3、 G4 兩個與非門組成的控制電路。C 為控制信號,用來控制 G3 和 G4 的激勵輸入。

下面來分析下 D 鎖存器的工作原理:

當控制信號 C=0 時,根據與非門的邏輯定律,無論 D輸入什么信號, RD 和 SD 信號都會輸出為1。RD 和 SD 都同時等于 1 的話,鎖存器的輸出端 Q 將維持原狀態不變。

當控制端 C=1 時,如果此時 D=0,SD 就等于1, RD 就等于 0,根據 RS 鎖存器的邏輯規律,電路的結果就為 0 狀態;如果 D =1,那么 RD 就等于 1,SD 也就等于 0,鎖存器的結果就為 1 狀態,也就是說,此時鎖存器的狀態是由激勵輸入端 D 來確定的,D 等于什么,鎖存器的狀態就是什么。

根據上面的描述,可以推出 D 鎖存器的特性表, Qn 是指觸發器當前邏輯狀態也即觸發前的狀態, Qn+1 是指觸發后的狀態。

通過這個表格,可以看出,當 C 為 1 時, D 的狀態和 Qn+1 的狀態完全一樣,當 D=0 時, Qn+1=0,當 D=1 時, Qn+1=1。進一步畫出 D 鎖存器的波形圖。

從 D 鎖存器的波形圖可以看出, D 是鎖存器的輸入信號, C 是鎖存器的控制信號,Q 是鎖存器的輸出信號。當控制信號 C 為高電平時,輸出信號 Q 將跟隨輸入信號 D 的變化而變化。

為什么要避免鎖存器?(Latch的危害)

前面雖然提到鎖存器是組合邏輯電路與時序電路的橋梁,但是其靈活性很難保證在設計中進行精準分析。在實際使用中,Latch 多用于門控時鐘(clock gating)的控制,在絕大多數設計中我們要避免產生鎖存器。它會讓設計的時序出問題,并且它的隱蔽性很強, 新人很難查出問題。

- 毛刺敏感 :鎖存器最大的危害在于不能過濾毛刺和影響工具進行時序分析。這對于下一級電路是極其危險的。這也就是為什么寄存器不用電平觸發而選擇使用邊沿觸發的原因。所以,只要能用觸發器的地方,就不用鎖存器。

- 不能異步復位: 由于其能夠儲存上次狀態的原因,上電后Latch處于不定態。

- 占用更多資源: 對于絕大多數當前主流的FPGA架構資源中,基本是不包含Latch,這也就意味著需要更多的資源去實現搭建Latch。在早些版本的某些FPGA內部包含了Latch。

- 使時序分析變得復雜: 鎖存器沒有時鐘信號,只有數據輸入和使能以及輸出 q 端,沒有時鐘信號也就說明沒有辦法對這種器件進行時序分析, 這個在時序電路里面是非常危險的行為,因為可能引起時序不滿足導致電路功能實現有問題。

- 額外的延時: 在ASIC設計中,鎖存器也會帶來額外的延時和DFT,并不利于提高系統的工作頻率。

結構完整就能避免Latch?

關于如何避免,可能大多數的人首先想到的是組合邏輯電路中,在if-else結構中缺少else或case結構中缺少default所導致,所以中要求if-else結構和case結構要寫完整。但結構完整就真能完全避免Latch的產生嗎?

module demo(

input wire [1:0] en,

output reg[3:0] latchtest

);

always @(*) begin

if (en ==1) begin

latchtest = 'd6;

end

else if (en ==2) begin

latchtest = 'd3;

end

else begin

latchtest = latchtest;

end

end

endmodule

圖上示例這種情況,雖然邏輯完整但也會生成latch,其原因是針對該邏輯信號進行了保持,構成了邏輯環路。

latch測試

同樣下圖中的設計也會產生鎖存器,原因是雖然邏輯完備但是沒有針對單一信號進行完備邏輯的處理,在部分邏輯信號進行了保持,所以邏輯仍生成了latch。

//demo1

reg latchtest1,latchtest2;

always @(*)begin

if(enable)

latchtest1 = in;

else

latchtest2 = in;

end

下面的設計是我認為比較隱晦的latch。乍一看,分支完備,case語句也有default,但在EDA工具進行分析后仍出現latch

module demo(

input wire [1:0] en,

output reg[3:0] latchtest

);

always @(*) begin

case (en)

0:latchtest[0] = 'd1;

1:latchtest[1] = 'd1;

2:latchtest[2] = 'd1;

3:latchtest[3] = 'd1;

default:latchtest = 'd1;

endcase

end

分析其根本原因仍然是,針對相關的分支條件該信號的部分bit位進行了保持。

隱晦的latch設計

此外,三目運算符在組合邏輯設計時進行邏輯保持,同樣會引入latch。

鎖存器產生的根本原因

生成latch的例子很多,從例子來看不論是單個信號或者是一個信號某些位,只要在組合邏輯設計時他存在邏輯保持都有可能生成latch,但說鎖存器產生的根本原因,即為代碼設計時的邏輯:需要在組合邏輯中避免保持的操作。當組合邏輯需要保持時,就會綜合出鎖存器。

避免Latch的解決方法

整理常見出現組合邏輯保持的情況,也即能得到避免生成latch的相關方法。

- if else分支結構不完整

- 組合邏輯中case結構不完整

- 組合邏輯設計時使用三目運算符存在邏輯保持

- 使用原信號進行賦值或者使用原信號進行條件判斷

- 敏感信號列表不完整

所以避免latch的方法就是,要對以上或者其他未列舉的組合邏輯中存在邏輯保持的情況進行改寫和規避,即可避免頭疼的latch生成。簡單來說就是:優化代碼邏輯,避免組合邏輯的邏輯保持。 當遇到邏輯保持的情況時,要對存在邏輯保持的分支進行補全,或者使用賦初值的方法進行覆蓋邏輯保持時的情況。

// 補全條件分支結構

always @(*) begin

if (en)

dout = in ;

else

dout = 'd0 ;

end

//賦初值

always @(*) begin

dout = 'd0 ;

if (en)

dout = data ; //如果en有效,改寫q的值,否則q會保持為0

end

必要的邏輯保持怎么處理?

可能對于有些情況無法完全避免掉組合邏輯設計的邏輯保持,對于這種情況,可以在這個組合邏輯路徑中插入一級寄存器,寄存器的輸出替代原來邏輯保持的部分,示例如下:

wire [DATA_WIDTH-1:0] accsum_in = (ab_sum_valid)?sum_in:dout;

always @(posedge clk or negedge rst_n) begin

if(rst_n == 'd0)begin

dout <= 'd0;

end

else if(adder1_outvld == 1)begin

dout <= sum_in ;

end

end

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26562 -

EDA工具

+關注

關注

4文章

268瀏覽量

31868 -

鎖存器

+關注

關注

8文章

906瀏覽量

41567 -

觸發器

+關注

關注

14文章

2000瀏覽量

61265 -

DFT

+關注

關注

2文章

231瀏覽量

22774

發布評論請先 登錄

相關推薦

談談Latch:組合與時序邏輯的橋梁

談談Latch:組合與時序邏輯的橋梁

評論