【核芯觀察】是電子發(fā)燒友編輯部出品的深度系列專欄,目的是用最直觀的方式令讀者盡快理解電子產(chǎn)業(yè)架構(gòu),理清上、中、下游的各個環(huán)節(jié),同時迅速了解各大細(xì)分環(huán)節(jié)中的行業(yè)現(xiàn)狀。以ChatGPT為首的AI大模型在今年以來可以說是最熱的賽道,而AI大模型對算力的需求爆發(fā),也帶動了AI服務(wù)器中各種類型的芯片需求,所以本期核芯觀察將關(guān)注ChatGPT背后所用到的算力芯片產(chǎn)業(yè)鏈,梳理目前主流類型的AI算力芯片產(chǎn)業(yè)上下游企業(yè)以及運(yùn)作模式。

接上期ChatGPT背后的算力芯片(二)

AI服務(wù)器中的主要算力芯片之FPGA

市場現(xiàn)狀

FPGA的最大特點(diǎn)就是,在芯片被設(shè)計(jì)、制造完成之后,用戶依然可以通過修改其邏輯單元和開關(guān)陣列編程,來進(jìn)行功能配置,實(shí)現(xiàn)所需要的功能。在AI算法快速迭代的過程中,用戶可以通過持續(xù)優(yōu)化FPGA的功能配置,來提高運(yùn)算效率。這也是FPGA與CPU、GPU、ASIC等芯片最大的不同。

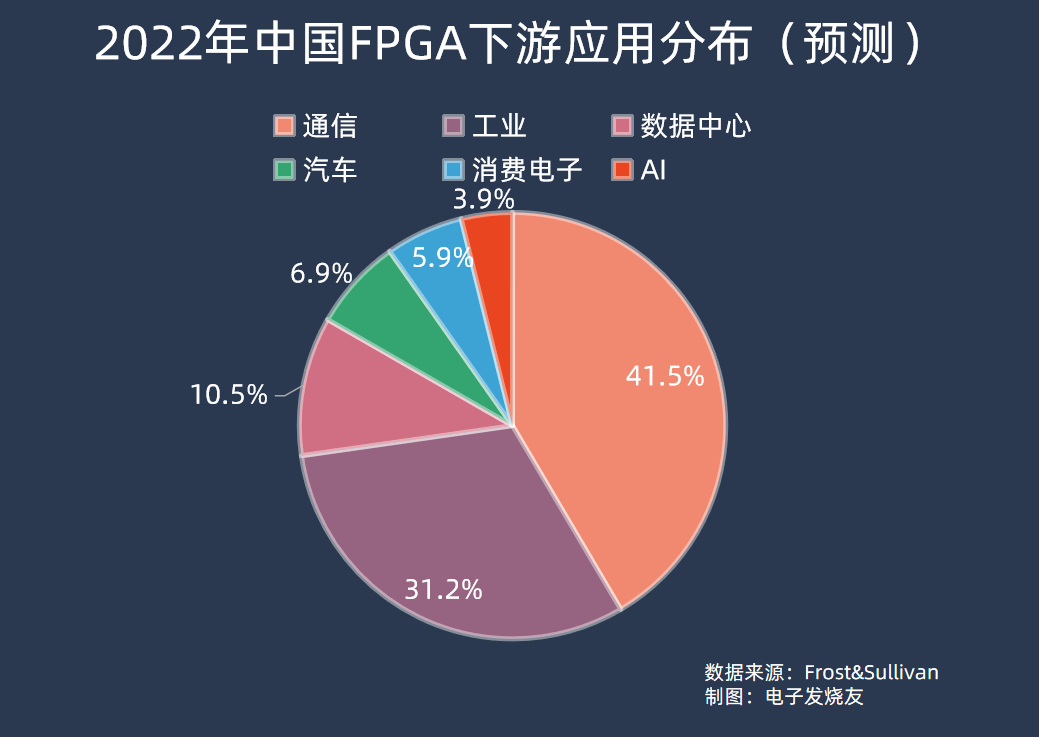

所以最初FPGA被大量用于通信領(lǐng)域,可以靈活更改高速通信協(xié)議的處理方式,適配不同場景。根據(jù)Frost&Sullivan的預(yù)測數(shù)據(jù),2022年中國FPGA下游應(yīng)用中,通信占比最高為41.52%,工業(yè)應(yīng)用其次,占比31.23%。數(shù)據(jù)中心、汽車、消費(fèi)電子、AI分別占比10.54%、6.94%、5.89%、3.88%。

從全球市場來看,根據(jù)Frost&Sullivan數(shù)據(jù),估算2021年全球FPGA市場規(guī)模為68.6億美元,2022年預(yù)計(jì)為79.4億美元,同比增長15.7%;到2025年市場規(guī)模將增長至125.8億美元,2021年到2025年年均復(fù)合增長率約16.4%。

中國市場上,2021年FPGA市場規(guī)模為176.8億元,到2025年 FPGA芯片銷售額將達(dá)到332.2億元,2021至2025年年均復(fù)合增長率將達(dá)到17.1%。出貨量方面,中國市場FPGA芯片出貨量在2020年約為1.6億顆,預(yù)計(jì)到2025年將達(dá)到3.3億顆,2021至2025年年均復(fù)合增長率將達(dá)到15.0%。

其中數(shù)據(jù)中心、AI領(lǐng)域市場增長迅速,F(xiàn)PGA能夠使數(shù)據(jù)中心的不同器件更加有效地協(xié)同,最大程度發(fā)揮每個器件的硬件優(yōu)勢避免數(shù)據(jù)轉(zhuǎn)換導(dǎo)致的算力空耗;在運(yùn)算加速領(lǐng)域,F(xiàn)PGA 在矩陣運(yùn)算、圖像處理、機(jī)器學(xué)習(xí)、非對稱加密、搜索排序等領(lǐng)域有著很廣闊的應(yīng)用前景。

在中國數(shù)據(jù)中心細(xì)分市場,F(xiàn)rost&Sullivan預(yù)計(jì)該市場規(guī)模在2021年為18.7億元,到2025年會達(dá)到34.6億元,其間年均復(fù)合增長率將為16.6%。

不過自去年年底以來,由OpenAI掀起的AI熱潮,有望推動FPGA市場以遠(yuǎn)超出此前預(yù)期的速度增長。

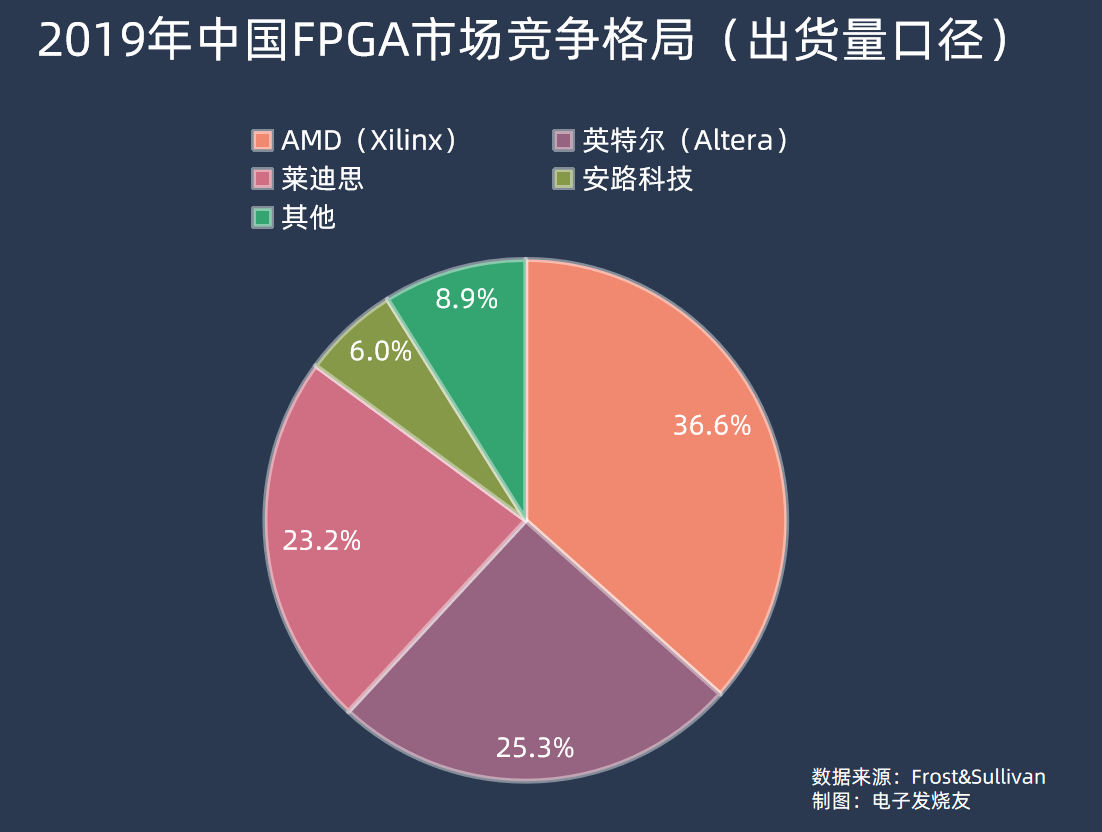

近年沒有新的FPGA市場份額數(shù)據(jù),按照Frost&Sullivan 2019年的數(shù)據(jù),中國市場上AMD(賽靈思)、英特爾(Altera)兩家占到FPGA市場銷售額的九成以上,分別為55.1%和36%。而按照FPGA出貨量來看,同期AMD占36.6%、英特爾占25.3%、萊迪思占23.2%、安路科技占6%。

FPGA的核心參數(shù)是邏輯單元容量,按照邏輯單元容量來分,2019年中國FPGA市場中需求量最大的是100K以下和100K—500K邏輯單元容量的FPGA,份額分別占市場的38.2%和31.7%,更高端的500K-1KK以及1KK以上邏輯單元容量的FPGA則分別占24.4%和5.7%的份額。

全球范圍來看,F(xiàn)PGA市場目前由AMD和英特爾雙寡頭壟斷,占整個市場份額近90%,第二梯隊(duì)的海外廠商有萊迪思、Microsemi等,各占5%左右。國內(nèi)FPGA廠商主要有復(fù)旦微電子、紫光國微(紫光同創(chuàng))、安路科技、高云半導(dǎo)體、華微電子、智多晶、京微齊力等等,不過從邏輯單元容量來看,國內(nèi)廠商主要集中在500K以下,更多產(chǎn)品線的邏輯單元容量在200K以下,中低端市場布局較為完善,但中高端領(lǐng)域目前國產(chǎn)FPGA仍未有大規(guī)模涉足。

復(fù)旦微電子在2018年推出了億門級FPGA系列,邏輯單元容量可達(dá)700K,據(jù)了解,其新一代十億門級的大容量FPGA有望在2023年內(nèi)推出。而2019年英特爾推出的 Stratix 10 GX 10M FPGA邏輯單元已經(jīng)高達(dá)10KK,相比之下國產(chǎn)FPGA在高端市場目前缺口還是較大的,但目前重要的是在中低端市場站穩(wěn),奪得更多的國內(nèi)市場份額。

AI服務(wù)器FPGA的趨勢

衡量FPGA的容量,有兩個階段,在2000年以前,F(xiàn)PGA廠商用門級數(shù)量規(guī)模來衡量FPGA的容量,因?yàn)锳SIC的最小功能單元是“門”,而本質(zhì)上FPGA與ASIC都可以同樣功能,甚至在ASIC設(shè)計(jì)過程中都會使用到FPGA進(jìn)行驗(yàn)證,所以“門”可以間接體現(xiàn)FPGA的容量。

后來2000年后,F(xiàn)PGA廠商逐漸開始轉(zhuǎn)用統(tǒng)一的邏輯單元來表示FPGA容量,這主要是由于FPGA性能需求的升級,芯片內(nèi)部的LUT結(jié)構(gòu)和集成度不斷改變,用門級數(shù)來表示FPGA容量越來越難。

如今FPGA不僅是單純的FPGA,而是將RAM、DSP、收發(fā)器、DDR接口、CPU、GPU等許多功能嵌入到 FPGA 中,所以對于FPGA的評價指標(biāo),也變得更加復(fù)雜,需要根據(jù)不同應(yīng)用去衡量參數(shù)。

在AI服務(wù)器中,F(xiàn)PGA往往起到加速計(jì)算的作用,F(xiàn)PGA的特性可以令其在深度學(xué)習(xí)中異構(gòu)計(jì)算、并行計(jì)算方面有一定優(yōu)勢,且其具備低延時的特性,在AI服務(wù)器中FPGA還可以實(shí)現(xiàn)數(shù)據(jù)高速收發(fā)、交換等功能。同時,相比于CPU和GPU,F(xiàn)PGA單位能耗比還更低,特別在深度學(xué)習(xí)領(lǐng)域,近年來微軟、百度、亞馬遜等已經(jīng)在數(shù)據(jù)中心大規(guī)模部署FPGA。

有數(shù)據(jù)顯示,在保持相同神經(jīng)網(wǎng)絡(luò)模型計(jì)算結(jié)果的同時,F(xiàn)PGA平臺的16位定點(diǎn)計(jì)算性能普遍是CPU的2到3倍,計(jì)算資源利用率更是CPU的接近20倍;與GPU相比,盡管計(jì)算性能沒有明顯領(lǐng)先,但功耗顯著降低,所以FPGA在AI服務(wù)器中用于計(jì)算加速是有明顯優(yōu)勢的。

在AI服務(wù)器中,F(xiàn)PGA的一些重要指標(biāo)包括邏輯單元數(shù)、DSP的數(shù)量、收發(fā)器的傳輸速率等。另一方面,F(xiàn)PGA的制程工藝也是考量FPGA的一個重要標(biāo)準(zhǔn),目前高端FPGA的制程基本是20nm以下,AMD目前最高端的產(chǎn)品線就采用臺積電16nm制程。

同時邏輯單元數(shù)大于700K,基本在1KK以上的水平;DSP的數(shù)量較多,比如超過10000的DSP;較高的Bloch RAM容量,比如1000Mb以上;收發(fā)器速率高于50GB/s,還集成CPU等的處理單元和PCIe 5等先進(jìn)接口。

總而言之,高端的FPGA往往以SoC的形式呈現(xiàn)。而為了更加便于數(shù)據(jù)中心、AI服務(wù)器等應(yīng)用的導(dǎo)入,F(xiàn)PGA廠商也提供了比如數(shù)據(jù)中心加速卡的解決方案,比如AMD Alveo系列。

AI服務(wù)器中的主要算力芯片之ASIC

市場現(xiàn)狀

近年來,TPU、NPU、VPU、DPU、BPU等各種名詞層出不窮,其實(shí)這些從廣義的概念看都屬于ASIC。

ASIC其實(shí)與前面提到的FPGA有密切的關(guān)系,在ASIC開發(fā)的過程中,往往要用到FPGA驗(yàn)證。理論上一些芯片功能如果能用FPGA做出來,那么ASIC就同樣可以做到,本質(zhì)上是用兩種不同的設(shè)計(jì)理念來讓芯片實(shí)現(xiàn)部分相同的功能。

當(dāng)然,F(xiàn)PGA的靈活程度是ASIC不可比擬的,ASIC自設(shè)計(jì)之初就被限定了功能,無法像FPGA一樣在實(shí)際使用中還可以隨時重新配置芯片功能。

雖然ASIC的設(shè)計(jì)流程漫長,但ASIC相比FPGA由于進(jìn)行了完整的定制,專為特定程序優(yōu)化電路,在進(jìn)行特定任務(wù)時性能會更加穩(wěn)定,并且運(yùn)行效率、能效比都會優(yōu)于FPGA。

根據(jù)Bob Broderson數(shù)據(jù),F(xiàn)PGA的能效比集中在1-10MOPS/mW之間。ASIC的能效比處于專用硬件水平,超過100MOPS/mW,是FPGA的10倍以上。

目前來看,在AI服務(wù)器場景中,ASIC主要用于推理服務(wù)器,針對已經(jīng)訓(xùn)練完成的模型來設(shè)計(jì)高效的運(yùn)算硬件。但當(dāng)前AI大模型領(lǐng)域正處于爆發(fā)初期,ASIC在AI服務(wù)器上的份額或許會呈現(xiàn)后發(fā)趨勢,在相關(guān)應(yīng)用的AI模型成熟后,未來在云端推理方面將有較大的市場空間。正如地平線CEO余凱曾說的,“一旦軟件算法固定下來,專用集成電路ASIC一定是未來的方向”。

KBVResearch報告數(shù)據(jù)顯示,到2025年,全球ASIC芯片市場規(guī)模預(yù)計(jì)將達(dá)到247億美元,在2019到2025年間的復(fù)合年增長率為8.2%。

也正因?yàn)槟壳皯?yīng)用方面的一些難點(diǎn),暫時來看,全球ASIC市場還未出現(xiàn)明顯的領(lǐng)先者,海內(nèi)外廠商都在高速發(fā)展的過程中。

海外的主要玩家有谷歌、Habana(英特爾收購)等,谷歌目前已經(jīng)推出了四代 TPU產(chǎn)品,TPU v5據(jù)稱即將在今年內(nèi)面世;英特爾在2019年收購了Habana,隨后在2022年推出了Gaudi 2;云服務(wù)器巨頭亞馬遜也在持續(xù)布局開發(fā)ASIC,此前亞馬遜計(jì)劃在Alexa語音助手運(yùn)算上采用ASIC,以降低對英偉達(dá)的依賴;微軟近幾年都有消息傳出,正在開發(fā)一款名為Athena的AI訓(xùn)練專用ASIC,據(jù)稱還將采用臺積電5nm制程,不過還未有這款芯片的具體消息。

國內(nèi)玩家有海思、寒武紀(jì)、燧原科技、百度、阿里等,其中海思、百度、阿里由于其公司業(yè)務(wù)場景對ASIC存在天然需求,因此選擇ASIC能降低其服務(wù)器建設(shè)成本。海思在2019年推出了昇騰910,百度也在同年推出了昆侖芯片、阿里也在2019年推出了含光800。

其中華為通過ASIC部署了端到端的完整生態(tài),比如使用昇騰910時,需要搭配華為的大模型支持框架MindSpore和盤古大模型等;阿里則將含光800用于自家業(yè)務(wù)平臺的加速,比如為淘寶等平臺提供算力支持;百度的昆侖芯則主要在自身服務(wù)器、算力集群等應(yīng)用,對政企客戶等提供算力。

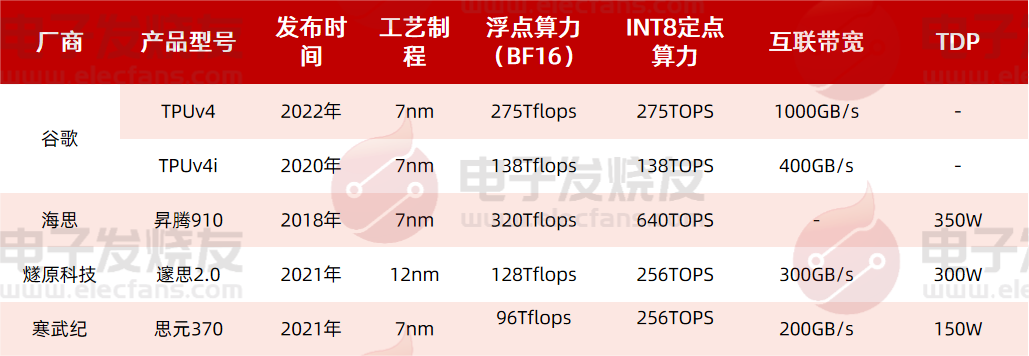

以公開的算力數(shù)據(jù)來算,海思的昇騰910在BF16浮點(diǎn)算力為320Tflops,已經(jīng)超越谷歌最新一代產(chǎn)品TPUv4的275Tflops,在INT8定點(diǎn)算力上同樣大幅領(lǐng)先。同時遂原科技和寒武紀(jì)的產(chǎn)品在整體性能上也與谷歌的TPUv4相差不遠(yuǎn),當(dāng)然,由于應(yīng)用上的區(qū)別,可能是設(shè)計(jì)上有不同傾向,比如TPUv4互聯(lián)帶寬較高,1000GB/s遠(yuǎn)遠(yuǎn)領(lǐng)先于遂原科技和寒武紀(jì)的產(chǎn)品。

燧原科技在2021年推出了邃思2.0,采用12nm制程,單精度 FP32 算力為 40TFLOPS,單精度張量 TF32 算力為 160TFLOPS,整數(shù)精度 INT8 算力為 320TOPS,可用于云端AI訓(xùn)練;同期寒武紀(jì)也推出了思元370芯片,采用7nm先進(jìn)制程,算力最高可達(dá) 256TOPS (INT8),可靈活應(yīng)用于云端推理、訓(xùn)練等領(lǐng)域。

AI服務(wù)器上ASIC的發(fā)展趨勢

ASIC作為一種專用的集成電路,它的發(fā)展永遠(yuǎn)是跟隨算法需求而定,這種表現(xiàn)在谷歌、百度、阿里、華為等云服務(wù)廠商中可能尤為明顯。

不過在2020年,英特爾發(fā)布了全新可定制解決方案,同時也將“結(jié)構(gòu)化ASIC”的概念帶火。從上文我們也了解到,F(xiàn)PGA與ASIC關(guān)系密切,同時又各有優(yōu)勢,英特爾提出的“結(jié)構(gòu)化ASIC”,就是一種各項(xiàng)特性上介于FPGA和ASIC之間的芯片。

這種結(jié)構(gòu)化ASIC在量產(chǎn)成本、邏輯門利用率、能耗、效能速度等表現(xiàn)上優(yōu)于FPGA,但又不如純ASIC表現(xiàn)得優(yōu)異,同時也具有FPGA的可編程化邏輯功效,以及加速芯片的研發(fā)設(shè)計(jì)速度與修改彈性,使芯片能更快完成并投入市場。

簡單來說,結(jié)構(gòu)化ASIC是一種“半成品”的ASIC,它的性能和功耗接近標(biāo)準(zhǔn)單元ASIC,同時能夠節(jié)省一半的一次性工程費(fèi)用和設(shè)計(jì)時間。但也有所損失,因?yàn)槊芏戎挥袠?biāo)準(zhǔn)單元ASIC的50%到75%,所以結(jié)構(gòu)化ASIC的成本會是標(biāo)準(zhǔn)單元ASIC的1.5-2倍。

按照英特爾的說法,采用結(jié)構(gòu)化ASIC后,芯片編程不能像FPGA一樣可以在現(xiàn)場修改,而是需要在芯片工廠完成對芯片的編程。盡管成本仍然高達(dá)數(shù)十萬美元,但只需要幾個月時間就可以完成,傳統(tǒng)ASIC則至少需要兩年。

所以目前ASIC的一個最大痛點(diǎn)是,設(shè)計(jì)時間和資源消耗,這在如今快速迭代的AI大模型和AI算法中,是難以成為主流的。而從結(jié)構(gòu)化ASIC的發(fā)展來看,事實(shí)上這個概念并非英特爾首創(chuàng),但過去由于半導(dǎo)體工藝制程的高速發(fā)展,使得制程帶來的性能紅利要遠(yuǎn)遠(yuǎn)大于ASIC的帶來的能效提升,因此結(jié)構(gòu)化ASIC沒有受到市場重視。

而近年來摩爾定律逐漸放緩,芯片制程工藝也已經(jīng)邁入一個較為穩(wěn)定的階段,因此現(xiàn)階段ASIC應(yīng)用的主要限制就在于設(shè)計(jì)周期和流片等工程費(fèi)用投入。或許結(jié)構(gòu)化ASIC能夠成為下一階段ASIC的一個重要發(fā)展方向,加速ASIC在AI服務(wù)器上的部署。

值得一提的是,電子發(fā)燒友網(wǎng)主辦的第七屆人工智能大會將在2023年8月23日正式召開,

在過去的三屆大會中,我們舉辦的“中國人工智能卓越創(chuàng)新獎”評選活動得到了業(yè)界的普遍認(rèn)可和廣泛好評。2023年我們將繼續(xù)這一殊榮的評選,舉辦“2023第四屆中國人工智能卓越創(chuàng)新獎”評選活動,旨在發(fā)掘和表彰人工智能領(lǐng)域優(yōu)秀人才、企業(yè)、技術(shù)以及產(chǎn)品。

“2023第四屆中國人工智能卓越創(chuàng)新獎”獎項(xiàng)提名于即日起到6月30日截至,提名詳情可掃描下方二維碼了解。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603319 -

asic

+關(guān)注

關(guān)注

34文章

1200瀏覽量

120501 -

gpu

+關(guān)注

關(guān)注

28文章

4739瀏覽量

128941 -

ChatGPT

+關(guān)注

關(guān)注

29文章

1560瀏覽量

7666

發(fā)布評論請先 登錄

相關(guān)推薦

AI算力芯片供電電源測試?yán)?費(fèi)思低壓大電流系列電子負(fù)載

AI算力芯片作為驅(qū)動復(fù)雜計(jì)算任務(wù)的核心引擎,其性能與穩(wěn)定性成為了決定應(yīng)用成敗的關(guān)鍵因素。而在這背后,供電電源的穩(wěn)定性和高效性則是保障AI算

存算一體架構(gòu)創(chuàng)新助力國產(chǎn)大算力AI芯片騰飛

在灣芯展SEMiBAY2024《AI芯片與高性能計(jì)算(HPC)應(yīng)用論壇》上,億鑄科技高級副總裁徐芳發(fā)表了題為《存算一體架構(gòu)創(chuàng)新助力國產(chǎn)大算力

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構(gòu)分析」閱讀體驗(yàn)】--全書概覽

本帖最后由 1653149838.791300 于 2024-10-16 22:19 編輯

感謝平臺提供的書籍,厚厚的一本,很有分量,感謝作者的傾力付出成書。

本書主要講算力芯片CPU

發(fā)表于 10-15 22:08

名單公布!【書籍評測活動NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架構(gòu)分析

紙質(zhì)媒體的高質(zhì)量和專業(yè)網(wǎng)絡(luò)媒體的信息更新速度。

算力芯片在最近15年有著巨大性能突破,這些年Intel的CPU芯片從雙核128位SIMD到眾

發(fā)表于 09-02 10:09

淺析三大算力之異同

隨著一年多前ChatGPT的出現(xiàn)引爆人工智能(AI)浪潮,支撐大模型背后的“算力”概念突然闖進(jìn)我們的視野,成為科技圈炙手可熱的新詞,引領(lǐng)著最新潮流。作為數(shù)字經(jīng)濟(jì)時代新生產(chǎn)

從多核到眾核, 賽昉科技RISC-V+NoC IP子系統(tǒng)為算力芯片賦能

全球算力產(chǎn)業(yè)已然邁入新一輪的快速發(fā)展階段,RISC-V具備開源開放、模塊化等獨(dú)特優(yōu)勢,使我國能夠獨(dú)立開發(fā)、部署滿足特定安全需求的算力芯片產(chǎn)品

揭秘芯片算力:為何它如此關(guān)鍵?

在數(shù)字化時代,芯片作為電子設(shè)備的核心組件,其性能直接關(guān)系到設(shè)備的運(yùn)行速度和處理能力。而芯片的算力,即其計(jì)算能力,更是衡量芯片性能的重要指標(biāo)。

【核芯觀察】IMU慣性傳感器上下游產(chǎn)業(yè)梳理(二)

前言:【核芯觀察】是電子發(fā)燒友編輯部出品的深度系列專欄,目的是用最直觀的方式令讀者盡快理解電子產(chǎn)業(yè)架構(gòu),理清上、中、下游的各個環(huán)節(jié),同時迅速了解各大細(xì)分環(huán)節(jié)中的行業(yè)現(xiàn)狀。本期【核

高算力芯片:未來科技的加速器?

在數(shù)字化時代,芯片作為電子設(shè)備的核心組件,其性能直接關(guān)系到設(shè)備的運(yùn)行速度和處理能力。而芯片的算力,即其計(jì)算能力,更是衡量芯片性能的重要指標(biāo)。

Sora算力需求引發(fā)業(yè)界對集結(jié)國內(nèi)AI企業(yè)算力的探討

據(jù)周鴻祎觀察,Sora視頻分析所需算力恐遠(yuǎn)超千億規(guī)模模型。因而,考慮到如今國內(nèi)芯片供應(yīng)受限,算力

是德科技智能算力‘芯’技術(shù)研討會回顧

2023年12月20日,是德科技成功舉辦了智能算力‘芯’技術(shù)研討會。此次研討會由是德科技的行業(yè)市場經(jīng)理周巍策劃并主持,研討會聚焦算力網(wǎng)絡(luò),

ChatGPT算力芯片如何做算力輸出

算力卡的核心當(dāng)然還是計(jì)算芯片,會搭配大容量高帶寬的內(nèi)存、緩存,以及搭載CPU用于調(diào)度,為了幫助數(shù)據(jù)傳輸,便會使用高速通道,這便是PCIe(高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn))在系統(tǒng)中的作用:提供總線通道。

發(fā)表于 01-11 10:01

?503次閱讀

【核芯觀察】ChatGPT背后的算力芯片(三)

【核芯觀察】ChatGPT背后的算力芯片(三)

評論