關于這個問題,我們看看身邊的同行都是如何回答的吧:

工程師A:這個問題其實...說白了主要是大家都在用,或者說大部分時候it works。

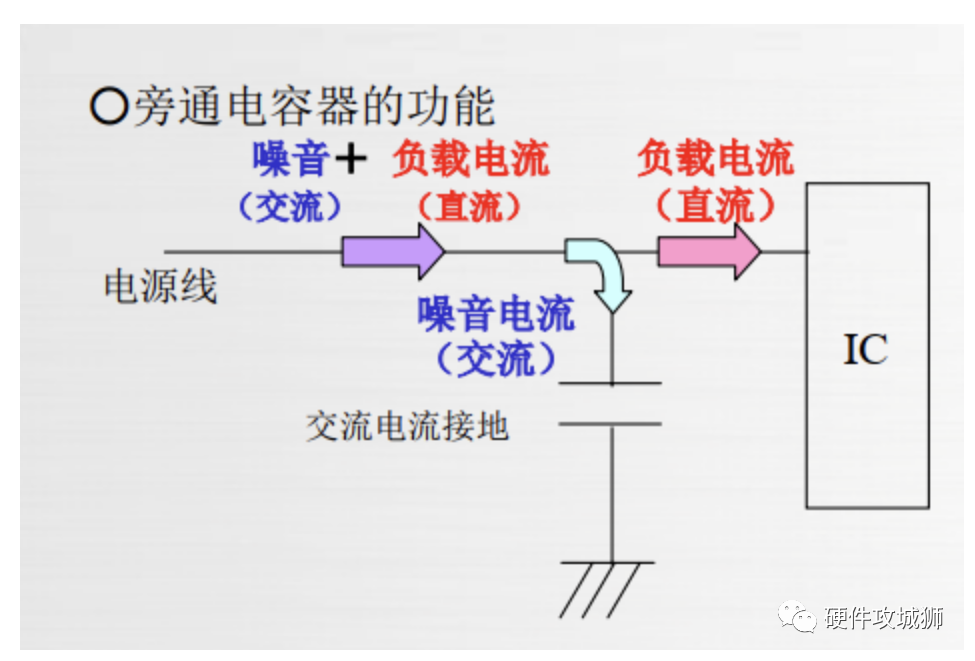

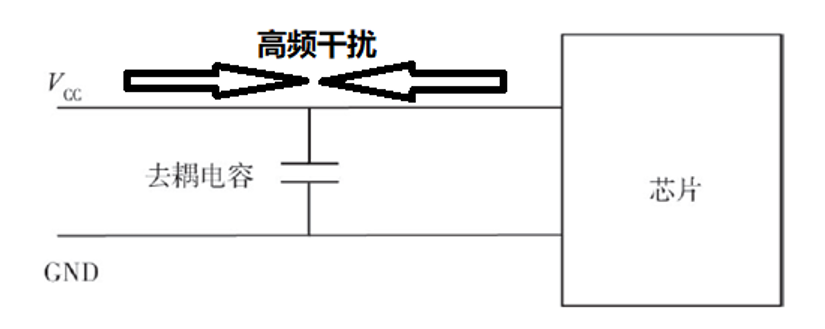

其實多看一些電源完整性相關的資料能發現不少討論,100nF的去耦電容作用頻段一般認為是幾MHz到二三十MHz,再配合板上的bulk電容,能實現從很低頻到二三十MHz這個頻段內全程較低的電源阻抗,大部分的應用已經夠用了。另外一方面因為大家形成了用100nF去耦的習慣,這樣的電容通常也有大量的庫存,采購價格也便宜,所以也沒必要標新立異去選其它容值,比如82nF,效果可能差不多,但你這么用,采購的同事肯定會找你的麻煩。

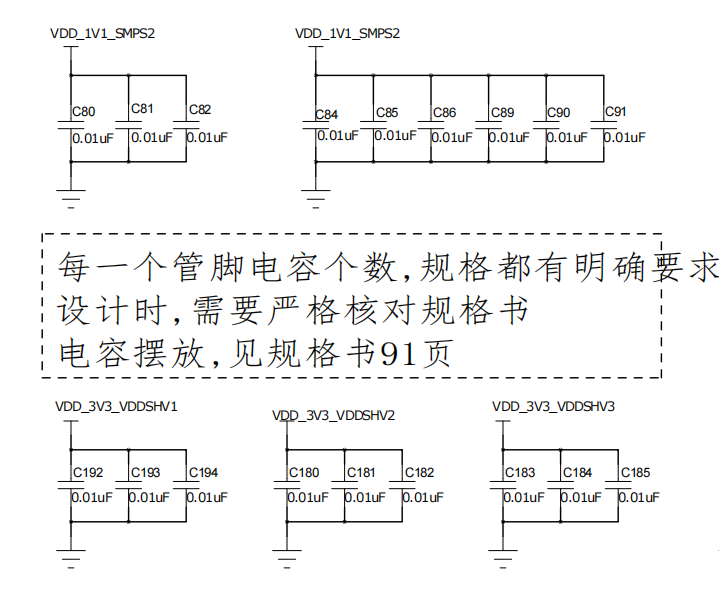

另外一方面,現在大量的高速IC尤其是高速數字IC會集成高頻去耦電容,所以片外只用搞一些相對低頻的去耦就夠了,一般做法就是搞一堆幾百nF級別的電容。而且片上集成的高頻去耦電容的效果比板上的強多了,板上去耦電容作用頻段的極限大概就兩三百MHz吧,對于現在動輒幾百MHz往上的時鐘頻率來說主要起安慰效果。

其他容值的去耦電容也不是不用,低頻模擬電路就會用上uF級別的去耦電容,PLL啊時鐘驅動器啥的又可能用上pF級別的,需要具體情況具體分析,分析不來懟個100nF上去大部分情況下沒啥問題。我最近遇到個問題,用1nF的去耦電容效果比用100nF的好,因為需要作用的頻段是200MHz左右。

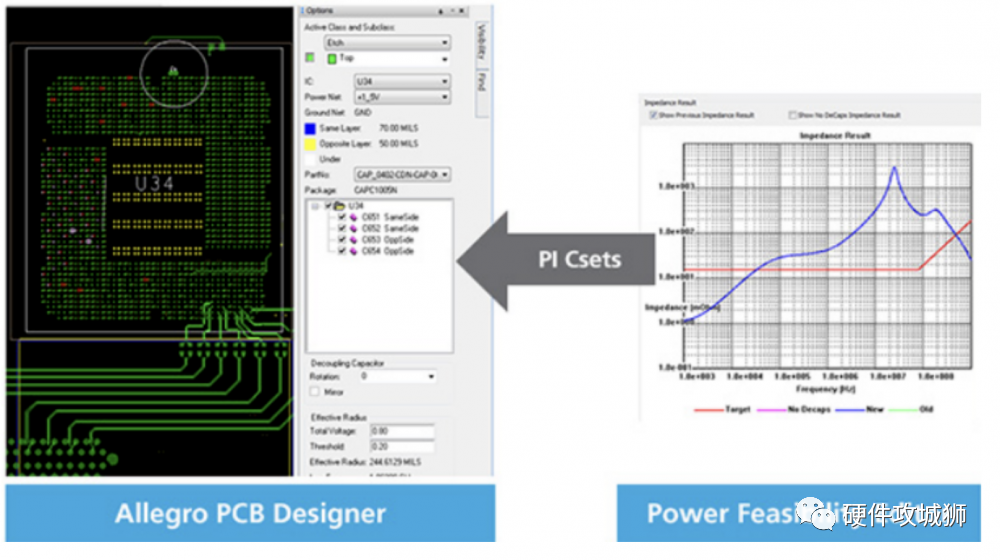

工程師B:放很多100nf是粗糙的設計,合理的做法是做PDN仿真,在電源平面所有頻段控制阻抗滿足要求。

100nF電容成本較低,在不做詳細分析時,多放置一些,可以在1~100MHz之間都提供較低的交流阻抗,因此一般也沒什么問題。

不考慮成本,同封裝下容量越大濾波效果越好,1uF 0402比100nF 0402在全頻段濾波效果都好。

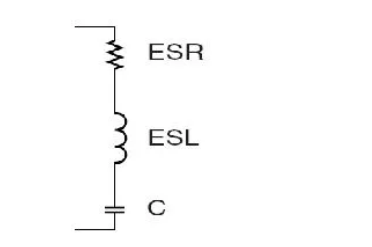

工程師C:100nF電容可以更好地去除高頻分量,小電容通常具有低ESR、低引線和內部電感、較高的自諧振頻率和較高頻率下的低阻抗。所以,在高頻數字電路的PCB板上,100nF很重要,然后作為一種設計習慣,這種方式被應用于很多數字電路設計中,成為一種規范。但其實,在以往調試很多電路板時,這種退耦效果可能并不能量化和直觀體現出來,是極端環境下的一種性能提升。

退藕電容并不是一個精確數值,因為每個電路的情況都不一樣,也不一定要100nF,而且常用較多的100nF是5%精度,對精度要求并不高,但100nF電容量大,封裝可以做到很小,容易制造,成本低,方便采購。前提是100nF對大部分數字IC來說,有較好的表現。

審核編輯:湯梓紅

-

IC

+關注

關注

36文章

5957瀏覽量

175734 -

仿真

+關注

關注

50文章

4093瀏覽量

133684 -

去耦電容

+關注

關注

11文章

316瀏覽量

22392 -

電源完整性

+關注

關注

9文章

209瀏覽量

20738 -

退耦電容

+關注

關注

1文章

29瀏覽量

9588

原文標題:為什么退耦電容通常選0.1uF?

文章出處:【微信號:電子設計寶典,微信公眾號:電子設計寶典】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么旁路電容緊盯著IC不放?為什么旁路電容總是0.1uF?

電容10uf和0.1uf并聯使用,這大小和個數是怎么算的?資料下載

電路中0.1UF和10UF電容有什么用?怎么用?資料下載

芯片IC0.1uF的電容,這些參數是如何確定

為什么退耦電容通常選0.1uF?

為什么退耦電容通常選0.1uF?

評論