毫米波 (mmWave) 成像已成為機場、公共建筑和體育場館安防掃描系統的重要組成部分。毫米波掃描儀優于傳統金屬探測器,因為它們可以識別和定位金屬和非金屬威脅。本文 介紹 了 毫米波 成像 硬件 的 工作 原理, 并 將 介紹 一種 芯片 組, 該 芯片 組 使用 邊緣 處理 來 管理 大量 數據 負載, 從而 支持 漫游 安全 掃描 系統 的 開發。

毫米波成像的工作原理

圖 1 說明 了 毫米波 掃描 器 的 工作 原理。該系統由連接到空間分散天線陣列的發射器和接收器陣列組成。該系統類似于測量回波損耗或S11的網絡分析儀。在任何時候,陣列中的一個天線都在以單個頻率發射低功率信號。該信號從目標反射并產生反向散射(插圖顯示了目標上單個點的反射,但實際上傳輸的信號是全向的,因此目標上的多個點會有反射)。

反向散射的相位和幅度由陣列中的所有接收天線測量。發射天線和接收天線之間可以使用極化,以減少直接發射到接收泄漏。測量完成后,從另一個發射天線(以相同頻率工作)發射相同的信號,并重復測量過程。

由于RF信號的穿透深度和反射的性質隨頻率而變化,因此前面描述的掃描通常在多個頻率下在寬帶上重復。由此產生的矢量矩陣形成一個多維數組(相對于頻率和空間位置),用于創建可以識別隱藏在衣服層之間和下方的金屬和非金屬物體的圖像。

完成此類掃描所需的硬件必須是多通道的,并且具有較寬的工作頻率范圍。10 GHz 至 40 GHz 的頻率范圍足夠寬,足以區分典型安全掃描場景中的對象(衣服、背包、武器和爆炸物)。較高的通道數系統往往具有更高的分辨率,使它們能夠識別小物體。例如,雖然檢測剃須刀片在機場掃描儀中至關重要,但保護公共建筑和體育場更側重于檢測較大的物品,如武器或爆炸物。在這些應用中,通常使用較少的通道數。

這些系統中的另一個關鍵組件是快速切換時間。這使得掃描系統得以實現,其中被掃描者只需在短時間內(通常為一秒或更短)擺姿勢。下一代演練系統需要更快的切換時間,以便人不必停下來擺姿勢。

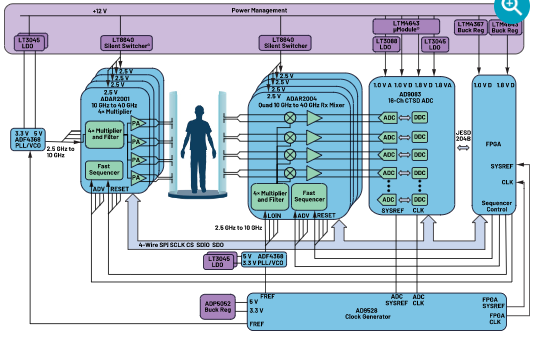

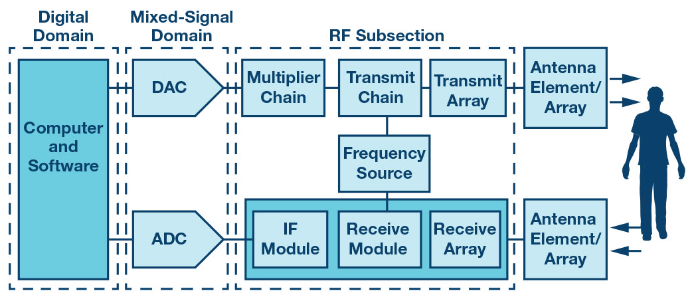

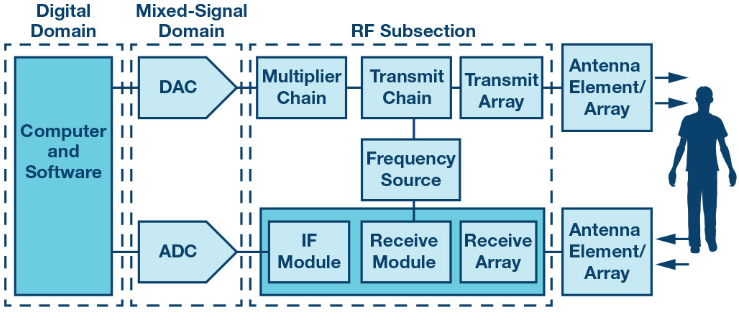

圖2顯示了如何使用ADI公司的毫米波成像芯片組實現完整的毫米波掃描儀。發射器陣列(ADAR2001)由中央捷變頻率源驅動。接收器陣列(ADAR2004)檢測反射信號,并將其下變頻至低中頻,在該頻率下,多通道連續時間Σ-Δ(CTSD)轉換器(AD9083)對其進行中頻采樣。

現在,我們將仔細研究這些組件以及它們的功能如何優化整體系統性能。

發射機

如前所述,發射器由大量空間分散天線組成,每個天線由功率放大器驅動。ADAR2001是一款4通道發射器,直接連接到天線,輸出頻率范圍為10 GHz至40 GHz。由于在大型陣列中分配10 GHz至40 GHz信號存在困難,ADAR2001集成了4×乘法器。因此,發射器 IC 前面的所有管道和信號分配都在 2.5 GHz 至 10 GHz 頻率范圍內進行。

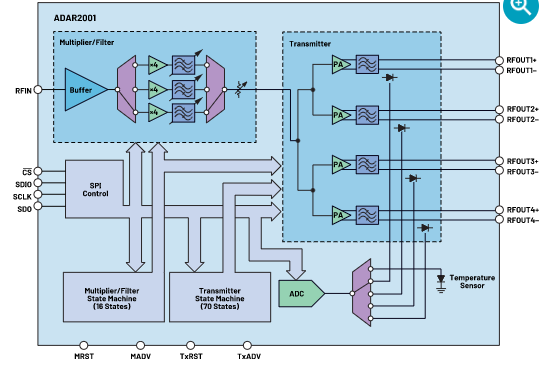

ADAR2001發射器的主要RF元件包括RF輸入緩沖器、帶集成可切換諧波濾波器的4×倍頻器、1:4信號分配器和2001個差分輸出功率放大器,用于驅動偶極子或螺旋天線等差分天線結構。ADAR3的詳細框圖如圖<>所示。

RFIN 端口施加 2.5 GHz 至 10 GHz 之間的 CW RF 輸入信號,功率電平至少為 –20 dBm。寬帶倍頻器由三個并聯子電路組成。每個子電路(低頻段、中頻段、高頻段)都經過優化,可乘以和濾波總頻率范圍的一部分。乘法器塊輸入端和輸出端的開關用于選擇所需工作頻率的子電路。

乘法器輸出通過可編程衰減器,然后分成四個并施加到四個功率放大器。除了乘法器模塊中的可配置濾波外,每個PA還包含一個可以啟用或禁用的低通/陷波濾波器。對于高達 20 GHz 的輸出頻率,應啟用此濾波器。高于 20 GHz,應禁用它。

可編程衰減器用于幫助確保輸出功率與頻率的關系相對平坦。該衰減器具有大約15 dB的數字步進衰減范圍。當輸出頻率從10 GHz掃描到40 GHz時,應減小此衰減,以保持所需的輸出功率平坦度與頻率的關系。這使得每個差分PA輸出的標稱PA輸出功率為+5 dBm,諧波抑制范圍為–20 dBc至–30 dBc。

要進行完整的 10 GHz 至 40 GHz 頻率掃描,必須將乘法器/濾波器模塊設置調整七次,以確保最佳的諧波抑制和輸出功率。此外,當系統以一個頻率駐留時,每個頻率

圖2.完整的毫米波成像系統。

圖3.ADAR2001 10 GHz至40 GHz發射器。

發射機通道必須依次打開和關閉。為了避免造成SPI命令瓶頸,ADAR2001包括兩個狀態機,可以預編程多達70種狀態。一旦器件的RAM被編程,就可以通過簡單的脈沖到器件的MADV(前進)引腳來實現狀態推進。這些特性相結合,可確保2 ns通道切換時間。在IC之間切換時也可以實現此切換時間(例如,器件A的通道4在器件B的通道1接通時關閉)。由于全掃描涉及多個頻率的全通道掃描,因此切換時間至關重要。例如,如果陣列有 500 個晶片,并且要以 10 MHz 的步長從 40 GHz 掃描到 50 GHz,則它必須執行總共 300,000 個通道切換才能完成完全掃描。

每個通道上的RF輸出功率可以使用單獨的片上RF檢波器進行監控。芯片溫度也可以通過片上溫度傳感器監控。這些傳感器饋入 5:1 模擬多路復用器,該多路復用器將所需信號傳遞到片內 8 位 ADC。

ADF4368 PLL/VCO為發射器網絡提供激勵。其輸出信號將根據發射通道的數量多次分離。ADF4368的輸出功率相對較高(+9 dBm)和ADAR2001的最小輸入閾值(–20 dBm)確保ADF4368的輸出在需要放大器緩沖之前可以多次無源分離。

接收器

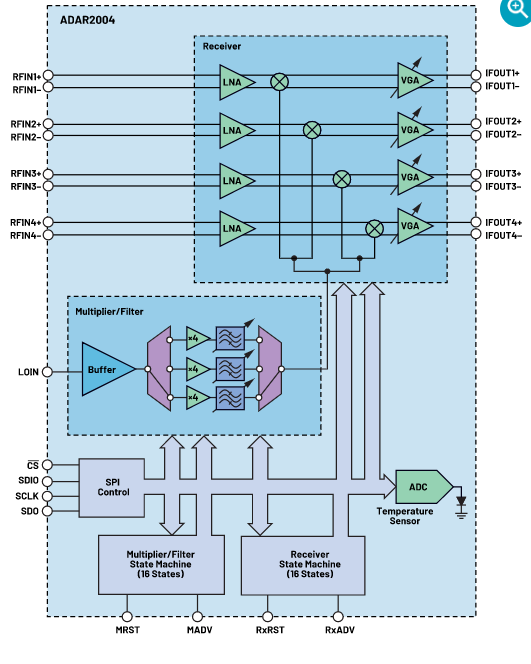

來自傳輸的反射被接收器拾取,接收器是多通道混頻器和ADC陣列。ADAR2004是一款四通道混頻器和ADC驅動器,內置數字編程增益放大器(DGA)。LO輸入也具有一個內部4×乘法器,由第二個PLL驅動,其輸出頻率與射頻偏移,因此混頻器產生真正的IF輸出。然后,混頻器的IF輸出由AD9083采樣,AD16是一款集成數字下變頻的<>通道連續時間Σ-Δ型ADC。選擇中頻采樣架構而不是零中頻架構,以避免接收器中LO泄漏引起的直流偏移,以及LO正交分路器中不完美的正交平衡引起的I/Q誤差。雖然這些缺陷可以通過校準來緩解,但每個輸入頻率都需要校準,因為LO泄漏和正交誤差往往隨頻率變化。

圖4所示為四通道混頻器ADAR2004的框圖。LO輸入由2.5 GHz至10 GHz正弦波驅動,在乘法器輸出端產生10 GHz至40 GHz的正弦波。乘法器輸出饋送到四個混頻器,這些混頻器的IF輸出具有可編程增益。與ADAR2001發射器一樣,ADAR2004接收器也具有兩個可預編程的片內狀態機。

多通道模數轉換器

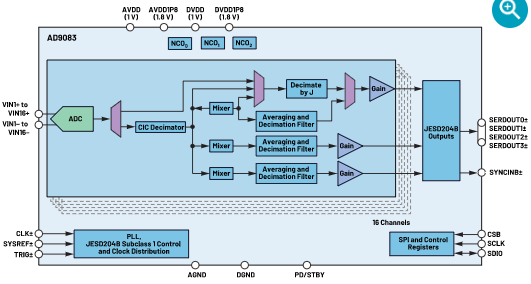

圖5所示為9083通道CTSD ADC AD16的框圖。ADC輸入設計為具有與ADAR2004的IF輸出相同的共模電壓。這允許混頻器輸出和ADC輸入直接連接。由于沒有交流耦合電容,可確保當混頻器輸出突然切換時(例如,在混頻器輸入端的頻率階躍期間),不會出現充電/放電瞬變。

使用集成單極點濾波器的一階CTSD ADC架構,最大限度地減少外部濾波,從而節省PCB空間。與奈奎斯特速率轉換器的建立時間相比,該架構還具有較快的信號建立時間,奈奎斯特速率轉換器需要高選擇性抗混疊濾波器來消除噪聲折疊。快速建立時間是本應用的關鍵要求,因為ADC建立時間必須能夠跟上發射側的快速通道開關。

圖4.ADAR2004 10 GHz至40 GHz接收器框圖。

每個ADC都有一個信號處理模塊,用于濾除來自Σ-Δ ADC的帶外整形噪聲并降低采樣速率。每個模塊包含一個級聯積分梳(CIC)濾波器、一個具有多個有限輸入響應(FIR)抽取濾波器(由J塊抽取)的正交數字下變頻器(DDC),或多達三個帶平均抽取濾波器的正交DDC通道,用于數據門控應用。三個正交DDC通道的存在可以同時解調多達三個頻率。稍后我們將看到如何使用它來顯著加快掃描時間。

系統設置和操作

ADAR2001和ADAR2004專為在大型陣列中高效工作而設計。特別強調減少布線開銷。ADAR2001和ADAR2004的RFIN和LO輸入端口可在低至–20 dBm的輸入電平下工作。由于需要從公共LO源(本例中為ADF4368)驅動這些輸入,因此這種低輸入靈敏度允許在需要放大之前進行大量無源扇出。例如,假設威爾金森功率分配器的凈損耗為1 dB,則ADF4368的9 dBm輸出功率可以無源扇出128次,可以驅動512個器件(<>個通道)。

驅動ADAR2001和ADAR2004片內時序控制器的進階和復位引腳也設計為并行驅動,以最大限度地減少處理器或FPGA必須提供的GPIO數量。通過在時序控制器中提供足夠的深度和復雜性,可以使用一組前進和復位脈沖驅動多達16個ADAR2001器件。

在工作之前,必須對ADAR2001和ADAR2004的時序控制器進行編程。雖然可以使用SPI命令訪問兩個設備的所有功能,但相關的延遲將導致不可接受的總掃描時間。

讓我們考慮如何為基于通道的掃描設置一個 64 通道系統(64 發射器、64 接收器),也就是說,我們在增加頻率并重復掃描之前以單個頻率循環遍歷所有傳輸通道。

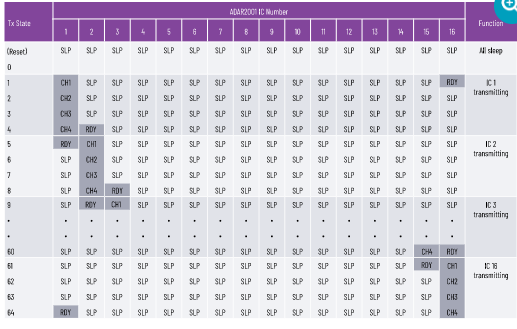

圖6顯示了如何對16個ADAR2001器件中的狀態機進行編程以啟用此掃描。該架構的一個關鍵目標是能夠對從公共控制線執行不同操作的多個設備進行排序。

請注意,在圖6中,雖然每個IC有65種狀態,但大多數IC大部分時間都設置為休眠模式(SLP)。例如,IC 1僅在前四種狀態下完全處于活動狀態,因為該IC的通道1、2、3和4按順序傳輸。在這四種狀態下,所有其他IC都處于SLP或就緒(RDY)模式。

圖5.AD9083原理框圖

同樣,IC 2僅在狀態5至8期間完全激活,因為所有其他IC都處于SLP或RDY模式。通過以這種方式配置16個狀態機,它們的導通周期彼此偏移,可以用并行脈沖驅動所有16個器件的前進和復位線路。

RDY模式是開發用于優化開關時間同時節省功耗的中間狀態。由于大多數發射器大部分時間處于非活動狀態,因此SLP模式是降低功耗的關鍵。但是,從系統角度來看,從SLP模式切換到傳輸模式(50 ns)所需的時間過長,會導致掃描期間出現延遲。RDY模式是一種中間狀態,可以在IC準備傳輸時調用。請注意,在圖7中,在狀態4中,IC 4的通道1正在傳輸,而IC 2通過將IC 4置于RDY模式來準備傳輸。在從發射器狀態 5 過渡到 1 的過程中,IC 2 從發射模式轉換到 RDY 模式,IC 10 從 RDY 模式轉換到發射模式。此轉換需要 1 ns。隨后的片內通道開關(即,從IC2上的通道3到通道4到通道2到通道2)的切換時間為1024 ns。對于以 10.40 GHz 步長從 0 GHz 掃描到 1 GHz 的 20 元素陣列,完整的掃描時間將小于 50 毫秒。這假設PLL鎖定時間為5 μs。如果使用兩個以乒乓模式運行的PLL來實現更快的頻率建立,則掃描時間將遠低于<> ms。

圖6.對16個ADAR2001發送器進行編程,用于由單個提前脈沖驅動的通道掃描。

ADAR2004接收器的操作和時序不太復雜,因為通常的做法是將所有接收器通道配置為始終接收。狀態機仍必須排序,以便在接收器與發射器一起掃描時選擇正確的乘法器路徑和濾波器設置。

如前所述,每個AD9083 ADC通道最多可以訪問三個正交DDC通道。這意味著它可以同時解調三個頻率,假設所有三個頻率都在ADC模擬輸入帶寬(125 MHz)的輸入頻率范圍內。例如,通過將三個IF音調定位在50 MHz、75 MHz和100 MHz,可以將這三個音調同時解調為I和Q基帶數據。

為了在發射端促進這種方法,必須使用三個發射PLL,而不是一個。三個發射頻率必須始終指向不同的物理發射IC(ADAR2001中的乘法器不能傳導多音信號)。這三個頻率必須始終不同,但在掃描時必須保持彼此接近的頻率。例如,如果其中一個ADAR2001器件上的一個通道以10 GHz的頻率傳輸,則另外兩個器件將以10.025 GHz和10.050 GHz的頻率發射,以支持50 MHz、75 MHz和100 MHz的IF輸出。此方案在傳輸路徑中需要更多的硬件和交換基礎設施,但具有將整體掃描時間減少 3 倍的好處。

結論

該芯片組由四通道發送器ADAR2001、四通道接收器ADAR2004、9083通道ADCAD16和PLL/VCOADF4368組成,具有實現下一代漫游毫米波安全掃描器所需的高集成度和功能。集成狀態機和片上數字下變頻可顯著卸載傳統的集中式處理,并將其轉移到智能邊緣。最終結果是,中央處理器在掃描期間不必擔心控制系統,并且它接收的數據已經被解調和抽取。雖然該芯片組專為毫米波安全成像應用而開發,但ADAR2001發射器和ADAR2004接收器的寬頻率范圍以及AD9083 16通道ADC的集成度,使該芯片組適用于需要高通道密度和快速開關的其他應用。

審核編輯:郭婷

-

芯片

+關注

關注

455文章

50832瀏覽量

423818 -

接收器

+關注

關注

14文章

2472瀏覽量

71926 -

毫米波

+關注

關注

21文章

1925瀏覽量

64820

發布評論請先 登錄

相關推薦

恩智浦與吉利汽車開展合作,定義下一代毫米波雷達

毫米波雷達在人體傳感器中有何應用

毫米波技術如何為自主機器人提供邊緣智能

毫米波傳感器實現邊緣智能的方法

毫米波人體掃描儀市場:過去、現在和未來

毫米波人體掃描儀市場: 過去、現在和未來

邊緣處理如何實現下一代毫米波掃描儀

邊緣處理如何實現下一代毫米波掃描儀

評論