- 位寬

即前一節提到的量化位數,常見的有8bit,10bit,12bit,16bit,24bit。比較少見的部分高速ADC有6bit~8bit。

- 分辨率

ADC所能分辨的最小量化信號的能力,最小分辨能力Δ=輸入滿量程電壓/2^N。分辨率主要由ADC的位數(輸出數字量的位數)決定,也與輸入滿量程有一定的關系。如一個輸出滿量程為0~5V的ADC、8位的ADC,其最小變化量為5V/2^8,約為19.5mV。若將ADC的位寬增加為10位,則ADC的最小變化量為5V/2^10,約為4.88mV。

- 量化誤差Σ

在量化過程中由于所采樣的電壓不一定能被Δ(最小量化單位)整除,所以量化前后存在一定誤差,此誤差稱為量化誤差。量化誤差屬于原理誤差,無法消除,理論上轉換器的位數越高,各離散電平之間的差值越小,量化誤差就越小。

- INL

INL (IntergerNonLinear, 積分非線性),指ADC實際轉換曲線與理想曲線在縱軸方向的差值,單位LSB,用于表示實際轉換曲線與理想的偏差程度。

- DNL

DNL (DifferentialNonLinear, 微分非線性),指ADC的實際量化臺階與對應于1LSB的理想值之間的差異。理想ADC偏差為0LSB。若DNL<1LSB,意味著傳輸函數具有單調性,沒有丟碼。

- SNR

SNR (Signal NoiseRatio,信噪比), ADC輸出信號功耗和噪聲功耗的比值,用dB表示。SNR=10*log(P_signal/P_noise),其中信號頻譜圖中基波分量有效值,噪聲=總能量-信號能量和諧波能量。理想ADC的噪聲主要來自量化噪聲。

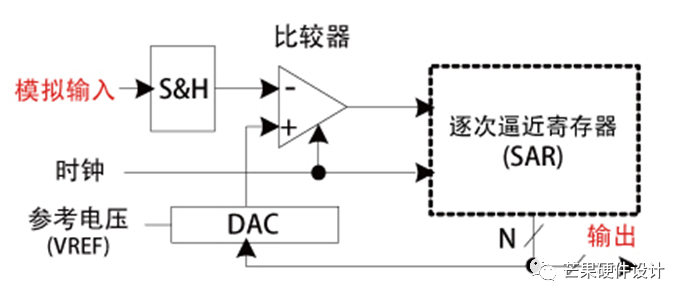

1.3 SAR型ADC原理

SAR(Successive Approximation, 逐次比較型), 包括一個比較器,一個數模轉換器、一個逐次逼近寄存器(SAR)和控制邏輯單元。將輸入的模擬信號與已知電壓(DAC,數模轉換)不斷進行比較,一個時鐘周期完成一次轉換,N位的ADC需要N個時鐘周期完成轉換,轉換完成后輸出二進制。

從上面描述可以看出,此種ADC有個問題,位寬越寬,轉換需要的時鐘周期越多,即如果想提高ADC分辨率,會限制采樣速率。所有此種ADC一般用在低速場景。

1.4 Σ-Δ型ADC原理

Σ-Δ型(Sigma-Delta-Converter, Σ-Δ型模數轉換器), 又稱為過采樣轉換器,它采用增量編碼方式,根據前一量值與后一量值的差值的大小進行量化和編碼。Σ-Δ型ADC主要由Σ-Δ型調制器和數字濾波器組成。調制器主要完成信號抽樣和增量編碼,給數字濾波器提供增量編碼。數字濾波器完成對Σ-Δ碼的抽取濾波,把增量碼轉換成高分辨率的線性脈沖碼調制的數字信號,因此抽取濾波器實際上相當于一個碼型變化器。

-

轉換器

+關注

關注

27文章

8703瀏覽量

147186 -

比較器

+關注

關注

14文章

1651瀏覽量

107220 -

DNL

+關注

關注

0文章

10瀏覽量

9358 -

ADC采樣

+關注

關注

0文章

134瀏覽量

12845 -

逐次逼近寄存器

+關注

關注

0文章

7瀏覽量

8180

發布評論請先 登錄

相關推薦

4.0電機參數的含義及測量方法 相關資料分享

步進電機的參數有哪些含義?

了解一下卡爾曼濾波中幾個參數的含義

移動WiMax參數指標及射頻測試淺析

淺析ADC的參數含義

淺析ADC的參數含義

評論