先來聊一聊什么是時鐘抖動。時鐘抖動實際上是相比于理想時鐘的時鐘邊沿位置,實際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實際上,時鐘源例如PLL是無法產生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現在理想值附近的一個范圍內,從而造成相鄰的時鐘邊沿存在偏差。在時序分析時,時鐘抖動是一個重要的因素。多種因素會導致時鐘抖動,包括PLL回路噪聲、電源紋波、熱噪聲以及信號之間的串擾等。

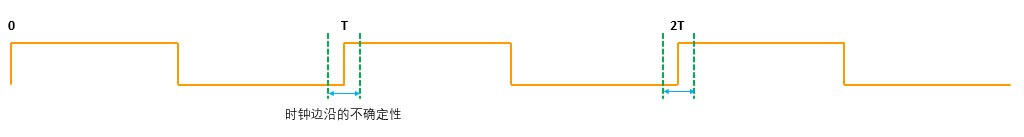

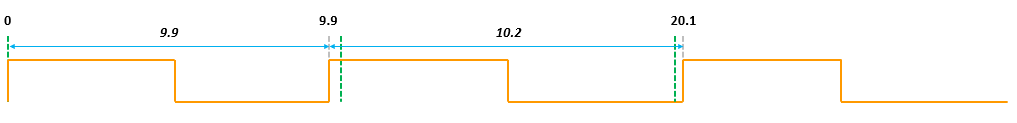

下圖顯示了時鐘抖動的基本概念。假定PLL生成時鐘頻率為100MHz,那么周期就是10ns。理想情況下,時鐘上升沿將出現在0ns、10ns、20ns、30ns等時刻。然后,PLL并非是一個理想時鐘源,所以,實際的時鐘上升沿可能會出現在0ns、9.9ns、20.1ns、29.8ns等時刻。換言之,實際是時鐘沿將出現在nT-jitter到nT+jitter的范圍內(這里n為整數)。需要注意的是圖中時鐘邊沿的不確定性對于時鐘上升沿和時鐘下降沿都是有效的,前者為整周期抖動,后者為半周期抖動。為方便起見,我們只討論整周期抖動。

時鐘抖動的幾種類型:

周期抖動

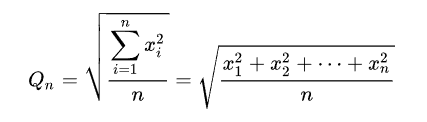

周期抖動的定義是實際時鐘周期與該時鐘的平均周期的偏差,即T1-Tavg,T2-Tavg,T3-Tavg,……,TN-Tavg(其中Tavg為平均周期)。這其實是周期抖動的計算方式之一,被稱為峰峰周期抖動(Peak-to-peakjitter)。周期抖動還可以采用RMS(Root MeanSquare,平方平均數,又名均方根)周期抖動來計算。計算公式如下圖所示。式中xi代表一個峰峰周期抖動。

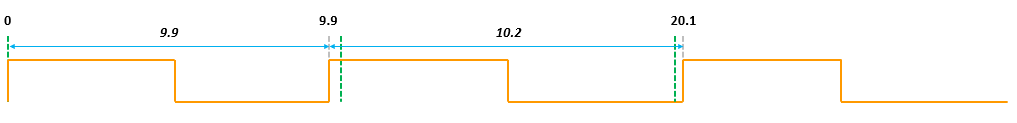

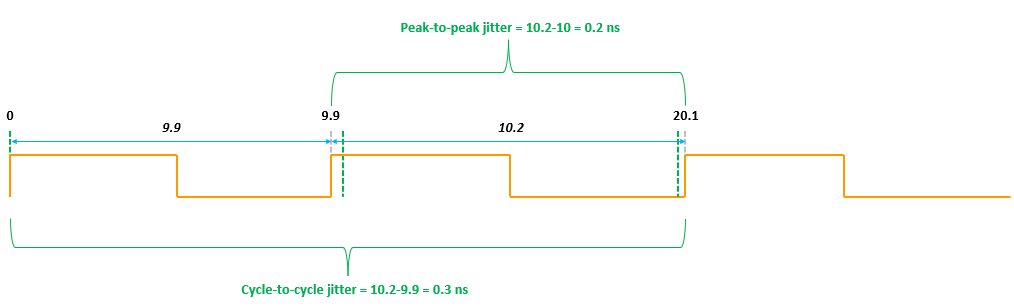

下圖顯示了峰峰周期抖動。圖中綠色虛線為理想時鐘上升沿位置,灰色虛線為實際上升沿位置。Tavg即為(9.9+10.2)/2,T1=9.9,T2=10.2,從而可計算出T1-Tavg和T2-Tavg。實際測量時要選擇多個樣本周期。

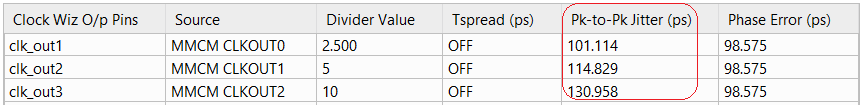

在Vivado Clocking Wizard IP中,會給出生成時鐘的峰峰周期抖動,如下圖所示。

相鄰周期抖動

相鄰周期抖動(Cycle-to-cycle jitter),顧名思義,指的是相鄰的兩個時鐘周期之間的周期長度差異,如下圖所示。第一個時鐘周期長度為9.9ns,與之相鄰的第二個時鐘周期長度為10.2ns,所以相鄰周期抖動為10.2-9.9=0.3ns。實際測量時要選擇多個周期樣本。需要注意的是相鄰周期抖動只關注兩個連續周期之間的周期長度變化,并不參考任何理想時鐘。不難發現,相鄰周期抖動就是峰峰周期抖動的差分:

(T1-Tavg)-(T2-Tavg)=T1-T2

最后,我們用一張圖即可展示峰峰周期抖動和相鄰周期抖動的差異,如下圖所示。

審核編輯:湯梓紅

-

pll

+關注

關注

6文章

832瀏覽量

135831 -

信號

+關注

關注

11文章

2826瀏覽量

77629 -

時鐘抖動

+關注

關注

1文章

62瀏覽量

16106 -

時序分析

+關注

關注

2文章

127瀏覽量

22739 -

周期抖動

+關注

關注

0文章

4瀏覽量

6087

原文標題:Cycle-to-cycle jitter 和 Peak-to-peak jitter什么區別?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論