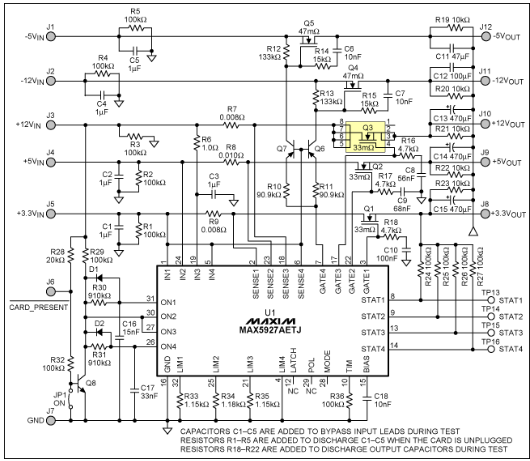

本文介紹的5通道電路雖然只采用了一個MAX5927A 4通道熱插拔控制器,卻可以實現3路正電源和2路負電源的熱插拔功能。圖1電路滿足以下負載供電和上電排序要求:

2A時,Ch1 = +3.3V (電路在 ≥ 3A時斷電)

1.6A時,Ch2 = +5V (電路在 ≥ 2.4A時斷電)

2A時,Ch3 = +12V (電路在 ≥ 3A時斷電)

150mA時,Ch4 = -12V (沒有電路斷電動作)

50mA時,Ch5 = -5V (沒有電路斷電動作)

啟動順為:通道2 (+5V)和通道3 (+12V)在低電平有效CARD_PRESENT變為低電平時立即接通。STAT2和STAT3在低電平有效CARD_PRESENT變為低電平10.8ms后,變為高電平。

通道1 (+3.3V)相對于通道2和通道3延遲11.8ms接通。通道1接通10.8ms后,STAT1變為高電平。

通道4 (-12V)和通道5 (-5V)相對于通道2和通道3延遲27.8ms接通。通道4和通道5接通10.8ms后,STAT4變為高電平。

鎖存故障管理。如果通道1至通道3中的任意一個出現錯誤,所有通道將被關閉,直到低電平有效CARD_PRESENT進入下一關斷和接通周期。

圖1. 5通道熱插拔電路控制3路正電源和2路負電源

雖然延遲要求和故障管理是針對這一設計的,但可以改變這一延遲以滿足其他時序要求。如果需要,故障管理可以改為自動重試模式。

熱插拔控制器選擇

之所以選擇MAX5927A,是由于它具有特殊的+15V絕對最大輸入電壓,而MAX5927是14V。如果12V供電電路采用了鏡像電路電感,斷路器過載時電路開路,使得12V電路可能出現供電電壓振鈴和過沖,那么這一電壓優勢就顯得非常重要。

接通時序

電阻R36 (在IC引腳10)將每一通道的接通時間設置為10.8ms ±2.8ms。在此期間,MAX5927A的內部低速比較器被禁止,使負載電容充電電流能夠達到通道1至通道3每一通道預設電流觸發值的兩倍,以滿足要求。在此期間,不需要觸發斷路器,負載電容很容易充電至最終值。在4kΩ和500kΩ之間調整R36,可以使啟動延時設置在400μs (最小)到50ms (最大)之間的任意值。在這一啟動時間的最后,STAT輸出從FALSE至TRUE的瞬變。STAT輸出為正,但也可以通過接地POL (引腳29)設置為負。

通過(R29 + R30) - C16時間常數將通道1相對于通道2和通道3延時11.8ms接通;可以增大C16以加大延時。通道1開始接通10.8ms后,STAT1變為高電平。

通過(R29 + R31) - C17時間常數將通道4和通道5相對于通道2和通道3延時28ms接通;可以增大C17以加大延時,或者減小R31,以縮短延時。通道4和通道5開始接通10.8ms后,STAT4變為高電平。

MODE置位(開引腳28)以配置MAX5927A為上電排序模式。

輸出電壓擺率

所有通道輸出電壓擺率設置為約1V/ms,數值與負載電容(C11至C15)值無關。可以修改C6至C10柵極電容值以改變擺率。擺率計算為ΔV/Δt = IGATE/CGATE。由于計算中并沒有包括FET柵極電容,因此,該方程并不是很精確。GATE1、GATE2和GATE3的柵極充電電流約為100μA。由于R10和R11電流的原因,Q4和Q5的柵極充電電流為30μA到50μA。負載電容充電電流可以計算為ICHARGE = CLOAD × ΔV/Δt。它由IGATE/CGATE = ICHARGE/CLOAD得出。電容C8至C10使通道1到通道3的輸出達到約1V/ms擺幅。沒有負載時,C13至C15以大約0.5A的電流充電,直到達到滿幅輸出。如果沒有C8至C10,輸出以兩倍于上面計算電流觸發值的電流對負載電容進行充電。電容C6和C7為10nF,使通道4和通道5的擺幅大約為1V/ms。

斷路器門限

21mV至27.5mV的慢速比較器閾值以及R7 = R9 = 8.3mΩ設置了通道1 (+3.3V)和通道3 (+12V)的限流值。默認值乘以1.13以及R33 = R35 = 1.15kΩ,得到大約3.1A至3.8A的最終值。21mV至27.5mV的慢速比較器閾值以及R8 = 10mΩ設置通道2 (+5V)限流值。默認值乘以1.15以及R34 = 1.18kΩ,得到大約2.415A至3.625A的最終值。通過調整檢測電阻R7到R9以及ISET電阻R33到R35來設置其他的限流值。可以從數據資料提供的曲線中確定默認乘數。限流斷路器不對低電流通道4 (-12V)和通道5 (-5V)提供保護。

內部上拉把LATCH置為高電平,將MAX5927A配置為鎖存故障管理。如果通道1至通道3中的任意一個出現故障,所有通道將被關斷,直到低電平有效CARD_PRESENT進入下一關斷和接通周期。

負電壓通道4和通道5

GATE4的柵極充電電流輸出是60μA至100μA,但是在對稱電路R4–Q7和R5-Q6中被分成30μA至50μA。GATE4的電壓可以比VIN4(3.3V)高5.3V,或者接通時≤+8.6V,關斷時接近0V。接通時,VQ6(BASE) = VQ7(BASE) = 3.3V,VQ6(EMITTER) = VQ7(EMITTER) ≈ 3.9V,關斷時為0V。R4和R5上相等的壓降使得Q6和Q7均分電流。R6和R7上相等的電流在Q4和Q5上產生相等的柵極驅動。關斷狀態下,GATE4 = 0V時的柵極驅動為0V。Q4和Q5的關斷速度取決于流過R6至R7的柵極放電電流。

FET選擇

所有通道,除了+12V通道,采用了SOT23封裝的n通道MOSFET直通晶體管;每一FET原理圖列出了VGS = 4.5V和TJ = +25°C時的最大RDS(ON)。VGS(max) = 20V (Si9410)的MOSFET被用于+12V通道。

總結

電路滿足所有的負載和上電排序設計要求—處理3個正電壓和2個負電壓通道,具有合適的順序接通時序、大于所需最小值的過電流觸發點,以及大約1V/ms的輸出擺率,達到了設計要求。

+5V和+12V通道的+3.3V延時 = 11.8ms (請參考圖2)

+3.3V通道的-5V延時 = 16.2ms (請參考圖3)

-5V負載關斷時間 = 1ms (請參考圖4和圖5)

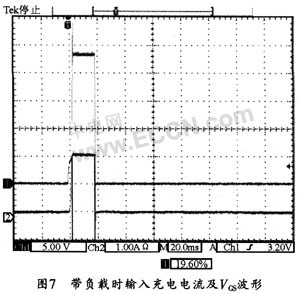

-12V負載關斷時間 = 4ns (請參考圖6和圖7)

-12V輸出電壓擺率 ≈ 1V/ms (請參考圖8)

-12V負載電容充電電流 ≈ 80mA (請參考圖9)

-5V輸出電壓擺率 ≈ 1V/ms (請參考圖10)

-5V負載電容充電電流 ≈ 55mA (請參考圖11)

+3.3V輸出電壓擺率 ≈ 1V/ms (請參考圖12)

+3.3V負載電容充電電流 ≈ 400mA (請參考圖12)

3A負載+3.3V接通,不觸發斷路器(請參考圖13)

+3.3V斷路器在3.22A時關斷(請參考圖14)

+5V負載電容充電電流 ≈ 500mA (請參考圖15)

+5V輸出電壓擺率 ≈ 1V/ms (請參考圖15)

2.4A負載+5V接通,不觸發斷路器(請參考圖16)

+5V斷路器在2.87A時關斷(請參考圖17)

+12V負載電容充電電流 ≈ 500mA (請參考圖18)

3A負載+12V接通,不觸發斷路器(請參考圖19)

+12V斷路器在3.1A時關斷(請參考圖20)

+5V在 ≈ 4A時啟動短路電路(請參考圖21)

+12V在 ≈ 5.7A時啟動短路電路(請參考圖22)

測試結果

圖2. +12V至+3.3V接通延時,沒有負載

Ch1 = Q8BASE(CARD_PRESENT), Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注釋:+12VOUT和+3.3VOUT之間有11.8ms延時。

圖3. +3.3V至-5V接通延時,沒有負載

Ch1 = Q8BASE, Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注釋:+3.3VOUT和-5VOUT之間有16.2ms延時。

圖4. -5V柵極相對于+3.3VGATE關斷,沒有負載

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +5VGATE, Ch4 = -5VGATE

注釋:-5V柵極關斷較慢;當1 < VGATE < 3V (2.5V,典型值)時,FET關斷。由此,正電壓通道關斷1.5ms至4ms后,-5V柵極完全關斷。

圖5. -5V負載關斷,50mA負載

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注釋:雖然由于輸出電容放電導致VOUT(-5V)沒有達到0V,-5V在1ms內下降至零。

圖6. -12V柵極關斷,沒有負載

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +12VGATE, Ch4 = -12VGATE

注釋:-12V柵極關斷較慢;當1 < VGATE < 3V (2.5V,典型值)時,FET關斷。由此,正電壓通道關斷1ms至4ms后,-12V柵極完全關斷。

圖7. -12V負載關斷,150mA負載

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注釋:雖然由于輸出電容放電導致VOUT(-12V)沒有達到0V,-12V輸入在4ms內降到零。

圖8. -12V接通波形

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注釋:接通順序,80Ω阻性負載 = 150mA。

圖9. -12V接通波形,沒有負載

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注釋:IIN(PK) = 80mA,對輸出電容充電。

圖10. -5V接通波形,100Ω阻性負載 = 50mA

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注釋:-5V擺率大約為1V/ms。

圖11. -5V接通波形,沒有負載

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注釋:IIN(PK) = 55mA,對輸出電容充電。

圖12. +3.3V接通波形,沒有負載

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

注釋:IIN(PK) = 400mA,對輸出電容充電;+3.3V擺率大約為1V/ms。

圖13. +3.3V接通波形,1.1Ω負載 = 3A

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

圖14. +3.3V過流關斷

Ch1 = STAT1, Ch2 = VGATE (+3.3V), Ch3 = +3.3VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注釋:IOUT和VOUT減小是由于輸出電容向恒阻負載放電。測得的觸發電流為3.22A。*

圖15. +5V接通負載電容充電電流,沒有負載

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

注釋:IIN(PK) = 500mA,對輸出電容充電。

圖16. +5V接通電流,2.083Ω負載 = 2.4A

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

圖17. +5V過流關斷

Ch1 = STAT2, Ch2 = VGATE (+5V), Ch3 = +5VOUT, Ch4 = IOUT(+5V) 0.5A/div

注釋:IOUT和VOUT減小是由于輸出電容向恒阻負載放電。測得的觸發電流為2.87A。

圖18. +12V啟動電流,沒有負載

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

注釋:IIN(+12Vpk) = 500mA,對輸出電容充電。

圖19. +12V接通電流,4Ω負載 = 3A

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

圖20. +12V過流關斷

Ch1 = STAT3, Ch2 = VGATE (+12V), Ch3 = +12VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注釋:IOUT和VOUT減小是由于輸出電容向恒阻負載放電。測得的觸發電流為3.1A。

圖21. 短路電路的+5V啟動電流

Ch1 = Q8BASE, Ch2 = +5VOUT, Ch3 = +5VGATE, Ch4 = IIN(+5V)

注釋:觸發時的4A負載電流。

圖22. 短路電路的+12V啟動電流

Ch1 = Q8BASE, Ch2 = VOUT, Ch3 = VGATE, Ch4 = IOUT

注釋:觸發時的5.7A負載電流。

測試PCB布板

圖23. 參考設計PCB元件布局

圖24. 頂層

圖25. 底層

審核編輯:郭婷

-

電源

+關注

關注

184文章

17718瀏覽量

250170 -

控制器

+關注

關注

112文章

16361瀏覽量

178046 -

熱插拔

+關注

關注

2文章

224瀏覽量

37349

發布評論請先 登錄

相關推薦

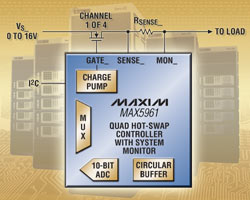

MAX5961 四通道熱插拔控制器,0至16V、提供10位電

基于LT1641的雙路熱插拔電路設計

5通道(3路+V和2路-V)熱插拔參考設計

MAX5970 0V至16V、雙通道熱插拔控制器,帶有10位

MAX5961 四通道熱插拔控制器(中文資料)

ADG658/ADG659:+3 V/+5 V/±5 V CMOS 4通道和8通道模擬復用器數據表

5通道(3路+V和2路-V)熱插拔參考設計

5通道(3路+V和2路-V)熱插拔參考設計

評論