Martin Murnane 和 Chris Augusta

逐次過近型(SAR)模數(shù)轉(zhuǎn)換器(ADCs)使用了許多新技術(shù)來改善分辨率。了解這些器件的工作原理對(duì)于預(yù)防故障和錯(cuò)誤很重要。本應(yīng)用筆記將從一般意義上討論使用SAR ADCs時(shí)易犯的錯(cuò)誤,以及更重要地,如何預(yù)防這些問題。

PuISAR的工作原理

ADI公司PulSAR?系列ADC使用內(nèi)部開關(guān)電容技術(shù)將SARADCs的分辨率擴(kuò)展到18位。這意味著在CMOS工藝上,不需要進(jìn)行成本高吊的薄膜激光調(diào)整。

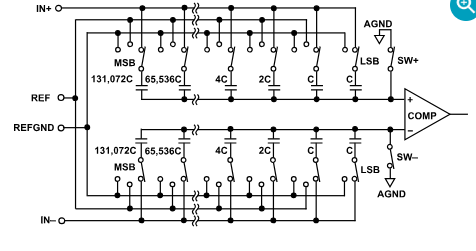

圖1顯示了AD7643的簡(jiǎn)化輸入級(jí)。AD7643是一款18位ADC,轉(zhuǎn)換速率可達(dá)1.25MSPS,它基于電荷再分配型數(shù)模轉(zhuǎn)換器(DAC),這在較新式SAR ADCs中頗為流行。SAR算法需要兩個(gè)階段來確定ADC輸出碼。第一個(gè)階段是采集階段,SW+和ISW-最初是關(guān)閉的。所有開關(guān)均連接到IN+和IN-模擬輸入,因此各電容用作采樣電容,以在輸入處采集模擬信號(hào)。第二個(gè)階段是轉(zhuǎn)換階段,SW+和SW-是打開的。輸入與內(nèi)部電客斷開,而作用于比較器輸入上,這將導(dǎo)致比較器不穩(wěn)定。從MSB開始,切換REF與REFGND之間元件陣列的各元件(這里將不詳述SAR算法),使比較器重新回到平衡狀態(tài),由此將產(chǎn)生代表模擬輸入信號(hào)的輸出碼。

圖1. AD7643簡(jiǎn)化原理圖

基準(zhǔn)電壓

在分析圖1的基準(zhǔn)電壓部分時(shí),我們將聚焦于使用PulSARADCs設(shè)計(jì)電路時(shí)易犯的錯(cuò)誤。請(qǐng)注意,當(dāng)計(jì)算輸出碼時(shí),輸人已與ADC的內(nèi)部元件斷開。這一點(diǎn)很重要, 它意味著在轉(zhuǎn)換階段,輸入(IN+和IN-)上出現(xiàn)的任何噪聲都不會(huì)影響所獲得的輸出碼。

在轉(zhuǎn)換階段,REF引腳與內(nèi)部開關(guān)電容結(jié)構(gòu)相連,因?yàn)榛鶞?zhǔn)電壓輸入處沒有采樣保持電路。此處出現(xiàn)的任何噪聲(在轉(zhuǎn)換階段)都會(huì)對(duì)輸出碼產(chǎn)生直接影響。如果因?yàn)樵谖粰z驗(yàn)期間噪聲增加,致使其中一位設(shè)置不正確,例如第6位應(yīng)當(dāng)是0但被設(shè)置為1,則所有后續(xù)位將被設(shè)置為1,以將DAC輸出降至正確的值。因此,輸出計(jì)算將不正確,導(dǎo)致輸出碼低6位為一串1,這些位一般被稱為“粘連位”(Stuck Bit)。為避免出現(xiàn)粘連位,采用一個(gè)極為穩(wěn)定的基準(zhǔn)電壓至關(guān)重要。

可以使用哪種類型的精密基準(zhǔn)電壓?

在PulSAR數(shù)據(jù)手冊(cè)“技術(shù)規(guī)格”部分中出現(xiàn)的-種誤解是外部基準(zhǔn)電壓與耗用電流。通常,對(duì)于低采樣率PulSAR(AD7685為250 kSPS),耗用電流值在數(shù)+μA范圍內(nèi);對(duì)于較高采樣率PulSAR(AD7621為3 MSPS),耗用電流值可達(dá)數(shù)百μA。這是平均電流,轉(zhuǎn)換器輸入驅(qū)動(dòng)是由基準(zhǔn)電壓驅(qū)動(dòng)電路提供ADC要求的最大電流。這可能是-FS或+FS,具體取決于ADC。實(shí)際上,任何基準(zhǔn)電壓都能提供數(shù)百μA電流,但有些基準(zhǔn)電壓在PulSAR高分辨率轉(zhuǎn)換器中并不實(shí)用。

低功耗基準(zhǔn)電壓(ADR12x、ADR36x)

低功耗基準(zhǔn)電壓一般是不可接受的,因?yàn)樵跈?quán)重最高有效位(MSB)判斷期間,它們通常缺乏能力建立。與相應(yīng)的緩沖式基準(zhǔn)電壓(如AD780、ADR43x和ADR44x)相比,這些基準(zhǔn)電壓的輸出阻抗通常較大。基準(zhǔn)電壓電路的動(dòng)態(tài)部分基本上是一RLC儲(chǔ)能電路,其中R位于ADC內(nèi)部(一些串聯(lián)開關(guān)電阻),C為基準(zhǔn)電壓儲(chǔ)能或去耦電容,L為基準(zhǔn)電壓本身的電感。在L來自精密基準(zhǔn)電壓源(如AD780)的情況下,PulSAR ADC設(shè)計(jì)師選用某一組R和C。使用這些值的結(jié)果是:當(dāng)系統(tǒng)被激勵(lì)后(激勵(lì)發(fā)生在位判斷過程中),系統(tǒng)達(dá)到臨界阻尼狀態(tài)。如果使用電感高得多(比好的緩沖式基準(zhǔn)電壓高100倍以上)的低功耗基準(zhǔn)電壓,將導(dǎo)致RLC電路處于欠阻尼狀態(tài),從而引起上述粘連位行為。

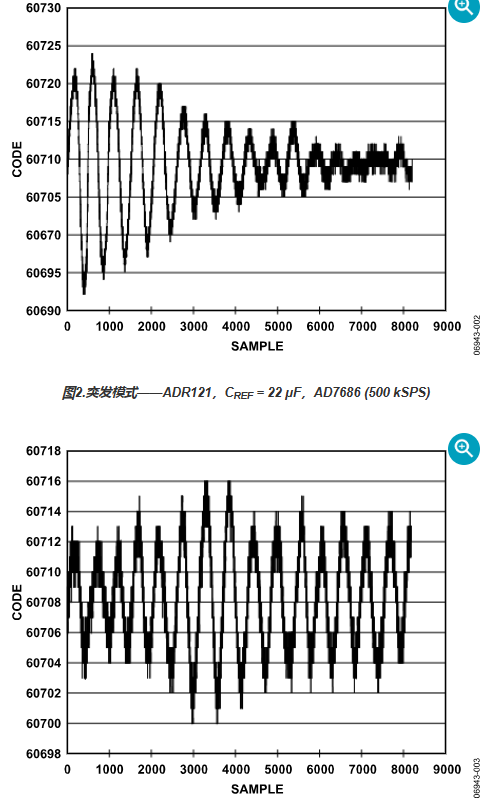

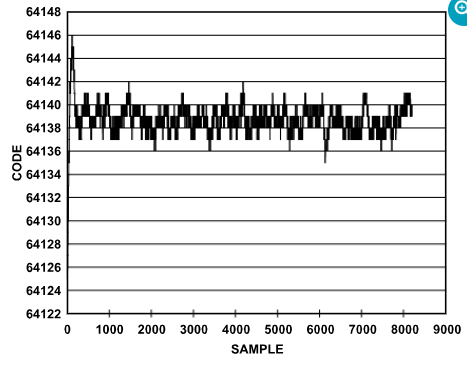

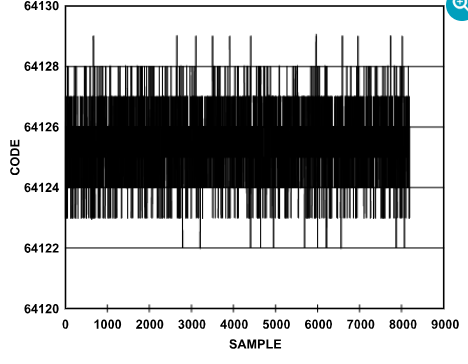

圖2至圖7顯示了一些低功耗基準(zhǔn)電壓的表現(xiàn)。請(qǐng)注意,這些圖中的術(shù)語“突發(fā)模式”是指這樣一種模式,即轉(zhuǎn)換控制信號(hào)保持非活動(dòng)狀態(tài),直至采集到8192個(gè)樣本之時(shí)才激活。這是對(duì)基準(zhǔn)電壓的最低要求,因?yàn)楫?dāng)ADC不進(jìn)行轉(zhuǎn)換時(shí),基準(zhǔn)電壓中便不存在動(dòng)態(tài)部分。我們使用了16位、500 kSPS PuISAR AD7686來獲得圖2至圖7中的數(shù)據(jù)。

直流測(cè)量數(shù)據(jù)一般以柱狀圖形式顯示,這對(duì)于顯示碼字躍遷(或躍遷噪聲)及峰峰噪聲非常有意義。不過,圖2和圖3則以時(shí)域顯示,以證明被測(cè)試的基準(zhǔn)電壓在動(dòng)態(tài)SAR轉(zhuǎn)換期間不能建立這一理論。

圖3.連續(xù)模式——ADRI21,CREF = 22 μF,AD7686 (500 kSPS)

圖2顯示了突發(fā)工作模式下欠阻尼RLC電路的經(jīng)典范例。圖3顯示了連續(xù)模式范例。如這兩幅圖所示,此基準(zhǔn)電壓從未完全建立至16位性能。在連續(xù)模式下,峰峰輸出碼仍與AD7686數(shù)據(jù)手冊(cè)中規(guī)定的性能相差約16采樣數(shù)或約4倍。

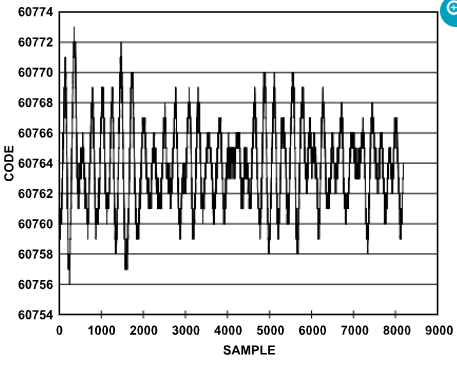

圖4顯示了使用ADR365時(shí)AD7686的性能。突發(fā)模式或連續(xù)模式對(duì)此基準(zhǔn)電壓而言并沒有真正不同,因?yàn)樗瑯訌奈赐耆⒅?6位性能。峰峰輸出碼同樣比AD7686的額定性能大4倍左右。

圖4. ADR365,CREF = 22 pμF,AD7686 (500 kSPS)

緩沖基準(zhǔn)電壓

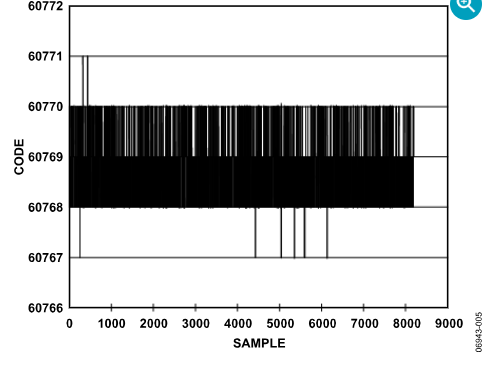

幾乎任何基準(zhǔn)電壓都可以使用適當(dāng)?shù)?a href="http://www.xsypw.cn/tags/放大器/" target="_blank">放大器(如AD8031或AD8605)進(jìn)行緩沖,以便獲得足夠的驅(qū)動(dòng)能力,因?yàn)榇藭r(shí)較高帶寬放大器的輸出中存在動(dòng)態(tài)部分。圖5顯示了把經(jīng)過AD8301緩沖的ADR365作為AD7686的基準(zhǔn)電壓進(jìn)行測(cè)試的輸出。

圖5.突發(fā)模式——ADR365, CREF = 22 μF,AD7686 (500 kSPS)

緩沖外部基準(zhǔn)電壓又會(huì)引發(fā)原來的功耗要求問題。較簡(jiǎn)單的解決方案是使用具有足夠驅(qū)動(dòng)的較佳基準(zhǔn)電壓,如AD780、ADR43x或ADR44x等。這種情況下可以使用任何低功耗基準(zhǔn)電壓,因?yàn)檫@些緩沖的串聯(lián)電感(通常)都很低。一個(gè)緩沖可以用來驅(qū)動(dòng)許多PulSARADC,因此這對(duì)多轉(zhuǎn)換器系統(tǒng)很有用。此外,在多轉(zhuǎn)換器應(yīng)用中,最佳方法是使用星形結(jié)構(gòu)的基準(zhǔn)電壓跡線,每個(gè)轉(zhuǎn)換器使用其自己的基準(zhǔn)電壓儲(chǔ)能電容。不建議從一組ADC中的第一個(gè)ADC開始進(jìn)行菊花鏈連接,因?yàn)锳DC基準(zhǔn)電壓可能會(huì)發(fā)生串?dāng)_。

低功耗基準(zhǔn)電壓(采樣率小于10 kSPS)

在低功耗、較低采樣率應(yīng)用中(例如必須使用低功耗基準(zhǔn)電壓的10 kSPS或更低應(yīng)用),可以在ADC的基準(zhǔn)電壓輸出之間使用一個(gè)小串聯(lián)電阻,如100。在突發(fā)工作模式下,為了讓流過這個(gè)電阻的電流趨于穩(wěn)定,最初幾次轉(zhuǎn)換可能需要丟棄。對(duì)于較高采樣率,通常無法進(jìn)行突發(fā)轉(zhuǎn)換,因?yàn)樾枰獊G棄的轉(zhuǎn)換太多。此外,隨著流過此電阻的電流增大到穩(wěn)態(tài)值,此電阻上的壓降在時(shí)域中表現(xiàn)為一個(gè)斜率,一般稱其為基準(zhǔn)電壓下降。

圖6顯示了在500kSPS較高采樣率應(yīng)用中使用202串聯(lián)電阻時(shí)的基準(zhǔn)電壓下降問題。請(qǐng)注意,最初幾百次轉(zhuǎn)換是在欠阻尼情況下,隨著采樣數(shù)增加,斜率表現(xiàn)為一個(gè)小的負(fù)值。

圖6.突發(fā)模式——ADR365,CREF = 22 μF,串聯(lián)電阻 = 20 Ω,AD7686 (500 kSPS)

圖7顯示10kSPS較低采樣率的情形。此時(shí)不存在欠阻尼問題,峰峰噪聲為5采樣數(shù),在性能上與AD7686很接近。

圖7.突發(fā)模式——ADR365,CREF = 22 μF,串聯(lián)電阻 = 20 Ω,AD7686 (10 kSPS)

為什么要使用較大去耦電容?

選定適當(dāng)?shù)幕鶞?zhǔn)電壓(或適當(dāng)?shù)幕鶞?zhǔn)電壓與緩沖電路)后,查看緩沖(運(yùn)算放大器)的數(shù)據(jù)手冊(cè),發(fā)現(xiàn)它建議避免使用大容性負(fù)載。但是,PuISAR ADC要求10 μF或更大的基準(zhǔn)電壓去耦電容(REF CAP)。 初看起來,這兩個(gè)要求自相矛盾。

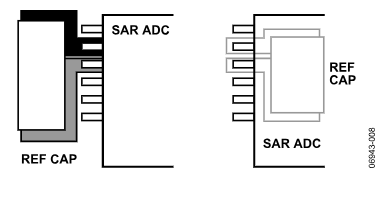

選定適當(dāng)?shù)幕鶞?zhǔn)電壓(或適當(dāng)?shù)幕鶞?zhǔn)電壓與緩沖電路)后,查看緩沖(運(yùn)算放大器)的數(shù)據(jù)手冊(cè),發(fā)現(xiàn)它建議避免使用大容性負(fù)載。但是,PuISAR ADC要求10 μF或更大的基準(zhǔn)電壓去耦電容(REF CAP)。 初看起來,這兩個(gè)要求自相矛盾。事實(shí)上,“去耦”這一術(shù)語有多種含義,用戶看到的PulSARADC基準(zhǔn)電壓(REF)引腳上的10 μF電容與電源(VDD、AVDD、DVDD、VIO、 OVDD)上的其它10 μF電容并不是回事。REF上的電容不是旁路電容,而是SAR ADC的——部分,這個(gè)電容不適合放在硅上。在位判斷期間,由于各位會(huì)在數(shù)十納秒或更快的時(shí)間內(nèi)建立,因此此處所示的儲(chǔ)能電容(REF CAP,參見圖8)是用來補(bǔ)充內(nèi)部CDAC的電荷,從而與內(nèi)部電容陣列上的電荷一起平衡比較器。隨著二進(jìn)制位加權(quán)過程的向前進(jìn)行,將從此電容中不斷提取少量電荷。當(dāng)然,內(nèi)部電容陣列只是其中(約為15 pF至60 pF,取決于ADC)的很小一 部分,但這些較大值儲(chǔ)能電容需要滿足SAR位判斷建立時(shí)間要求。關(guān)于在位判斷過程中電荷發(fā)生了什么事情等一些錯(cuò)綜復(fù)雜的細(xì)節(jié)問題,這不屬于本應(yīng)用筆記的討論范圍。

圖8.基準(zhǔn)電壓電容位于SAR ADC同側(cè)或位于PCB后側(cè)

儲(chǔ)能電容大小不足也會(huì)引起粘連位問題。電容的放置和類型同樣很重要。為避免基準(zhǔn)電壓下降,需要使用等效串聯(lián)電阻(ESR)低的電容。近年來,已經(jīng)有非常好的陶瓷X5R介電電容可以在0603封裝尺寸下提供10正容值。對(duì)于許多PulSAR ADC,通過降低某些性能要求,即微分非線性(DNL), 可以減小基準(zhǔn)電壓電容值。

布局

建議將一個(gè)電容直接放在ADC的基準(zhǔn)電壓引腳上,用來消除開關(guān)電容瞬變。要求使用高質(zhì)量電容(例如鉭電容或X5R型陶瓷電容,不推薦使用NPO電容),因?yàn)檫@是一個(gè)電荷存儲(chǔ)電容,而不是旁路電容,電容值可以在4.7 μF至22 μF范圍內(nèi)。請(qǐng)注意,某些數(shù)據(jù)手冊(cè)規(guī)定了開啟建立時(shí)間,這表明REF引腳上使用了一個(gè)特殊基準(zhǔn)電壓電容。請(qǐng)參考相關(guān)PulSAR數(shù)據(jù)手冊(cè)的“技術(shù)規(guī)格”部分以了解詳細(xì)信息。

布局開始時(shí),考慮具有SAR ADC器件的PCB布局,并考慮在ADC基準(zhǔn)電壓引腳上放置一個(gè)電容。首先將該電容放在這些引腳附近,然后將基準(zhǔn)電壓放在電容附近,最后放在放大器附近(參見圖8)。

布局中還需要一條粗跡線,以減小電路中的阻抗。ADC的基準(zhǔn)電壓輸入具有動(dòng)態(tài)輸入阻抗,意味著對(duì)此引腳的輸入必須用低阻抗源驅(qū)動(dòng)。請(qǐng)注意,如果基準(zhǔn)電壓是經(jīng)緩沖進(jìn)入REF引腳,則緩沖輸出阻抗必須很低。這也同樣適用于模擬輸入引腳。

放大器選擇

大部分PulSAR數(shù)據(jù)手冊(cè)都對(duì)放大器做了詳細(xì)說明。需要注意的一些主要問題是低噪聲電平和低輸出阻抗。輸入信號(hào)建立時(shí)間也是一項(xiàng)重要參數(shù),因此要求放大器具有高壓擺率性能。符合這一要求的放大器有:ADA4841-1、AD8021、ADA4899-1、AD8099和ADA4941-1。

ADA4841-1和AD8021能驅(qū)動(dòng)PuISAR ADC,具有高帶寬和良好的壓擺率,是出色的ADC驅(qū)動(dòng)器選擇。ADA4899-1也是不錯(cuò)的替代之選,具有出色的壓擺率和良好的帶寬,但需要消耗更多電流。還有其它放大器也適合各種應(yīng)用,例如AD8099,它具有極低的噪聲密度,因此適合18位ADC應(yīng)用。但是,這款器件不是單位增益穩(wěn)定型,雖然可以將其配置成單位增益穩(wěn)定型,但它的電流消耗很高(16 mA)。不過,它具有一個(gè)(禁用 )功能,可以利用該功能減小電流消耗,以適合便攜式應(yīng)用。ADA4941-1是單端轉(zhuǎn)差分應(yīng)用的另一個(gè)選擇,具有5 V輸入電壓,例如可用于PuISAR 18位ADC AD7982。

結(jié)論

了解SAR ADC的工作原理對(duì)于避免新設(shè)計(jì)中易犯的錯(cuò)誤非常重要。本應(yīng)用筆記所列出的問題在新設(shè)計(jì)中是很常見的。

審核編輯:郭婷

-

放大器

+關(guān)注

關(guān)注

143文章

13619瀏覽量

213851 -

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

53文章

8263瀏覽量

146696 -

adc

+關(guān)注

關(guān)注

98文章

6525瀏覽量

545224

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【絕對(duì)干貨】高精度逐次逼近型ADC支持電路的設(shè)計(jì)和故障排除

ADC外圍電路的設(shè)計(jì)

ADC外圍電路設(shè)計(jì)方法

實(shí)用模擬電路設(shè)計(jì)技術(shù)Section4高速采樣ADC

高速ADC時(shí)鐘抖動(dòng)的影響的了解

DN1013-了解時(shí)鐘抖動(dòng)對(duì)高速ADC的影響

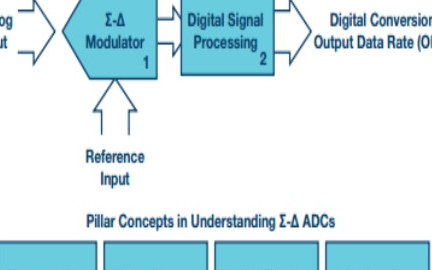

一文了解Σ-Δ型ADC拓?fù)浣Y(jié)構(gòu)的基本原理

了解PulSAR ADC支持電路

了解并延續(xù)∑-ΔADC的安全運(yùn)行

了解PuISAR ADC支持電路

了解PuISAR ADC支持電路

評(píng)論