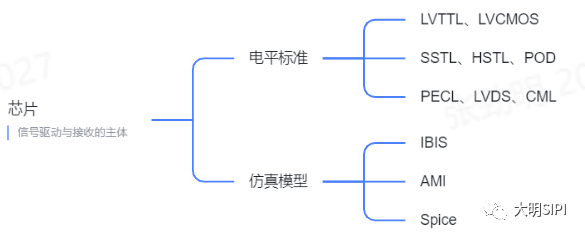

這一節開始我們介紹信號完整性的另一個要素--芯片(驅動、接收器件),主要涉及到如下內容:

有一定基礎的同學也可以直接略過此部分內容,但我覺得在介紹IBIS模型、介紹SIPI仿真之前,還是有必要先講一下各種電平標準,這樣有助我們更好的完成信號完整性仿真和分析。

驅動和接收器參數

在介紹具體的電平標準前需要介紹一些概念:

-

驅動器:

- 輸出高電平(Voh):保證邏輯門的輸出為高電平時的輸出電平的最小值,邏輯門的輸出為高電平時的電平值都必須大于此Voh。也就是說輸出高電平的最低值可能會達到Voh。

- 輸出低電平(Vol):保證邏輯門的輸出為低電平時的輸出電平的最大值,邏輯門的輸出為低電平時的電平值都必須小于此Vol。也就是說輸出低電平的最高值可能會達到Vol。

-

接收器:

- 輸入高電平(Vih):保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高于Vih時,則認為輸入電平為高電平。

- 輸入低電平(Vil):保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低于Vil時,則認為輸入電平為低電平。

- 閥值電平(Vt):數字電路芯片都存在一個閾值電平,就是電路剛剛勉強能翻轉動作時的電平。它是一個界于Vil、Vih之間的電壓值,對于CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸出,則必須要求輸入高電平> Vih,輸入低電平

對于一般的邏輯電平,以上參數的關系如下:Voh > Vih > Vt > Vil > Vol。

我們在做SI分析時,用Vih、Vil來衡量仿真波形的高、低電平的噪聲裕量。在考慮不同邏輯電平接口之間的互連時我們必須充分考慮驅動器的Voh和接收器的Vih以及驅動器的Vol和接收器的Vil之間的裕量是否足夠,如果裕量很小,那么兩種接口的電平對接就存在一定的風險。

常用的邏輯電平有 TTL、CMOS、LVTTL、LVCOMS、SSTL、HSTL、CML、ECL、PECL、LVPECL、LVDS等。這些邏輯電平接口都有自身的結構特點,為了能夠獲得最優的信號質量我們必須對所使用的電平接口輸入輸出結構有充分的了解。只有如此才能夠設計出傳輸線和驅動、接收器完好匹配的電路。另外,我們需要對常用的邏輯電平的電氣特性有充分了解,這有助我們判定仿真測試得到的結果是否滿足要求。在實際的設計中經常遇到不同電平接口之間的互連,這就導致驅動器和接收器的共模電平、電壓擺幅很可能不相同,為了數據的安全可靠傳輸就需要考慮各種電平接口之間的轉換。

在各種邏輯電平的互連設計中,需要尊需以下基本原則:

-

電平關系, 驅動器件的輸出電壓必須處在負載器件所要求的輸入電壓范圍,包括高、低電壓值。應保證合格的噪聲容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax≥0.4V),并且輸出電壓不超過輸入電壓允許范圍,否則有可能導致器件損壞。

-

驅動能力 ,驅動器件必須能對負載器件提供灌電流最大值。驅動器件必須對負載器件提供足夠大的拉電流,關系到驅動器的帶負載能力和總線速率。對于一般驅動器來說驅動電流都是mA級別的,相比而言各種邏輯電平的輸入電流都是uA級的,對于TTL、CMOS等傳統的低速接口來說可以驅動很多器件工作。高速的SerDes鏈路大部分都是CML電平而且都是點到點的拓撲結構,此時更加關注信號的邊沿變化率,如果邊沿變化率太緩可能無法支持過高的信號速率。但也要注意長的布線鏈路也會造成比較大的損耗,這就需要驅動器可以通過驅動能力的調整來改善信號的幅度,對于高速serdes來說往往不僅僅是驅動能力的問題,還需要配合加重、均衡等技術來改善信號質量。

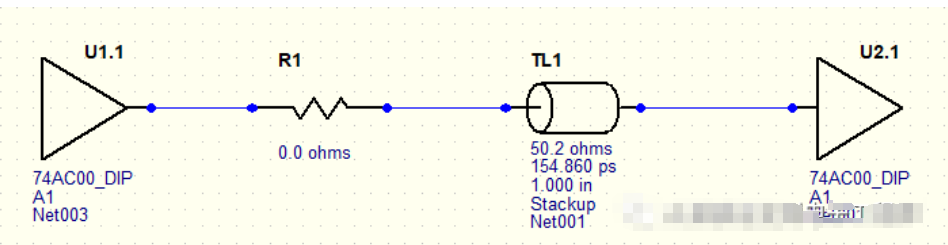

從另一方面驅動能力反映的是驅動器的 輸出阻抗 ,從阻抗方面理解更有利于我們 保證驅動器和傳輸線之間的阻抗匹配 。

-

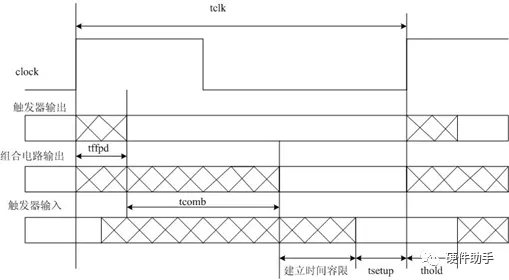

時延特性, 在高速信號進行邏輯電平轉換時,往往會帶來一定的延時。而且同一器件同一總線不同管腳的輸出延時會有一定的偏差,這一延時偏差會很大程度上限制總線速率,時序設計時一定要充分考慮。

-

如果兩種電平不能直接相連,則需要借助電平轉換芯片。選用電平轉換邏輯芯片時應慎重考慮,反復對比。通常邏輯電平轉換芯片為通用轉換芯片,可靠性高,設計方便,簡化了電路,但對于具體的設計電路一定要考慮以上三種情況,合理選用。需要充分考慮電平轉換芯片對上升/下降時間的影響,應保證Tplh和Tphl滿足電路時序關系的要求和EMC的要求。

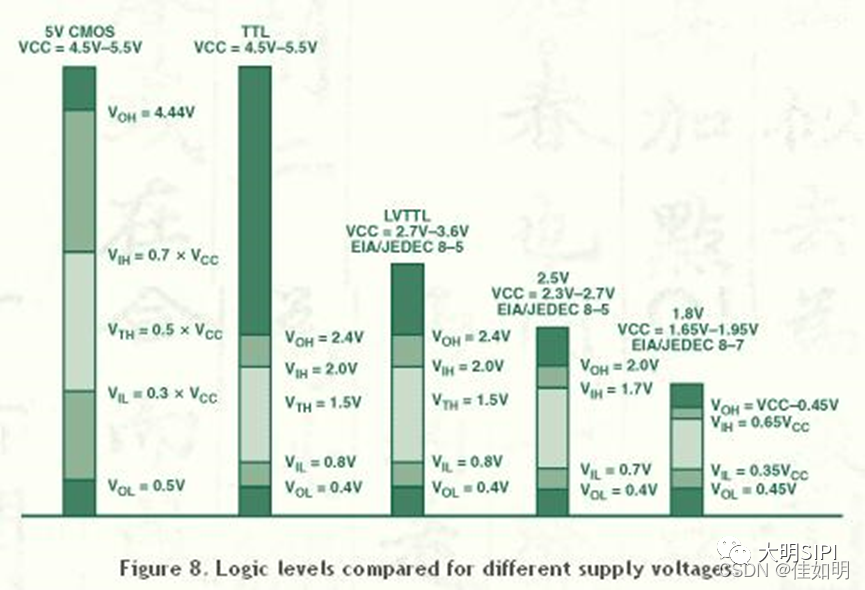

TTL 、CMOS電平

TTL和CMOS的邏輯電平是比較傳統的低速電平接口,不能提供很快的開關速度,按典型電壓可分為四類:5V系列、3.3V系列,2.5V系列和1.8V系列。5V系列比較通用被稱為TTL或者CMOS電平,3.3V及以下的邏輯電平被稱為低電壓邏輯電平,常用的為LVTTL或LVCMOS電平。一般的數字設計基礎教材中都有詳細介紹。這里給出不同系列的邏輯電平之間的邏輯電平對比,并簡要分析何種情況下不同電平接口可以直接互連,什么情況下不能直接互連。

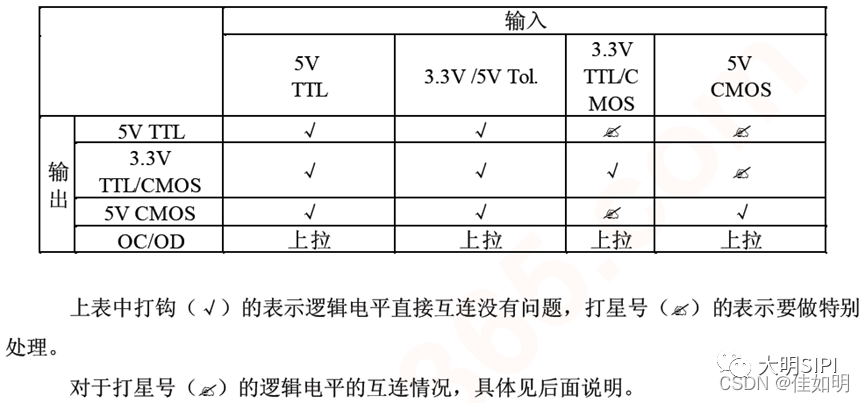

常用的TTL和CMOS電平分類有:5V TTL、5V CMOS、3.3V TTL/CMOS、3.3V/5VTol.、和OC/OD門。其中:

- 3.3V/5V Tol.是指輸入是3.3V邏輯電平,但可以忍受5V電壓的信號輸入。

- 3.3V TTL/CMOS邏輯電平表示不能輸入5V信號的邏輯電平,否則會出問題。

3.3V和5V邏輯電平的互連

注意某些5V的CMOS邏輯器件,它也可以工作于3.3V的電壓,但它與真正的3.3V器件(是LVTTL電平)不同,比如其VIH是2.31V(=0.7×3.3V,工作于3.3V)而不是2.0V,因而與真正的3.3V器件互連時工作不太可靠。因為這種接法無形中減小了高電平的噪聲裕量,在進行信號完整性仿真時需要特別注意。

值得注意的是有些器件有單獨的輸入或輸出電壓管腳,此管腳接3.3V的電壓時,器件的輸入或輸出邏輯電平為3.3V的邏輯電平信號,而當它接5V電壓時,輸入或輸出的邏輯電平為5V的邏輯電平信號,此時應該按該管腳上接的電壓的值來確定輸入和輸出的邏輯電平屬于哪種分類。

** OC/OD輸出加上拉電阻可以驅動所有邏輯電平。**

5V TTL和3.3V/5VTol.可以被除了2.5V、1.8V外的所有邏輯電平驅動

由此得到以下邏輯電平匹配表格:

2.5V和3.3V之間的邏輯轉換。

-

3.3V TTL/CMOS邏輯電平驅動2.5V CMOS邏輯電平

2.5V的邏輯器件有LV、LVC、AVC、ALVT、ALVC等系列,其中前面四種系列器件工作在2.5V時可以容忍3.3V的電平信號輸入,而ALVC不行,所以可以使用LV、LVC、AVC、ALVT系列器件來進行3.3VTTL/CMOS邏輯電平到2.5V CMOS邏輯電平的轉換。

-

2.5V CMOS邏輯電平驅動3.3V TTL/CMOS邏輯電平

2.5V CMOS邏輯電平的VOH為2.0V,而3.3VTTL/CMOS的邏輯電平的VIH也為2.0V,所以直接互連的話可能會出問題(除非3.3V的芯片本身的VIH參數明確降低了)。此時可以使用雙軌器件SN74LVCC3245A來進行2.5V邏輯電平到3.3V邏輯電平的轉換。

-

驅動器

+關注

關注

52文章

8236瀏覽量

146369 -

接收器

+關注

關注

14文章

2472瀏覽量

71913 -

信號完整性

+關注

關注

68文章

1408瀏覽量

95488 -

AVC

+關注

關注

0文章

21瀏覽量

10998 -

CMOS電平

+關注

關注

0文章

18瀏覽量

7191

發布評論請先 登錄

相關推薦

2011信號及電源完整性分析與設計

高速串行總線的信號完整性驗證

介紹信號完整性的另一個要素—芯片

介紹信號完整性的另一個要素—芯片

評論