3.3V 直流母線在寬帶網絡系統中廣受歡迎,用于各種較低電壓,為 DSP、ASIC 和 FPGA 供電。這些較低的電壓范圍為1V至2.5V,通常需要高負載電流。為了保持高轉換效率,降壓轉換器的功率MOSFET導通損耗必須降至最低。問題在于,3.3V總線還頻繁使用亞邏輯電平MOSFET。這種MOSFET具有相對較高的RDS(ON),將轉換器的滿載效率限制在 85% 左右。更有效的解決方案是使用邏輯電平MOSFET,其R值非常低DS(ON)但需要一個 5V 電源。LTC1876 通過將一個 1.2MHz 升壓型穩壓器 (其從一個 5.3V 輸入產生一個 3V 偏置電源)與兩個提供低電壓輸出的降壓型控制器相結合,允許使用邏輯電平 MOSFET。通過將所有三個穩壓器集成到單個 IC 中,LTC1876 實現了小型且成本低廉的高效電源。

設計示例

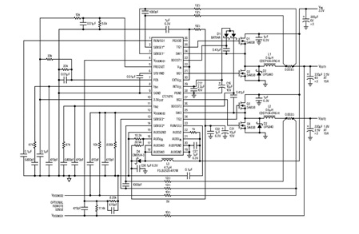

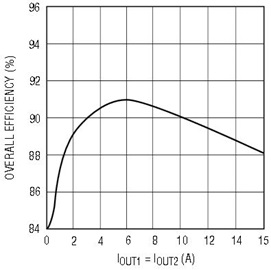

圖1所示為采用2.5V輸入提供15.1V/8A和15.3V/3A的設計。因為 LTC1876 為 MOSFET 柵極驅動提供了一個 5V 偏置,所以 RDS(ON)MOSFET Si4838 (典型值為 2.4mΩ) 可用于實現高效率。圖2顯示,在很寬的負載范圍內,總效率高于90%。

圖1.LTC1876 設計可在 3A 和 3A 時將 2.5V 轉換至 15.1V,在 8A 時轉換 15.<>V。

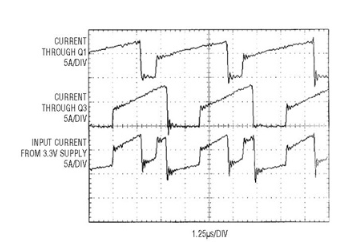

圖2還顯示,該設計的輕載效率超過84%。這是 LTC1876 突發模式操作的一個直接優勢。兩個降壓通道的異相運行進一步提高了效率。第一通道的頂部MOSFET與第二通道的MOSFET異相180°,從而最大限度地減少了通過輸入電容的RMS電流。這大大降低了與輸入電容ESR相關的功率損耗。圖3顯示了此操作的詳細電流波形。?

圖2.設計效率高,如圖1所示。

圖3.每個開關穩壓器的峰值電流為5A,但輸入端的總紋波仍然僅為5A,使C最小化在要求。

結論

LTC1876 采用三種技術,從一個低輸入電壓高效地為低電壓 DSP、ASIC 和 FPGA 供電。第一種技術使用內部升壓穩壓器為MOSFET柵極驅動提供單獨的5V電壓。其次,其突發模式操作可在輕負載下實現高效率。最后是異相技術,可最大限度地減少輸入RMS損耗并降低輸入噪聲。完整的穩壓器電路保持小巧且價格低廉,因為所有三個開關穩壓器(一個升壓穩壓器和兩個降壓控制器)都集成在單個IC中。對于提供單獨 5V 或輸入電源大于 5V 的系統,內部升壓穩壓器可用于提供開關電流高達 1A 的第三個升壓輸出。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8736瀏覽量

147537 -

MOSFET

+關注

關注

147文章

7208瀏覽量

213759 -

asic

+關注

關注

34文章

1205瀏覽量

120599

發布評論請先 登錄

相關推薦

使用DC / DC轉換器為ADC供電

模擬開關充當DC / DC轉換器

提供5.1V / 9.1V / 12.1V輸出的高效率降壓DC/DC轉換器

一個從5V到4V的DC-DC轉換器

FR9206 SOT23-6 3A同步降壓芯片 DC-DC轉換器

4.5V至28V輸入、3A 輸出、同步 降壓 DC-DC轉換器TPS5433xA數據表

4.5V至28V輸入、3A 輸出、同步降壓DC-DC轉換器TPS54335-2A數據表

高效DC/DC轉換器從15.3V背板提供兩個3A輸出

高效DC/DC轉換器從15.3V背板提供兩個3A輸出

評論