幾十年來,計算機已經從占據整個房間的機器縮小到可以戴在手腕上的設備。研究人員專注于增加單個計算機芯片上晶體管數量的密度,并且通常依賴 SOC(或片上系統)來降低成本并使設備更緊湊。但是我們開始接近我們可以將芯片的某些部分做得多小的物理極限,而其他部分在某些用例中也同樣有效,即使它們不是最小的、最前沿的設計。

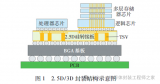

這就是芯片封裝的重要性所在。封裝是在芯片或電路板上連接集成電路的過程,隨著電子設備的縮小和芯片組件本身變得越來越小,封裝變得越來越復雜。IBM 于 2021 年宣布了一款組件尺寸僅為 2 納米的芯片。隨著半導體行業轉向新的芯片構造方法,封裝技術的進步將變得越來越重要。這種轉變的一個關鍵部分是小芯片技術的興起。

對小芯片的研究表明了計算的未來可能是什么樣子。有許多新興用例(如訓練和運行復雜的 AI基礎模型)可以從新芯片設計中受益,而不是專注于構建單片 SOC。chiplet 背后的概念有效地將 SOC 分解成多個復合部分(如 GPU、CPU、I/O 和內存),并構建對特定任務更有效的 chiplet 系統。

就人工智能而言,你可以構建一個小芯片系統,將處理單元、人工智能加速器和內存堆棧結合在一起,所有這些都在通信和共享數據,就好像它們都在同一個芯片上一樣。

將小芯片從研究轉向生產需要克服的最大障礙之一是小芯片在封裝過程中粘合在一起的方式。迄今為止,大多數設計都使用位于金屬焊盤頂部的焊料或焊料和銅的組合將小芯片連接在一起。這些方法導致鍵合在 150 到 30 微米之間,需要非常緊密的焊接才能有效。但是 IBM 和 ASMPT(半導體生產硬件和軟件的主要供應商)的一組研究人員一直在研究一種新的方法來結合小芯片,從而大大減少空間量。

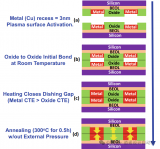

在本周于 2023 年 IEEE 電子元器件與技術會議 (ECTC) 上發表的一篇論文中,1個研究人員概述了他們的混合鍵合概念。他們的方法在不使用焊料的情況下,將銅和氧化物熔合在只有幾個原子厚的層中。結果是小芯片之間的鍵合僅為 0.8 微米左右,比目前正在測試的其他方法要薄得多。

新的混合鍵合方法有可能增加小芯片之間的數據吞吐量,以及可以安裝在給定空間中的小芯片數量,從而使小芯片系統更像單個 SOC。例如,它對于將 chiplet 技術集成到更小的設備以及提高 chiplet 的性能或其能效具有重大意義。

在團隊的方法中,最艱巨的挑戰是確保粘合牢固,以極小的規模去除潛在的水分或氣泡。粘合層之間只有三個水分子就足以破壞層與層之間的連接。消除這種危險以及氣泡,同時保持粘合在一起的各層表面清潔——并確保這一過程能夠可靠地一次又一次地進行——是該團隊在研究中尋求克服的主要挑戰。

該團隊的方法類似于芯片晶圓的鍵合方式,這是目前的標準行業慣例——只是規模相當小——他們一直在使用專為芯片到晶圓鍵合而設計的 ASMPT 機器來執行他們的測試。雖然該團隊認為他們的方法可以大規模構建小芯片并將其結合在一起,但在研究 ASMPT 系統的工具方面還需要做更多的工作。

未來的系統將需要新的方法來解決計算問題,因為它們變得更加復雜和多樣化,而小芯片提供了解決這些問題的潛在途徑。通過混合鍵合,創建的系統就好像它們是單個芯片的一部分一樣,未來變得更加清晰。

審核編輯:劉清

-

加速器

+關注

關注

2文章

806瀏覽量

38044 -

封裝技術

+關注

關注

12文章

553瀏覽量

68023 -

SoC設計

+關注

關注

1文章

148瀏覽量

18809 -

人工智能

+關注

關注

1796文章

47643瀏覽量

239937 -

chiplet

+關注

關注

6文章

434瀏覽量

12619

原文標題:IBM,分享混合鍵合新技術

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

帶你一文了解什么是引線鍵合(WireBonding)技術?

電子封裝 | Die Bonding 芯片鍵合的主要方法和工藝

混合鍵合技術:開啟3D芯片封裝新篇章

IBM分享混合鍵合新技術

IBM分享混合鍵合新技術

評論