寫(xiě)testbench最最核心的部分就是發(fā)激勵(lì),今天用一個(gè)簡(jiǎn)單的示例來(lái)介紹如何在uvm里給RTL發(fā)激勵(lì)。

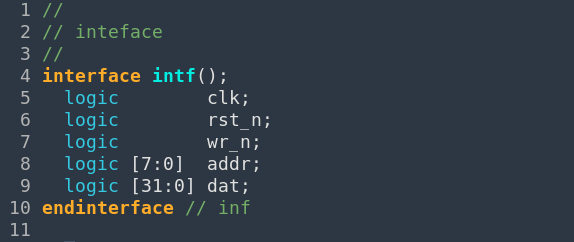

第一步,先來(lái)定義interface,如下。

interface是sv的一個(gè)關(guān)鍵字,級(jí)別等同于module,所以與module是并列的,一般單獨(dú)寫(xiě)一個(gè)文件。

第二步,在testbench里實(shí)例化interface,并連接interface與RTL。

既然interface與module同級(jí),實(shí)例化時(shí)就不能忘記括號(hào)。由于大部分信息不需要引到interface端口上,所以看上起來(lái)有點(diǎn)不太像模塊例化。

第三步,把interface實(shí)例化對(duì)象傳遞到uvm。

在run_test()之前,通過(guò)uvm里的函數(shù)uvm_config_db::set()函數(shù)把interface存儲(chǔ)到指定的存儲(chǔ)路徑。

第四步,在uvm里讀取interface,并存儲(chǔ)到virtual interface里。

從名字上看,config_db是一種存儲(chǔ)配置信息的數(shù)據(jù)庫(kù)(類(lèi)似全局變量,可以想象成一個(gè)關(guān)聯(lián)數(shù)組),要正確存儲(chǔ)和讀取數(shù)據(jù),需要類(lèi)型和存儲(chǔ)路徑同時(shí)正確。v_intf有點(diǎn)像是一個(gè)指針,把讀取的數(shù)據(jù)存到這個(gè)指針對(duì)應(yīng)的存儲(chǔ)空間里。

第五步,驅(qū)動(dòng)v_intf的信號(hào)。

先初始化所有的信號(hào)。由于virtual interface指向了前面實(shí)例化的interface,給virtual interface賦值,等同于給真實(shí)的interface的信號(hào)賦值。

隨機(jī)發(fā)一些激勵(lì),這部分與純sv的寫(xiě)法沒(méi)有差別。

仿真結(jié)果

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7525瀏覽量

164162 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83878 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59903 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19205 -

Module

+關(guān)注

關(guān)注

0文章

68瀏覽量

12867

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

華為深耕海外版圖 將在日本設(shè)立第二個(gè)研發(fā)中心

邵貝貝書(shū)中第二個(gè)例子的問(wèn)題

請(qǐng)問(wèn)為什么第二個(gè)周期更長(zhǎng)?

如何使用ESP32并添加第二個(gè)無(wú)線(xiàn)電模塊?

如何為SPIFFS使用第二個(gè)SPI閃存芯片?

電腦第二個(gè)硬盤(pán)怎么裝

谷歌發(fā)布AndroidQ的第二個(gè)測(cè)試版 繼續(xù)對(duì)折疊屏適應(yīng)

蘋(píng)果macOS Catalina 10.15.1第二個(gè)Beta今天發(fā)布

Zoom營(yíng)收增幅可能連續(xù)第二個(gè)季度超過(guò)300%

ASM宣布在新加坡開(kāi)設(shè)第二個(gè)車(chē)間

開(kāi)發(fā)ATtiny微處理器編程器的第二個(gè)版本

我的第二個(gè)UVM代碼—連接interface

我的第二個(gè)UVM代碼—連接interface

評(píng)論