終端端接對于信號完整性有著重要的意義,它和源端匹配一樣都是解決信號完整性問題的重要手段。所以無論是高速的并行總線如DDR,還是高速串行總線如Serdes都會采用終端的端接。DDR的ODT功能就是典型的終端端接,而大多數Serdes采用的CML電平,在芯片內部的P、N兩根線上都有50ohm的端接。

01

終端端接

源端匹配的作用就是:即使終端沒有匹配,信號到達終端發生反射,返回的到源端的反射信號也會由于源端阻抗匹配而不會發生反射,從而消除了二次反射和多次反射的影響。

而終端端接則是讓終端負載阻抗與傳輸線阻抗相匹配,使得初始電波進入到傳輸線直至到終端被接收器件接收一直處于匹配狀態整個傳輸過程中都不會發生反射。

(a) (b)

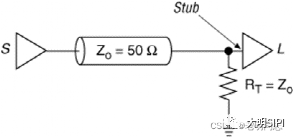

終端端接有上圖所示兩種方式:(a)端接電阻RT 靠近負載端下拉到地;(b)需要兩個端接電阻,R1 、R2 分別接到VCC和地。滿足R1 ||R2 = Z0 或RT=Z0 即可實現阻抗匹配。

假設上面兩種情況下源端阻抗和傳輸線匹配,接口的IO電壓為VCC。那么進入傳輸線的初始電波只有1/2VCC。對于(a)接收的信號擺幅就是從0V到1/2VCC,其共模電平為VCC/4。對于(b)當R1=R2 時接收信號的擺幅就是1/4VCC到3/4 VCC,共模電平為1/2VCC 。

基于兩種終端端接的上述特點,我們來分析兩種情況的應用。

對于情況(a)來說無論是過驅動還是欠驅動情況,信號的低電平為0,高電平要小于VCC。是否能夠應用這種匹配方式要看接收器件的電平接口VIL和VIH的值。比如,3.3V LVTTL電平的VIH = 2.0V,當欠驅動的情況下接收端的幅值肯定會低于1.65V,此時可能導致接收高電平錯誤。

對于(b)由于其共模電平為1/2VCC,接收信號高低電平以1/2VCC為中心,這種匹配方式適合用于SSTL或者HSTL這種基于比較器的結構的電平接口。DDR2、DDR3以及QDR的DQ信號內部的ODT端接就采用(b)所示的戴維南端接。

需要注意的是,端接的值并不一定非要和傳輸線阻抗完全匹配。端接阻值越小時接收器件接收的信號幅值也就越小,端接阻值越大時接收器接收信號幅值越大。端接阻值選擇多大合適要通過仿真結合信號的噪聲裕量來確定。

如下圖所示為不同終端端接的仿真波形。(藍色為ODT120,黃色ODT60,綠色為ODT40,紅色為ODT20)。

如上所示,ODT20的情況由于端接20ohm比50ohm傳輸線阻抗要小得多,在終端發生負反射使信號的幅值減小,此時信號的噪聲余量比較小。如果有其它的噪聲例如串擾、電源噪聲等就可能會使信號質量帶來風險;ODT40和ODT60的情況端接阻抗與傳輸線阻抗最接近,阻抗不連續性不是很大,所不同的是ODT60情況發生正反射,ODT40發生負反射,因此ODT60要比ODT40情況信號幅值大一些噪聲余量也要大一些;ODT120的情況下端接和傳輸線阻抗不匹配程度很大,但是信號幅值較ODT60進一步提高。但由于阻抗不連續性過大使其眼皮比較厚相比ODT60的情況噪聲余量增加并不明顯。

對于DDR信號的ODT配置的選擇需要具體問題具體分析,當信號鏈路比較短的情況可以不用ODT功能,因為此時傳輸線效應并不明顯阻抗不連續的影響不大;當信號線比較長時,能夠體現傳輸線特性,如果源端匹配和鏈路其它匹配做的都很好的情況下,此時只有終端會發生一次反射也可以不用ODT功能。

當源端匹配做的不好或者鏈路上存在很多阻抗不連續點的情況下就需要啟用ODT功能了,具體配置需要根據仿真結果來確定。另一方面并不是說開啟ODT功能就一定能夠得到比關閉ODT功能時更大的噪聲余量和時序裕量,而且也不是所有的信號質量問題都能通過開啟ODT來解決。

對于速率不算太高的DDR3來說,有時我們會發現好像ODT OFF時的結果都比ODT ON時要好。這是為什么呢?

首先接收端接收到的波形為入射電壓和反射電壓的疊加,如下所示:

入射電壓一定的情況下,反射電壓的大小正負取決于終端的反射系數。

DDR3的ODT結構如下圖所示。這里的R1\\R2就相當于DDR3的ODT值。

DDR3的ODT 值有20、40、60、120ohm以及ODT off等值,不同的ODT配置造成的影響就是終端反射系數不同。、

ODT20,ρ= Vref / Vinc= (20-50)/(20 +50) = -0.428,負反射使接收信號幅值減小;

ODT40,ρ= Vref / Vinc= (40-50)/(40 +50) = -0.111,負反射使接收信號幅值減小;

ODT60,ρ= Vref / Vinc= (60-50)/(60 +50) = 0.091,正反射使接收信號幅值增大;

ODT120,ρ= Vref / Vinc= (120-50)/(120 +50) = 0.411,正反射使接收信號幅值增大;

ODT OFF,ρ= Vref / Vinc = (∞ - 50)/(∞ + 50) = 1,全反射使接收信號幅值加倍。

由此可見當鏈路比較短或者其它地方不存在反射的情況下,信號的幅值完全取決于末端的反射系數,即ODT的配置。當ODT OFF情況下信號的幅值最大上升下降邊沿最陡因此其眼寬最寬。但是鏈路中的阻抗不匹配也會增加信號的過沖和振鈴,當線路很長或者阻抗不連續點很多時就有可能ODT OFF的情況要比ODT ON要差。

-

接收器

+關注

關注

14文章

2472瀏覽量

71911 -

比較器

+關注

關注

14文章

1651瀏覽量

107218 -

DDR

+關注

關注

11文章

712瀏覽量

65342 -

信號完整性

+關注

關注

68文章

1408瀏覽量

95488 -

CML

+關注

關注

0文章

32瀏覽量

19316

發布評論請先 登錄

相關推薦

示波器信號完整性的意義

什么是信號完整性

聽懂什么是信號完整性

終端端接在信號完整性中的意義

終端端接在信號完整性中的意義

評論