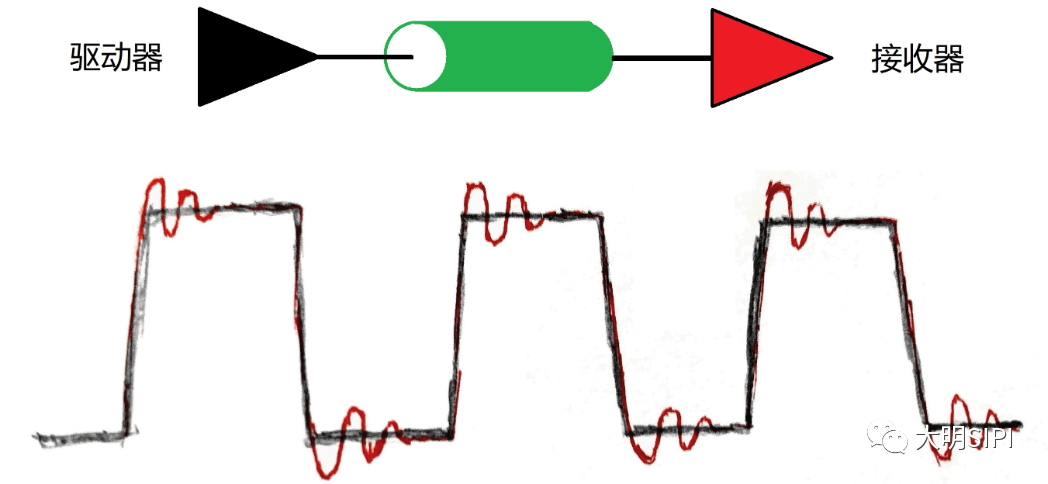

信號在驅動器和接收器之間傳輸時,由于源端和末端反射的存在就會導致多次反射,反射的結果就是導致接收端的波形產生信號的畸變。當驅動器的驅動能力強時可能導致過沖和振鈴;當驅動器的驅動能力比較弱時,可能會導致信號邊沿退化嚴重甚至邊沿不單調。

當過沖超過接收器的規范要求就會對器件壽命產生影響;過沖過大也會導致信號鏈路上產生遠高于信號頻率本身的高頻分量,從而導致更加嚴重的EMI問題,這也可能導致系統設計失敗;當振鈴過于嚴重就會影響信號的有效位寬和噪聲裕量,有效位寬減小會導致信號建立、保持時間余量不足,噪聲余量減小會導致信號抗干擾能力的降低,串擾和電源噪聲都可能導致信號的誤判;時鐘信號如果存在邊沿不單調則也可能導致接收器接收數據錯誤。因此可以說控制傳輸路徑上的反射是信號完整性分析的首要任務。而控制反射最常用的手段就是源端匹配和終端端接。

01

源端匹配

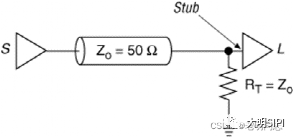

實際設計中最常用的源端匹配方式就是在驅動器輸出端加串聯電阻。電阻的阻值需要根據驅動器的輸出阻抗來決定,匹配電阻加上驅動器輸出阻抗等于傳輸線阻抗時能夠完全消除源端的反射。

如上所示,在驅動器輸出就近加33ohm匹配電阻Rmatch,使Rmatch+Rs=50ohm。信號進入傳輸線時在Vdrv點50ohm電阻和50ohm的傳輸線分壓,得到的信號幅值只有1.65V。1.65V的入射電壓沿傳輸線傳播到接收端發生全反射,產生1.65V的反射信號。這就導致在接收端接收到的幅值為3.3V,同時反射信號向源端傳輸,由于源端的阻抗已經匹配,當反射信號到達源端之后就不會再發生反射。

由此可見,源端匹配的作用就是讓驅動器輸出端的阻抗(包含驅動器內阻和匹配電阻)與傳輸線阻抗匹配,抑制了終端不匹配導致的反射信號在源端發生二次反射,進而抑制了多次反射的發生。抑制了多次反射,也就抑制了信號的過沖和振鈴,無論對器件的壽命還是接收端信號的有效判決都有重要的意義。

采用源端匹配方式時,需要注意匹配電阻阻值的選擇和匹配電阻布局這兩個方面。源端匹配電阻選擇以匹配傳輸線阻抗為目的,但也并不是選擇了合適的阻值就能夠起到預期的作用,如果匹配電阻的布局不合理它的效果就會大打折扣。

02

匹配電阻的布局

前面講傳輸線的效應時曾經提到,通常認為當信號傳輸延時小于信號上升時間1/6時,互連線處在集總區域,不會體現出傳輸線效應。這一點應用到匹配電阻的布局中就要求,源端匹配電阻布局要盡量靠近驅動器。因為只有讓匹配電阻和驅動器內阻之間的互連線(TLD2)延時小于信號上升時間的1/6才能夠使驅動器內阻和這段互連線加上匹配電阻看作是集總的,將這三部分集總在一起考慮。

下面我們可以仿真對比一下當信號上升時間為50ps時驅動器內阻到匹配電阻的互連線延時分別為8ps(小于50ps的1/6)、20ps、50ps(與信號上升時間相當)時的接收器件接收到的信號波形。

為了更好地觀測仿真結果,將三種情況信號的延時分別錯開了1ns。

需要注意的是,這里的仿真為了讓讀者更加清晰的看到驅動器內阻到匹配電阻的互連線延時的影響,將信號的上升時間設置為50ps是非常快,實際應用中除了高速串行鏈路和DDR等高速并行總線上升時間并不會達到這么快。

從上面的仿真結果可以看出:

1.驅動器內阻到匹配電阻的互連線長度對接收器接收波形有很大影響,會在接收波形穩定電平處產生周期性的過沖和震蕩,且過沖的間隔等于傳輸線延時的兩倍。這說明由于驅動器內阻到匹配電阻的互連線的存在使得源端并沒有完全匹配,在驅動器和接收器之間還是存在著反射信號;

2.驅動器內阻到匹配電阻的互連線延時小于信號上升時間延時1/6時產生的反射信號對信號質量影響很小;互連線延時超過信號上升時間延時1/6、甚至和信號上升時間相當時產生的反射信號非常大,會產生比較大的過沖,且過沖的幅度隨著延時的增大而增大,匹配電阻所起到的匹配效果也會更差。

由此可見,對于一個上升時間有1ns左右的LVTTL或者CMOS電平信號,只要驅動器內阻到匹配電阻之間的延時不超過150ps,匹配電阻就能起到良好的匹配效果。微帶線的延時大概140ps/inch,帶狀線170ps/inch,也就是說只要這段互連線布線長度不超過1inch即可;但是對于DDR等高速內存接口上升時間可能只有幾十ps,這對匹配電阻的布局和布線要求就相當嚴格了,因此這些高速接口常常使用的是芯片內部匹配端接。

03

驅動器的驅動能力

驅動器輸出阻抗從一定程度上反映了驅動器的驅動能力。根據輸出電阻的大小可以分為過驅動和欠驅動兩種情況。下圖所示為驅動器輸出一個上升時間500ps的3.3V階躍信號,輸出阻抗分別為20ohm、80ohm的時候,在接收端接收到的信號波形。

所謂過驅動就是驅動器輸出阻抗(驅動器內阻加上源端匹配電阻)小于傳輸線阻抗的情況,此時進入傳輸線的入射電壓大于1/2VCCIO,接收端反射回來的信號在源端發生負反射從而使接收端信號產生過沖和振鈴,經過多次反射后穩定于VCCIO電平。

欠驅動就是驅動器輸出阻抗大于傳輸線阻抗的情況,此時進入傳輸線的入射電壓小于1/2VCCIO,接收端接收到的電壓幅值小于VCCIO,接收端反射回來的信號在源端發生正反射從而使接收端信號產生階梯狀上升的趨勢,經過幾次反射之后才能到達穩定的VCC電平。總體上看,過驅動時信號邊沿很陡并且存在過沖,而欠驅動時信號邊沿很緩。

另外,除了使用驅動器輸出阻抗來表示驅動器輸出能力之外,還可以使用驅動電流來表示驅動能力的大小,比如說xilinx的FPGA中LVTTL、CMOS電平的驅動電流通常在4mA到24mA可調,驅動電流越大說明驅動能力越強。

04

—

信號上升時間

信號上升時間對信號質量有重要的影響。在過驅動情況下,如果上升時間很快,信號將很快達到過沖的峰值,如果信號的上升時間很長那么過沖達到峰值的時間也會變長甚至不能達到峰值;在欠驅動的情況下,信號的上升時間很短會在信號邊沿上形成明顯的臺階,隨著信號上升時間的增大臺階會越來越不明顯最后可能消失。無論是過沖還是臺階它們的寬度都和傳輸線延時有關,由此信號上升時間和傳輸線延時應該有一定的關系使相互作用對最終信號質量產生影響。

過驅動情況下,驅動器到接收器之間傳輸線延時為1ns,信號上升時間分別為1ns、2ns、3ns情況接收器接收波形如下圖所示:

當信號上升時間小于2倍的傳輸線延時,接收端過沖能夠達到峰值;當信號上升時間大于2倍的傳輸線延時時, 接收端過沖峰值減小,上升時間越大過沖越不明顯。

欠驅動情況下,驅動器到接收器之間傳輸線延時為1ns,信號上升時間分別為1ns、2ns、3ns情況接收器接收波形如下圖所示:

當信號上升時間小2倍的傳輸線延時時,接收端信號存在臺階,臺階的大小為2倍的傳輸線延時減去上升時間;當信號上升時間大于2倍的傳輸線延時時, 接收端臺階不再明顯,上升時間越大信號的邊沿越緩。這再一次證明了為什么說上升時間越快、傳輸線長度越長帶來的信號完整性問題越嚴重。

-

驅動器

+關注

關注

53文章

8263瀏覽量

146696 -

接收器

+關注

關注

14文章

2475瀏覽量

72046 -

DDR

+關注

關注

11文章

712瀏覽量

65425 -

信號完整性

+關注

關注

68文章

1412瀏覽量

95546 -

電源噪聲

+關注

關注

3文章

152瀏覽量

17497

發布評論請先 登錄

相關推薦

信號完整性實際設計中最常用的源端匹配方式

信號完整性實際設計中最常用的源端匹配方式

評論