數轉換器(ADC)正經歷從并行LVDS(低壓差分信號)和CMOS數字接口到串行接口(JESD204)的轉變。

JESD204標準

自從2006年發布以來,JESD204標準經過兩次更新,目前版本為B版。2006年4月, JESD204最初版本發布。該版本描述了轉換器和接收器(通常是FPGA或ASIC)之間數Gb的串行數據鏈路。在最初版本中,串行數據鏈路被定義為一個或多個轉換器和接收器之間的單串行通道。

所示鏈路是轉換器和接收器之間的串行數據鏈路。幀時鐘同時路由至轉換器和接收器,并為設備間的JESD204鏈路提供時鐘。

通道數據速率定義為312.5 Mbps與3.125 Gbps之間,源阻抗與負載阻抗定義為100 Ω ±20%。差分電平定義為標稱800 mV峰峰值、共模電平范圍從0.72 V至1.23 V。該鏈路利用8b/10b編碼,采用嵌入式時鐘,這樣便無需路由額外的時鐘線路,以及相關的高數據速率下傳輸的數據與額外的時鐘信號對齊的復雜性。

這種形式的串行數據傳輸能容忍走線之間較大的容差——就同步采樣并行LVDS和CMOS接口設計而言。此外,編碼是直流平衡的,確保采用時鐘和數據恢復(CDR)設計時極佳的轉換頻率。

JESD204A標準

2008年4月,該標準第一版發布,稱為JESD204A。此修訂版增加了支持多個轉換器下的多路對齊串行通道的能力。此版本保留了最初版所支持的通道數據速率——即從312.5 Mbps至3.125 Gbps,另外還保留了幀時鐘。

增加了對多路對齊串行通道的支持,可讓高采樣速率和高分辨率的轉換器達到3.125 Gbps的最高支持數據速率。

通過在標準中加入這些功能,便可支持采用更高采樣速率和/或分辨率的轉換器。例如,根據JESD204,采樣時鐘為250 MHz的14位模數轉換器,在單通道下通過單鏈路傳送可能需要5.0 Gbps的輸出數據速率。

然而,修訂后的JESD204A標準已支持多路對齊串行通道,轉換器采樣數據可映射到兩條對齊串行通道上。這樣便可將單條通道的數據速率降至2.5 Gbps,低于3.125 Gbps的最高支持數據速率。

對于模數轉換器,當接收到信號時,若要正確重建模擬域采樣信號,則關鍵是了解采樣信號和其數字表示之間的時序關系。雖然最初的JESD204標準和修訂后的JESD204A標準在性能上都比老的接口標準要高,它們依然缺少一個關鍵因素:鏈路上串行數據的確定延遲。

該時序關系受模數轉換器的延遲影響,定義為輸入信號采樣邊沿的時刻直至模數轉換器輸出數字表示這段時間內的時鐘周期數。JESD204及JESD204A標準中沒有定義可確定性設置模數轉換器延遲和串行數字輸出的功能。另外,轉換器的速度和分辨率也不斷提升。這些因素導致了該標準的第二個版本——JESD204B。

JESD204B標準

2011年7月,第二版本標準發布,稱為JESD204B,即當前版本。修訂后的標準中,其中一個重要方面就是加入了實現確定延遲的條款。另外,對數據速率的支持上升到了12.5 Gbps,并描述了設備的不同速度等級。

此修訂版標準使用設備時鐘作為主要時鐘源,而不是像之前版本那樣以幀時鐘作為主時鐘源。

在JESD204標準之前的兩個版本中,沒有確保通過接口的確定延遲相關的條款。JESD204B修訂版通過提供一種機制,確保兩個上電周期之間以及鏈路重新同步期間,延遲是可重現和確定性的。

該機制是這樣工作的:在定義明確的時刻使用SYNC~輸入信號,同時初始化所有通道中轉換器最初的通道對齊序列。此外,接收器必須將每條通道的數據進行緩沖,用來處理串行數據通道上的偏斜。可使用稱為Rx緩沖延遲(RBD)的可編程周期數,在明確定義的時刻將緩沖數據同時釋放。

除了確定延遲,JESD204B支持的通道數據速率上升到12.5 Gbps,并將設備劃分為三個不同的速度等級:

第一速度等級與JESD204和JESD204A標準定義的通道數據速率相同,即通道數據電氣接口最高為3.125 Gbps。如前所述,這些數據速率的差分電平為標稱800 mV峰峰值,共模電壓電平范圍為0.72 V至1.23 V(源阻抗和負載阻抗定義為100 Ω ±20%)。

JESD204B的第二速度等級定義了通道數據速率最高為6.375 Gbps的電氣接口。該速度等級與第一速度等級相似,差分電平為標稱800 mV峰峰值。共模電平范圍由于基于接收器給定的終端電壓而稍有不同,但總體與第一速度等級相似。源阻抗和負載阻抗相同,均定義為100 Ω ±20%。

JESD204B的第三速度等級定義了通道數據速率最高為12.5 Gbps的電氣接口。該速度等級電氣接口要求的差分電平降低至標稱400 mV峰峰值,與較低的兩個速度等級相比較而言,它將電平值有效地降低了兩倍。共模電平范圍與第二速度等級相似,由接收器指定的終端電壓決定。源阻抗和負載阻抗同樣定義為100 Ω ±20%。

為提供更多的靈活性,JESD204B版本采用設備時鐘而非幀時鐘。在之前的JESD204和JESD204A版本中,幀時鐘是JESD204系統的絕對時間參照。幀時鐘和轉換器采樣時鐘通常是相同的。

這樣就沒有足夠的靈活性,而且當要將此同樣的信號路由給多個設備并計數不同路由路徑之間的偏斜時,就會對系統設計產生不必要的復雜性。JESD204B中,采用設備時鐘作為JESD204系統每個元件的時間參照。每個轉換器和接收器分別接收由時鐘發生器電路產生的設備時鐘,該發生器電路負責從同一個源產生所有設備的時鐘。這讓系統設計更加靈活,但需為每個給定設備指定幀時鐘和設備時鐘之間的關系。

隨著轉換器速度和分辨率的提高,對于效率更高的數字接口的需求也隨之增長。JESD204串行數據接口標準的建立,是為了提供更優秀和快速的方法,以便將數據從轉換器傳輸到接收器設備。

接口經過兩個版本的改進和實施,以適應對更高速度和分辨率轉換器不斷增長的需求。每個修訂版都滿足了對于改進其實施的要求,并允許標準演進以適應轉換器技術的改變及由此帶來的新需求。隨著系統設計越來越復雜,以及對轉換器性能要求的提高,JESD204標準有望進一步調整和演進,滿足新設計的需要。

就像幾年前LVDS開始取代CMOS成為轉換器數字接口技術的首選,JESD204有望在未來數年內以類似的方式發展。雖然CMOS技術目前還在使用中,但已基本被LVDS所取代。轉換器的速度和分辨率以及對更低功耗的要求最終使得CMOS和LVDS將不再適合轉換器。隨著CMOS輸出的數據速率提高,瞬態電流也會增大,導致更高的功耗。雖然LVDS的電流和功耗依然相對較為平坦,但接口可支持的最高速度受到了限制。這是由于驅動器架構以及眾多數據線路都必須全部與某個數據時鐘同步所導致的。

由于JESD204標準已為轉換器供應商和用戶所采納,它被細分并增加了新特性,提高了效率和實施的便利性。此標準即適用于模數轉換器(ADC)也適用于數模轉換器(DAC)。

由于該標準已為越來越多的轉換器供應商、用戶以及FPGA制造商所采納,它被細分并增加了新特性,提高了效率和實施的便利性。此標準既適用于模數轉換器(ADC)也適用于數模轉換器(DAC),更重要的是作為FPGA的通用接口(也可能用于ASIC)。

JESD204接口標準經過兩個版本的改進和實施,以適應對更高速度和分辨率轉換器不斷增長的需求。每個修訂版都滿足了對于改進其實施的要求,并允許標準演進以適應轉換器技術的改變及由此帶來的新需求。隨著系統設計越來越復雜,以及對轉換器性能要求的提高,JESD204標準有望進一步調整和演進,滿足新設計的需要。

為什么需要高速轉換器轉FPGA串行接口

JESD204數據轉換器串行接口標準由JEDEC委員會制定,旨在標準化并減少高速數據轉換器與FPGA(現場可編程門陣列)等其它器件之間的數據輸入/輸出數目。更少的互連可簡化布局布線,并支持實現更小尺寸的解決方案,同時不影響整體系統性能。這些特性對于克服許多高速ADC應用的系統尺寸和成本限制非常重要,包括無線基礎設施(GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA)、收發器架構、軟件定義無線電、便攜式儀器儀表、醫療超聲設備、雷達和安全通信等軍用/航空應用。

據介紹,并行接口的物理布局限制和串行 LVDS(低壓差分信號)方法的比特率限制目前給設計人員帶來了技術障礙。而高速轉換器轉FPGA串行接口,一是可簡化整體系統設計,具有更小/更少的布線數量,電路板走線設計更輕松。針對更小型的系統,客戶需要更簡單的布局設計。二是可減少引腳數,從高引腳數低速度并行接口升級到低引腳數高速度串行接口,可使發射端和接收端同時減少,也使集成嵌入式時鐘進一步減少引腳數。三是降低系統成本,具有更小的IC封裝和電路板設計可降低成本。四是能輕松擴展滿足未來帶寬需要,更小的幾何尺寸、更快地速度,能更好地適應各種標準。

ADI公司是JEDEC JESD204標準委員會的創始成員,可開發出了兼容的數據轉換器技術和工具,并推出了全面的產品路線圖,從而全力幫助客戶充分利用這一重大接口技術突破。

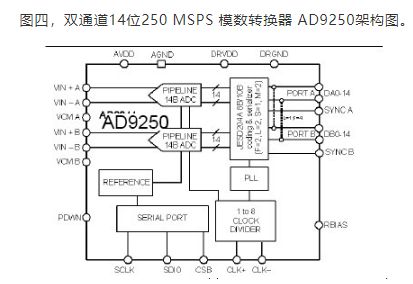

雙通道14位/250 MSPS ADC( AD9250)

為了解決這一需求, ADI最近推出采用 JEDEC JESD204B 串行輸出數據接口標準的雙通道14位250 MSPS 模數轉換器 AD9250。張靖強調,AD9250 ADC 是市場上首款完全達到 JESD204B Subclass 1確定性延遲要求的250 MSPS ADC,此功能通過一個串行接口支持多個數據轉換通道精密同步。

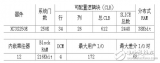

AD9250 ADC的串行接口方案通過單通道或雙通道鏈路提供高達5 Gbps 的采樣率。使用兩個串行通道可支持250 MSPS全速雙通道模數轉換數據速率,單個通道則用于支持較低的采樣率。目前已有FPGA 供應商。針對模擬信號鏈的這種端到端無縫連接方案可簡化 PCB 布局,加快原型開發,使產品更快上市。

AD9250 轉換器的 JESD204B 串行接口將每個 IC 所需高速差分輸出數據路徑的數目從多達28個減至2個。每個上電周期以及經過鏈路重新同步事件后,其 Subclass 1確定性延遲功能都是可重復的。此功能在以下應用中很重要:分集無線電系統和儀器儀表、TD-SCDMA/WCDMA/LTE(尤其是2R2T >8R8T演進)等多模式數字接收機應用、雷達/防務電子、醫療成像系統、電纜基礎設施以及通用軟件無線電。

雙通道14位250 MSPS ADC AD9250主要特性和性能還體現在,具有 Subclass 1確定性延遲的 JESD204B 編碼串行數字輸出 信噪比 (SNR):70.6 dBFS(185 MHz輸入,250 MSPS) 無雜散動態范圍 (SFDR):88 dBc(185 MHz輸入,250 MSPS) 中頻采樣頻率最高達400 MHz 95 dB通道隔離/串擾 低功耗和小封裝尺寸。

ADI推出的評估套件,AD9250-250EBZ (250 MSPS)、AD9250-170EBZ (170 MSPS)和AD6673-250EBZ DUT板,與輔助高速數據采集卡 HSC-ADC-EVALDZ,構成 AD9250的完整評估系統,它針對信號性能進行了優化。采集到的數據可以利用筆記本電腦和 ADI 免費軟件 VisualAnalog進行分析。為了與 FPGA 開發平臺兼容,DUT 板可以使用 CVT-ADC-FMC-INTPZB FMC 內插器連接器。

ADI 的這款產品為 FPGA 系統中的模擬信號鏈設計提供了一種新的高度集成方法。雙通道14位 ADC AD9250具備的寬帶信號處理性能,其簡化的接口為軟件定義無線電和醫療超聲領域的下一代 FPGA 應用掃清了設計障礙。對于許多系統設計師來說,實現高性能模擬信號鏈所面對的 I/O 挑戰現在有了一個精巧的解決方案。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605019 -

adc

+關注

關注

99文章

6530瀏覽量

545379 -

無線電

+關注

關注

60文章

2145瀏覽量

116695

發布評論請先 登錄

相關推薦

UM232H-B是FT232H高速到串行/并行接口轉換器的開發模塊

高速轉換器應用指南及需要注意的事項

寬帶數據轉換器應用的JESD204B與串行LVDS接口考量

高速DSP與串行A/D轉換器TLC2558接口的設計

關于JESD204B轉換器與FPGA匹配的設計關鍵點

基于FPGA連接的JESD204B高速串行鏈路設計需要考慮的基本硬件及時序問題詳解

基于FPGA的串行A/D轉換模塊設計

為什么需要高速轉換器轉FPGA串行接口

為什么需要高速轉換器轉FPGA串行接口

評論