Noam Levine 和 David Skolnick

到目前為止,我們已經描述了DSP處理器的物理架構,解釋了DSP如何提供與傳統模擬電路相比的一些優勢,并研究了數字濾波,展示了DSP的可編程特性如何適用于此類算法。現在,我們來看看在硬件平臺ADSP-2 EZ-Kit Lite&tm;上實現有限脈沖響應(FIR)濾波器算法的過程(在第2100部分中簡要介紹,在ADSP-2181系列匯編代碼中實現)。該實現已擴展為處理數據 I/O 問題。

使用數字濾波器

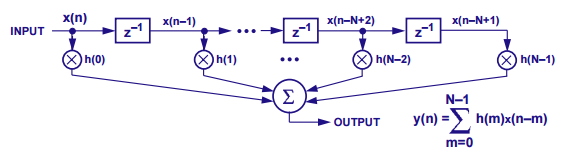

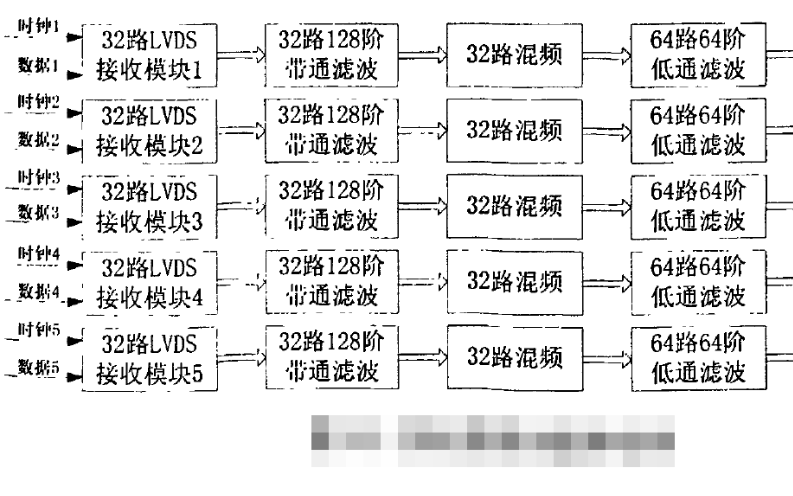

DSP的許多架構特性,例如執行零開銷環路的能力,以及在單個處理器周期中獲取兩個數據值的能力,對于實現此濾波器非常有用。簡要回顧一下,FIR濾波器是一種全零濾波器,它是通過將具有濾波器系數的輸入數據點序列進行卷積來計算的。其控制方程和直接形式表示如圖1所示。

圖1.直接形式的FIR濾波器結構。

在此結構中,每個“z–1“框表示輸入數據歷史記錄的單個增量,采用 z 變換表示法。將每個連續延遲的樣本乘以適當的系數值 h(m),并將結果加在一起,生成一個值,表示對應于第 n 個輸入樣本的輸出。延遲元件或濾波器抽頭的數量及其系數值決定了濾波器的性能。

濾波器結構通過使用DSP進行計算來建議實現此算法所需的物理元素。對于計算本身,每個輸出樣本都需要多次等于濾波器長度的乘法累加運算。

輸入數據的延遲塊和系數值列表需要 DSP 中保留的內存區域來存儲數據值和系數。DSP的增強型哈佛架構允許程序員將數據存儲在程序存儲器和數據存儲器中,從而在每個周期內從DSP的內部SRAM執行兩次同時存儲器訪問。通過數據存儲器保存傳入的樣本,程序存儲器存儲系數值,可以在一個周期內獲取數據值和系數值以進行計算。

此 DSP 架構支持使用循環緩沖的程序(在第 2 部分和本期后面的部分中簡要討論)。這意味著地址指針只需要在程序開始時初始化,循環緩沖機制確保指針不會離開其分配的內存緩沖區的邊界 - 這是FIR濾波器代碼中廣泛用于輸入延遲線和系數的功能。一旦確定了程序的元素,下一步就是開發DSP源代碼來實現算法。

開發 DSP 軟件

ADSP-2100系列的軟件開發流程包括以下步驟:架構描述、源代碼生成、軟件驗證(調試)和硬件實現。圖 2 顯示了一個典型的開發周期。

圖2.軟件開發流程。

架構說明:首先,用戶創建運行算法的硬件系統的軟件描述。系統描述文件包括系統中的所有可用內存和任何內存映射的外設。以下是使用ADSP-2181 EZ-Kit Lite的此過程示例。

源代碼生成:從理論到實踐,這一步——將算法思想轉化為在DSP上運行的代碼——通常是過程中最耗時的步驟。有幾種方法可以生成源代碼。一些程序員更喜歡用高級語言(如 C)編寫算法;其他人更喜歡使用處理器的本機匯編語言。對于程序員來說,C 語言的實現可能更快,但編譯的 DSP 代碼由于沒有充分利用處理器的架構而缺乏效率。

匯編代碼通過充分利用處理器的設計,可以產生高效的實現。但是程序員需要熟悉處理器的本機匯編語言。最有效的方法是將C語言與系統的時間關鍵型數學密集型部分的匯編代碼相結合。在任何情況下,程序員都必須了解處理器的系統約束和外設細節。本文中的FIR濾波器系統示例使用ADSP-2100系列的本機匯編語言。

軟件驗證(“調試”): 此階段使用稱為模擬器的軟件工具測試代碼生成的結果,以檢查程序的邏輯流并驗證算法是否按預期執行。模擬器是DSP處理器的模型,它a)提供對所有存儲器位置和處理器寄存器的可見性,b)允許用戶連續運行DSP代碼或一次運行一條指令,c)可以模擬向處理器饋送數據的外部設備。

硬件實現:在這里,代碼在真正的DSP上運行,通常分幾個階段:a)在EZ-Kit Lite等評估平臺上試用;b) 在線仿真,以及 c) 生產 ROM 生成。試用提供程序操作的快速通過/不通過確定;此技術是本文中使用的實現方法。在線仿真監控系統中的軟件調試,其中EZ-ICE等工具可以?控制目標平臺上的處理器操作。所有調試完成后,可以生成最終代碼的引導ROM;它用作最終的生產實現。

使用ADSP-2181 EZ-Kit Lite

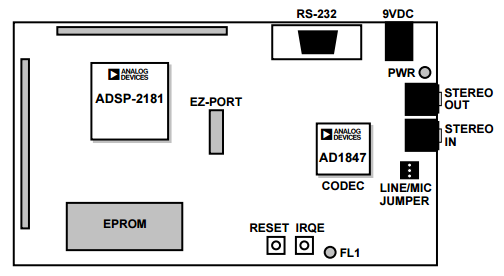

我們的開發周期示例介紹了整個過程,使用ADSP-2181 EZ-Kit Lite(開發包ADDS-21xx- EZLITE)作為濾波器算法的目標硬件。EZ-Kit Lite是一款低成本演示和開發平臺,由一個33 MHz ADSP-2181處理器、一個AD1847立體聲音頻編解碼器和一個插座式EPROM組成,后者包含用于通過RS-232連接將新算法下載到DSP的監控代碼(圖3)。

圖3.EZ-Kit Lite 板的布局。

要完成架構描述階段,需要知道DSP可用的存儲器和存儲器映射外設。程序員將此信息存儲在系統描述文件中,以便開發工具軟件可以為目標系統生成適當的代碼。EZ-Kit Lite不需要DSP外部的存儲器,因為片上可用存儲器由ADSP-16的程序存儲器(PM)SRAM的384,2181個位置和數據存儲器(DM)SRAM的16,352個位置組成。(用于系統控制寄存器的 32 個 DM 位置不可用于工作代碼)。有關ADSP-2181、EZ-Kit Lite架構和相關主題的更多信息,請參見本文末尾提到的文本。

可用的系統資源信息記錄在系統描述文件中,供ADSP-2100系列開發工具使用。系統描述文件具有.SYS擴展名。以下列表顯示了系統描述文件 [EZKIT_LT.SYS]:

.系統EZ_LITE; /* 為這個系統命名 */

.adsp2181; /* 指定處理器 */

.mmap0; /* 指定系統引導,并且 */,

/* PM 位置 0 在內部存儲器中 */

.seg/PM/RAM/ABS=0/code/data int_pm[16384];

.seg/DM/RAM/ABS=0 int_dm[16352];

.endsys; /* 結束描述 */

該列表將 PM 的 16,384 個位置聲明為 RAM,從地址 0 開始,以便將代碼段和數據值都放置在那里。還聲明了 16,352 個可用位置的數據存儲器作為 RAM,從地址 0 開始。由于這些處理器使用具有兩個不同內存空間的哈佛體系結構,因此 PM 地址 0 不同于 DM 地址 0。ADSP-2181 EZ-Kit Lite的編解碼器使用串行端口連接到DSP,該串行端口未在系統描述文件中聲明。要使系統描述文件可用于其他軟件工具,系統組裝器實用程序 BLD21 會將.SYS文件轉換為體系結構或 。呵呵,文件。系統構建器的輸出是一個名為 EZKIT_LT 的文件。哎呀。

編寫完代碼后,下一步是生成可執行文件,即將代碼轉換為DSP可以執行的指令。第一個組裝DSP代碼。這會將程序文件轉換為其他開發工具可以處理的格式。匯編還會檢查代碼是否存在語法錯誤。接下來,使用體系結構文件中聲明的可用內存鏈接代碼以生成 DSP 可執行文件。鏈接器將源代碼中的所有代碼和數據放入內存空間;輸出是一個DSP可執行文件,可以下載到EZ-Kit Lite板。

生成過濾器代碼

本系列的第 2 部分 [模擬對話 31-2,第 14 頁,圖 6] 介紹了 FIR 濾波器的小型匯編代碼列表。在這里,該代碼被增強以包含一些特定于 EZ-Kit Lite 的功能,特別是編解碼器初始化和數據 I/O。核心濾波器算法元素(乘法累加、使用循環緩沖區對數據和系數進行數據尋址,以及對零開銷循環效率的依賴)不會改變。

輸入數據將使用板載AD1847編解碼器進行采樣,該編解碼器具有可編程采樣速率、輸入增益、輸出衰減、輸入選擇和輸入混頻功能。其可編程特性使系統具有靈活性,但它也增加了編程任務,以便為DSP系統初始化它。

訪問數據

在本例中,編解碼器的一系列控制字(將在列表第一部分中的程序開頭定義)將初始化編解碼器,使其具有8 kHz采樣率,每個輸入通道上的增益值適中。由于AD1847是可編程的,用戶通常會重復使用接口和初始化代碼段,僅更改不同應用的特定寄存器值。此示例會將特定的篩選器段添加到 EZ-Kit Lite 軟件中找到的現有代碼段。

此接口代碼聲明內存中用于數據 I/O 的兩個區域:“tx_buf”(用于從編解碼器傳輸出的數據)和“rx_buf”(用于接收傳入數據)。這些內存區域或緩沖區中的每一個都包含三個元素:控制或狀態字、左通道數據和右通道數據。對于每個采樣周期,DSP 將從編解碼器接收狀態字、左通道數據和右通道數據。在每個采樣周期,DSP必須向編解碼器提供發射控制字、左聲道數據和右聲道數據。在此應用程序中,發送到編解碼器的控制信息不會更改,因此傳輸數據緩沖區中的第一個單詞將保持原樣。我們假設源是使用右聲道的單聲道麥克風(無需擔心左聲道輸入數據)。

使用EZ-Kit Lite軟件中的I / O shell程序,我們只需要參與標有“input_samples”的代碼部分。當從準備處理的編解碼器接收到新數據時,將訪問此部分代碼。如果只需要正確的通道數據,我們需要讀取位于數據存儲器中位置rx_buf + 2的數據,并將其放入數據寄存器中以饋入濾波器程序。

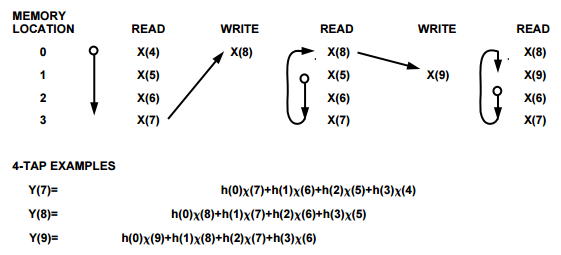

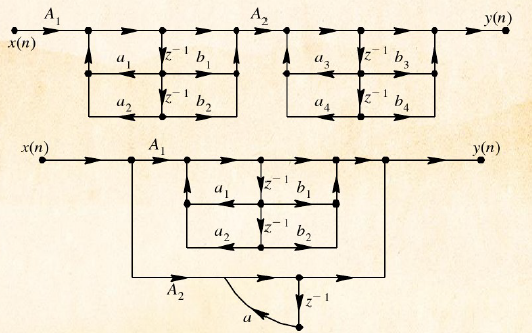

來自編解碼器的數據需要使用ADSP-2181的循環緩沖功能通過輸入延遲線饋入濾波器算法。輸入延遲塊的長度由濾波器使用的系數數決定。由于數據緩沖區是循環的,因此緩沖區中最早的數據值將位于上次訪問篩選器后指針指向的任何位置(圖 4)。同樣,每次通過濾波器始終以相同的順序訪問的系數也放置在程序存儲器的循環緩沖區中。

圖4.對篩選數據使用循環緩沖區的示例 輸入。

算法代碼

要對接收到的數據進行操作,只需進行少量修改即可使用上一期中發布的代碼部分。為了實現這個過濾器,我們需要使用乘法/累加(MAC)計算單元和數據地址生成器。

ADSP-2181的MAC將結果存儲在40位寄存器中(32個2位字的乘積為16位,8位允許總和擴展而不會溢出)。這允許中間篩選器值根據需要增長和收縮,而不會損壞數據。使用的代碼段是通用的(即,可用于任何長度的過濾器);因此,MAC的額外輸出位允許運行具有未知數據的任意過濾器,而不必擔心丟失數據。

為了實現FIR濾波器,對濾波器在每個數據點上的所有抽頭重復乘法/累加操作。為此(并為下一個數據點做好準備),MAC 指令以循環的形式編寫。ADSP-21xx的零開銷環路功能允許在指定數量的計數內重復MAC指令,而無需編程干預。計數器設置為抽頭數減一,循環機制自動減少每個循環操作的計數器。將循環計數器設置為“taps–1”可確保數據指針在執行完成后最終位于正確的位置,并允許最終 MAC 操作包括舍入。由于AD1847為16位編解碼器,因此具有舍入功能的MAC可提供四舍五入到最接近的16位值的統計無偏結果。此最終結果將寫入編解碼器。

為了獲得最佳代碼執行,每個指令周期都應執行有意義的數學計算。ADSP-21xxs通過多功能指令實現這一點:處理器可以在同一指令周期內執行多種功能。對于FIR濾波器代碼,每個乘法累加(MAC)操作可以與兩個數據訪問并行執行,一個來自數據存儲器,一個來自程序存儲器。此功能意味著在每次循環迭代中都會執行 MAC 操作。同時,正在獲取下一個數據值和系數,并且計數器會自動遞減。所有這些都不會浪費時間維護循環。

當為每個輸入數據樣本執行濾波器代碼時,MAC環路的輸出將被寫入輸出數據緩沖區,tx_buf。雖然該程序僅處理單通道輸入數據,但結果將通過寫入內存緩沖區地址 tx_buf+1 和 tx_buf+2 寫出到兩個通道。

最終的源代碼列表顯示在第 15 頁。過濾器算法本身列在“中斷服務例程”下。其余代碼用于編解碼器和 DSP 初始化以及中斷服務例程定義。這些主題將在本系列的后續部分中探討。

The EZ-Kit Lite

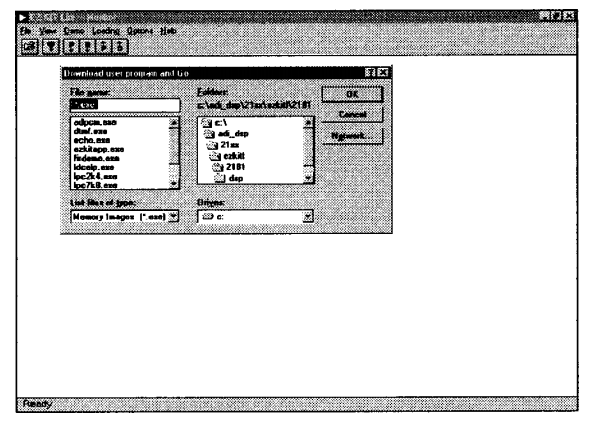

EZ-Kit Lite隨附的基于Windows的監控軟件可以將可執行文件加載到EZ-Kit Lite板上的ADSP-2181中。這是通過下拉的“加載”菜單選擇“下載用戶程序并轉到”來完成的(圖5)。這會將濾波器程序下載到ADSP-2181并開始程序執行。

圖5.EZ-Kit 精簡版下載菜單。

本文的目的是概述從算法描述到可在硬件開發平臺上運行的 DSP 可執行程序的步驟。引入的問題包括軟件開發流程、架構描述、源代碼生成、數據 I/O 和 EZ-Kit Lite 硬件平臺。

與每個主題相關的許多細節級別,這篇簡短的文章無法公正地對待。更多信息可在以下參考資料中找到。本系列將繼續在此應用程序的基礎上構建其他主題。下一篇文章將通過處理器中斷結構更詳細地研究數據輸入/輸出 (I/O) 問題,并討論簡單濾波器算法的其他功能。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19295瀏覽量

230001 -

dsp

+關注

關注

553文章

8006瀏覽量

349105 -

濾波器

+關注

關注

161文章

7832瀏覽量

178227

發布評論請先 登錄

相關推薦

[共享] 數字信號處理及其MATLAB實現

如何去使用數字信號處理算法

數字信號處理—理論、算法與實現

數字信號處理的FPGA實現

如何使用FPGA實現數字信號處理算法的研究

數字信號處理:在硬件平臺上實現算法

數字信號處理:在硬件平臺上實現算法

評論