這一期我們來討論一些名詞,就是標題里滿滿當當的英文單詞。當然,其中最核心也是最基本的,就是OCV。什么是OCV?它又有什么含義呢?或許后端的朋友們對它相對熟悉些。

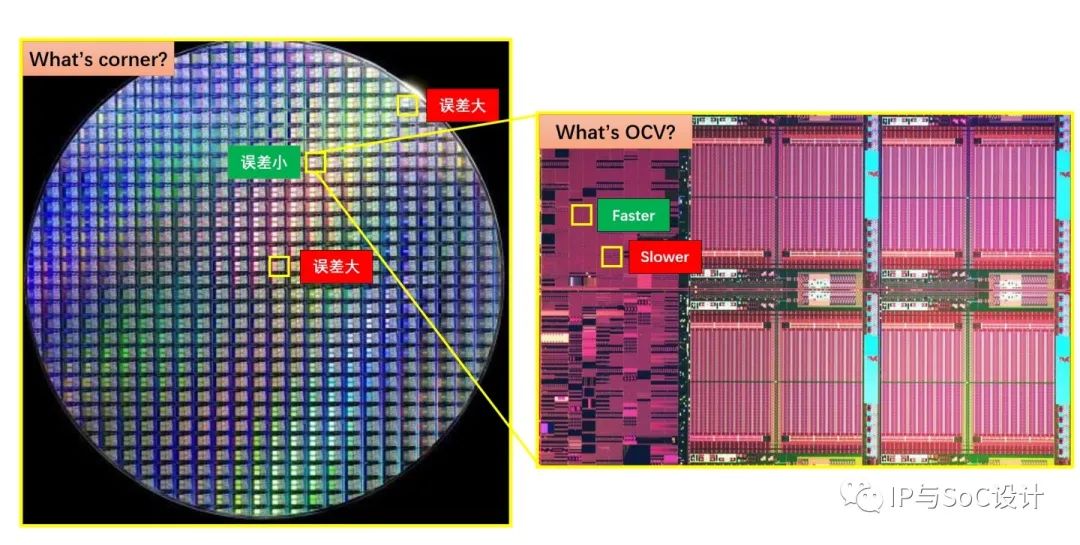

某種意義上來說,芯片很脆弱。在生產中,外界環境的各種變化,比如PVT,都可能會使芯片產生不同的誤差,從而導致同一晶圓上不同區域上的芯片里的晶體管速度變快或變慢,從而產生corner的概念。

由于這些偏差的存在,不同晶圓之間,同一晶圓的不同芯片之間,同一芯片的不同區域之間,情況都是不相同的。造成這些差異的因素有很多種,這些因素造成的不同主要體現:

1,IR Drop造成局部不同的供電的差異;

2,晶體管閾值電壓的差異;

3,晶體管溝道長度的差異;

4,局部熱點形成的溫度系數的差異;

而OCV就可以描述PVT在單個芯片所造成的影響,我們在時序分析時引入derate參數模擬OCV效應,其通過改變時延遲的早晚來影響設計。

在了解OCV和它的演進歷程之前,我們不妨多了解些概念,可以有助于我們更全面地去理解它。

工藝角(Process?Corner)

與雙極晶體管不同,在不同的晶片之間以及在不同的批次之間,MOSFETs 參數變化很大。為了在一定程度上減輕電路設計任務的困難,工藝工程師們要保證器件的性能在某個范圍內。如果超過這個范圍,就將這顆IC報廢了,通過這種方式來保證IC的良率。

傳統上,提供給設計師的性能范圍只適用于數字電路并以“工藝角”(Process Corners)的形式給出。其思想是:把NMOS和PMOS晶體管的速度波動范圍限制在由四個角所確定的矩形內。這四個角分別是:快NFET和快PFET,慢NFET和慢PFET,快NFET和慢PFET,慢NFET和快PFET。

例如,具有較薄的柵氧、較低閾值電壓的晶體管,就落在快角附近。從晶片中提取與每一個角相對應的器件模型時,片上NMOS和PMOS的測試結構顯示出不同的門延遲,而這些角的實際選取是為了得到可接受的成品率。因此,只有滿足這些性能的指標的晶片才認為是合格的。在各種工藝角和極限溫度條件下對電路進行仿真是決定成品率的基礎。

工藝角分析,corner analysis,一般有五種情況:

fast nmos and fast pmos(ff)

slow nmos and slow pmos(ss)

slow nmos and fast pmos(sf)

fast nmos and slow pmos(fs)

typical nmos and typical pmos(tt)

t,代表typical(平均值)

s,代表slow(電流小)

f,代表fast(電流大)

PVT(process,voltage,temperature)

設計除了要滿足上述5個corner外,還需要滿足電壓與溫度等條件,形成的組合稱為PVT(process,voltage,temperature) 條件。

設計時設計師還常考慮找到最好最壞情況,時序分析中將最好的條件(Best Case)定義為速度最快的情況, 而最壞的條件(Worst Case)則相反。

根據不同的仿真需要,會有不同的PVT組合。以下列舉幾種標準STA分析條件:

WCS(Worst Case Slow):slow process,high temperature,lowest voltage

TYP(typical):typical process,nominal temperature,nominal voltage

BCF(Best Case Fast):fast process,lowest temperature,high voltage

WCL (Worst Case @ Cold):slow process, lowest temperature, lowest voltage

在進行功耗分析時,可能是另外的一些組合,如:

ML(Maximal Leakage):fast process,high temperature,high voltage

TL(typical Leakage):typical process,high temperature,nominal voltage

三種STA(Static Timing Analysis)分析方法:

1,單一模式,用同一條件分析setup/hold;

2,BC_WC模式,用worst case計算setup,用best case計算hold;

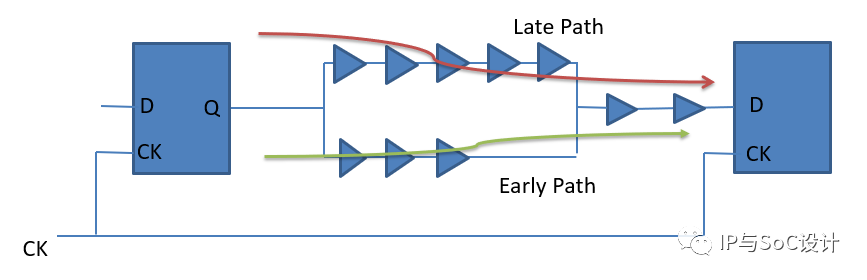

3,OCV模式,計算setup 用計算worst case數據路徑,用best case計算時鐘路徑;計算hold 用best case計算數據路徑,用worst case計算時鐘路徑。

Tip:

BC-WC:即為best case corner和worst case corner,分別代表兩種不同的PVT環境。BC時,timing-arc的時間最短,WC時,timing-arc的時間最長。

考慮到芯片運行環境的變化,以及在芯片制作中難以克服的工藝原因造成的Die to Die的參數不同,在原來Single Mode中通過分析的芯片,在真實芯片運行中,未必能完成所設定的功能。

考慮到single mode的粗糙性,在130nm以下的工藝中基本上已經不用了。因此設計人員引進了BC-WC(best corner-worst corner)分析模式。BC-WC模式下,工具會分析芯片所可能出現的最好和最壞的運行情況,保證這兩種極端情況下芯片功能的完整性。

而OCV模式,AOCV模式,POCV模式等均是在不同PVT(不同corner)的基礎上添加derate。

什么是OCV

OCV,也就是On chip variation。

與corner同理,同一塊芯片上的晶體管也會有變快或者變慢的現象,因此產生了OCV的概念。

在設計中引入OCV的目的在于從設計角度考慮芯片在實際生產中可能出現的各種差異(variation),從而適度增加設計余量(margin),減少不必要的設計悲觀量(pessimism)。

隨著芯片工藝的發展,對于STA的要求也越來越高,并且設計的復雜度不斷提升。傳統的WC-BC模式已無法準確的反應芯片的實際真實時序。OCV正是在這種情況下被提出并實際應用到STA中。

OCV在path上設置統一的derate,悲觀度較高。derate數值是指對launch、capture、data line的cell或者net上添加一個比理想情況更為悲觀的倍數,比如針對setup,launch的derate統一設置為1.1,表示delay時間增加值原來的1.1倍,capture的derate統一設置為0.9,表示delay時間變為原來的0.9倍。從而使設計能夠覆蓋實際生產過程中產生的variation。針對common path,利用cppr將悲觀量移除。

Tip:

CPPR (Clock Reconvergence Pessimism Removal),共同路徑悲觀去除

實現方式:

(1)運用于主PVT庫對應的微小差異PVT庫

(2)set_timing_derate命令設置全局derate值

Tip:

timing derate,我們可以稱為時序增減因子。在芯片的生產過程中,由于刻蝕、不同點的溫度、金屬不均勻、串擾、晶體管溝道長度等影響因素,導致片上各個位置單元延遲不一樣。因此,我們需要一個縮放因子來讓設計更加嚴格。

timing derate是計算OCV的一種簡單方法,在某單一條件(BC-WC)下,把指定path的delay放大或者縮小一些,這個比率就是derate。

OCV中電壓的考慮

電壓需要分為電壓全局偏差,電壓局部偏差來理解。

同樣以ffg 0.88v來check hold為例。我們可以將0.88v作為全局電壓。在這個電壓下,device的速度最快。但是,由于對于clock的lauch,capture都采用的最快的device,并不能覆蓋所有的最差情況。

因此,在ocv中增加一部margin來覆蓋這一部分情況也就可以理解了。

OCV中溫度的考慮

溫度同樣可以劃分為全局溫度偏差,局部溫度偏差。全局溫度偏差,將在PVT中得以體現。由于溫度反轉的影響,僅采用極限溫度-40c,125c有時候并不能覆蓋全局溫度偏差中的最差情況。有時需要增加額外的溫度的corner。

而由于芯片內部不同位置之間,由于device翻轉速率,電壓降等不同,導致局部相同的時序路徑中,溫度也有偏差。采用相同的溫度仍然不能覆蓋所有最差情況。

在進行signoff時,需要增加ocv余量,覆蓋溫度局部偏差。

OCV分析

-OCV建立時間分析,暫不考慮CPPR

-OCV保持時間分析,暫不考慮CPPR

-timing derate

-CPPR

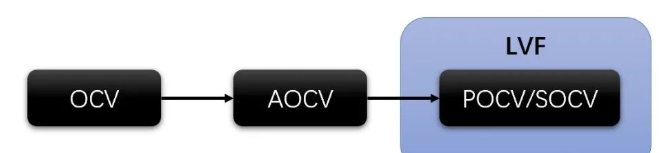

關于AOCV、POCV和LVF

什么是AOCV呢?

隨著半導體工藝的進步以及芯片設計的日趨復雜化,傳統OCV約束方式已經越來越不符合45nm及以下工藝的千萬門級高速芯片設計。相對于傳統OCV在path上設置統一derate值的方法,AOCV更為科學與合理的根據path的實際情況加上不同的derate值。通過科學合理的方法降低了derate值的悲觀度。

在傳統OCV上引入了對路徑長度和整個路徑在物理上所跨越的距離的考慮。在實際設計中,通過對一條line中cell在不同的邏輯深度時的仿真,以及基于前后級在物理中不同距離來得到一個更精確的derate值來進行時序分析,而不是OCV傳統的粗放式的統一的derate。

AOCV,即Advanced OCV。它在傳統OCV分析方法的基礎之上更進一步,在傳統OCV上引入了對路徑長度和整個路徑在物理上所跨越的距離的考慮。

隨著數據路徑的增長,OCV效應會減弱;隨著跨越距離的增加,OCV效應又會增強。AOCV就是要通過考慮這些OCV效應的變化從而避免過度悲觀的OCV分析。如何來有效 降低OCV的過度悲觀,是我們提高時序分析準確性的關鍵。

因此設計人員想到了通過仿真以及結合芯片的實際物理情況,對每個cell給出更貼近實際情況的derate值,將能有效的幫助我們得到更準確的時序分析。由此我們引入了AOCV分析模式,在AOCV中,我們將通過對cell在不同的邏輯深度時的仿真,以及基于前后級在物理中的不同距離來得到一個更精確的derate值來進行時序分析,而不是傳統的粗放式的統一的derate。

AOCV derate table:

(1)path depth:基于cell在整條時序路徑中所處的深度或者級數來考慮derate

(2)path distance:基于路徑中cell或net跨越的物理距離來給出相應的derate

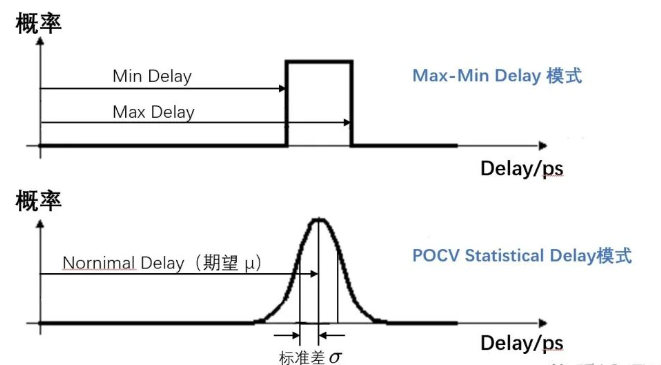

也正是因為OCV存在以下缺點:在實際中的variation,絕少是一個統一的數值,而大概率是服從正態分布的。所以AOCV才應運而生。

既然有了AOCV,為什么要有POCV?

1,當工藝進化到14nm后,AOCV分析模式中動態設置時序減免值的方法已經不能滿足精度要求,其分析結果的悲觀型也無法很好地改變。

2,AOCV需要先分析邏輯深度和物理距離兩個因素,再設置時序減免值,導致CPU工作量巨大,時序分析計算時間增加。

3,時序優化過程中增加或者刪除緩沖器會改變邏輯深度,然后又需要根據邏輯深度重新選擇時序減免值,重新時序計算,迭代次數和時間增加。

POCV (Parametric On Chip Variation)

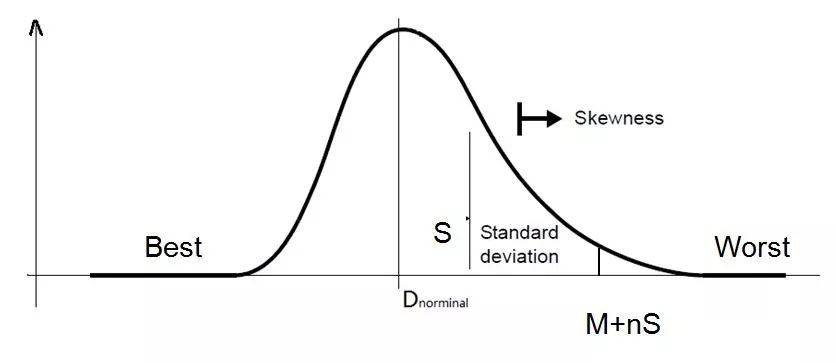

POCV,又稱SOCV(Statistical On Chip Variation),如下圖所示,POCV和AOCV一樣將delay模擬成一個正態分布。每個cell的delay最高概率出現在期望值u周圍,整體落在正負3倍標準差區間內的概率為99.7%。

以上介紹的時序分析方法就是POCV,也叫SOCV,全稱為Statistic OCV。這是一種比AOCV更加先進的分析模式,它放棄了用最worst和最best的情況去標記delay,取而代之的是M+nS和M-nS的值,因此timing的情況會比OCV以及AOCV更加樂觀。

至于LVF是什么呢

LVF,liberty variation format。是一種和liberty庫文件(.lib)有關的數據格式。

POCV的內容可以集成到類似于liberty文件中,有助于時序分析。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50936瀏覽量

424671 -

晶圓

+關注

關注

52文章

4927瀏覽量

128099 -

晶體管

+關注

關注

77文章

9705瀏覽量

138463 -

OCV

+關注

關注

0文章

25瀏覽量

12551 -

POCV

+關注

關注

1文章

6瀏覽量

12465

原文標題:科普:OCV、AOCV、POCV、LVF

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用Labview vision assistant怎么做OCV識別急求

為什么要有POCV?

基于開路電壓(OCV)的電量計設計

獲取鋰離子(Li+)電池參數,用于基于開路電壓(OCV)的電

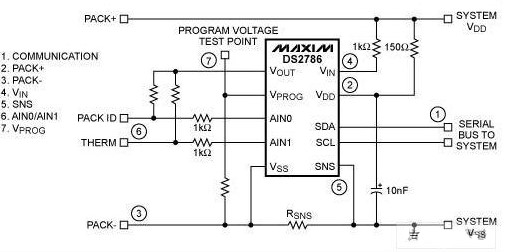

基于開路電壓(OCV)的電量計DS2786

AOCV時序分析法降低工作電壓

基于DS2786 OCV電路板的編程及測試步驟

OCV、AOCV、POCV、LVF都是些什么?

解釋DS2786的開路電壓(OCV)電量計

AOCV時序分析概念介紹

科普:OCV、AOCV、POCV、LVF

科普:OCV、AOCV、POCV、LVF

評論