前 言

本文主要介紹i.MX 8M Mini基于FlexSPI、PCIe與FPGA的高速通信案例。

本文檔適用開發環境:

Windows開發環境:Windows 7 64bit、Windows 10 64bit

虛擬機:VMware15.1.0

Linux開發環境:Ubuntu18.04.4 64bit

U-Boot:U-Boot-2020.04

Kernel:Linux-5.4.70

Linux SDK:5.4.70_2.3.0

*測試硬件平臺:TLIMX8-EVM評估板(NXP i.MX 8M Mini)

案例一:主要演示ARM Cortex-A53通過FlexSPI接口讀取FPGA(Spartan-6采集卡TL-HSAD-LX)發送的模擬數據,并進行校驗,通過串口打印相關信息。實測速率為114.89MB/s。

案例二:主要演示ARM Cortex-A53通過PCIe接口與FPGA進行通信,實現對CameraLink相機圖像的采集、編碼和顯示。實測傳輸幀率為60fps。

1 flexspi_read案例

1.1 案例說明

本案例主要演示ARM Cortex-A53通過FlexSPI接口讀取FPGA(Spartan-6采集卡TL-HSAD-LX)發送的模擬數據,并進行校驗,通過串口打印相關信息。

(1) 驅動默認配置FlexSPI為DDR模式(雙邊沿),配置FlexSPI的時鐘源為400MHz,分頻系數pre_divider和post_divider分別為2和5,此時FlexSPI的ROOT CLK時鐘為400MHz/2/5 = 40MHz,DDR模式的傳輸時鐘SCLK= ROOT SCLK/2 = 20MHz,數據位寬為8bit,即理論傳輸速率為40MB/s,實測速率為37.56MB/s。

(2) 驅動如配置FlexSPI為DDR模式(雙邊沿),配置FlexSPI的時鐘源為400MHz,分頻系數pre_divider和post_divider分別為1和3,此時FlexSPI的ROOT SCLK時鐘為400MHz/1/3 = 133MHz,DDR模式的傳輸時鐘SCLK = ROOT SCLK/2 = 66.5MHz,數據位寬為8bit,即理論傳輸速率為133MB/s,實測速率為114.89MB/s。

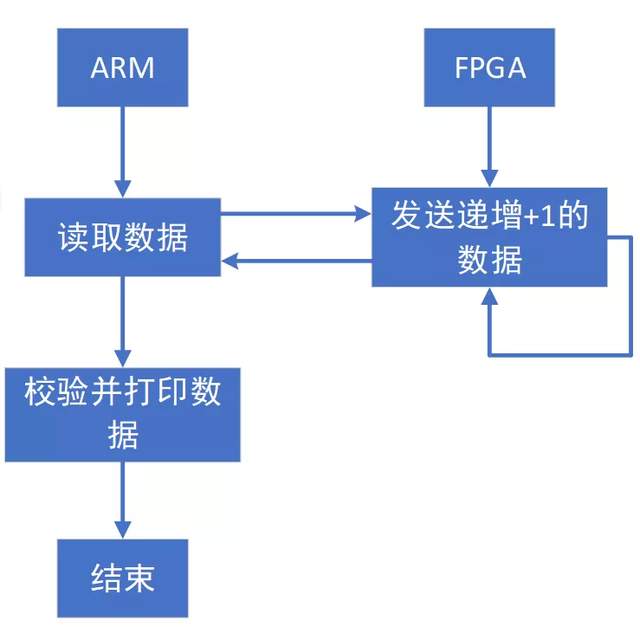

FPGA端:發送從0x00遞增至0xFF的數據。

ARM端:讀取數據并進行校驗,打印誤碼率、讀取速率和讀取到的數據。

程序流程圖如下:

圖 2

1.2 案例測試

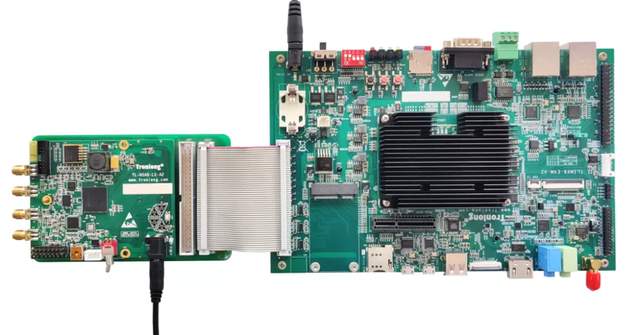

圖 3

請按照上圖進行硬件連接,并將案例bin目錄下的可執行文件flexspi_read、“driver\bin\”目錄下驅動文件flexspi_imx8.ko、“dts\image\”目錄下的設備樹文件tlimx8-evm-flexspi.dtb拷貝至評估板文件系統。采集卡TL-HSAD-LX加載或固化“data_to_flexspi\bin\”目錄下的.bit或.mcs文件。在評估板文件系統flexspi_read文件所在路徑下,執行如下命令查詢程序參數說明。

Target# ls

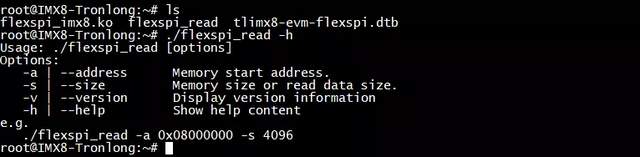

Target# ./flexspi_read -h

圖 4

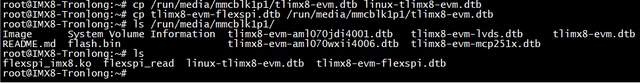

執行如下命令將默認使用的設備樹tlimx8-evm.dtb進行備份,然后把tlimx8-evm-flexspi.dtb拷貝至“/run/media/mmcblk1p1/”目錄并重命名為tlimx8-evm.dtb。

Target# cp

/run/media/mmcblk1p1/tlimx8-evm.dtb linux-tlimx8-evm.dtb//備份默認的tlimx8-evm.dtb,新文件名為linux-tlimx8-evm.dtb

Target# cp tlimx8-evm-flexspi.dtb /run/media/mmcblk1p1/tlimx8-evm.dtb

備注:更換設備樹后,需重啟評估板方可使設備樹生效。

圖 5

1.2.1 功能測試

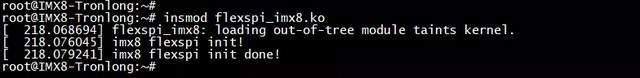

執行如下命令加載FlexSPI驅動。

Target# insmod flexspi_imx8.ko

圖 6

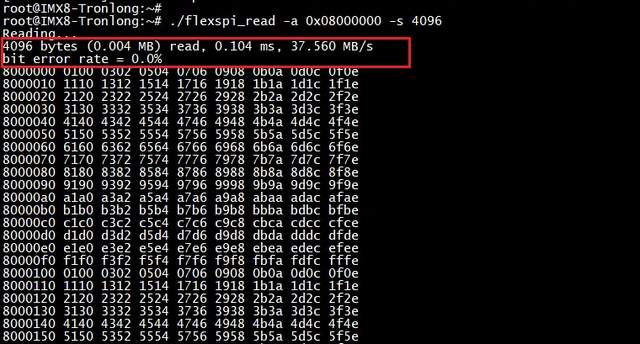

執行如下命令進行測試。

Target# ./flexspi_read -a 0x08000000 -s 4096

圖 7

本次測試速率為37.56MB/s,誤碼率為0,與理論速率40MB/s接近。

備注:受限于測試板卡的硬件連接形式的影響,37.56MB/s是零誤碼率時的最高實測速率。

若讀取小于或等于2048Byte的數據時,每次讀完需清空FlexSPI的RX Buffer,否則下次讀取的數據是緩存在Buffer中的舊數據。

Target# devmem2 0x30bb0000 w 0xFFFF7031

圖 8

1.2.2 性能測試

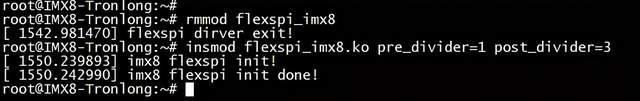

執行如下命令卸載flexspi驅動,并重新加載驅動。同時采集卡TL-HSAD-LX重新加載或固化FPGA程序。

Target# rmmod flexspi_imx8

Target# insmod flexspi_imx8.ko pre_divider=1 post_divider=3

備注:pre_divider和post_divider為分頻系數,詳細說明請查閱驅動說明章節。

圖 9

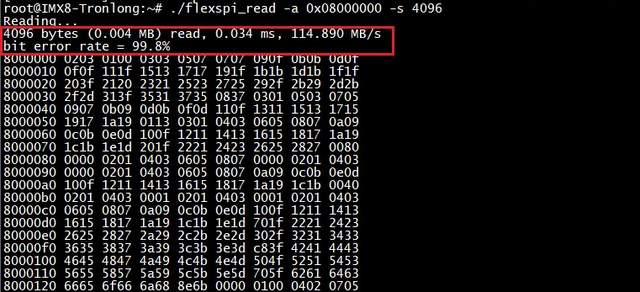

執行如下命令進行測試。

Target# ./flexspi_read -a 0x08000000 -s 4096

圖 10

可以看到本次測試速率為114.89MB/s,與理論速率133MB/s接近。

備注:受限于測試板卡的硬件連接形式的影響,此速率下的誤碼率為99.8%。

1.3 案例關鍵代碼

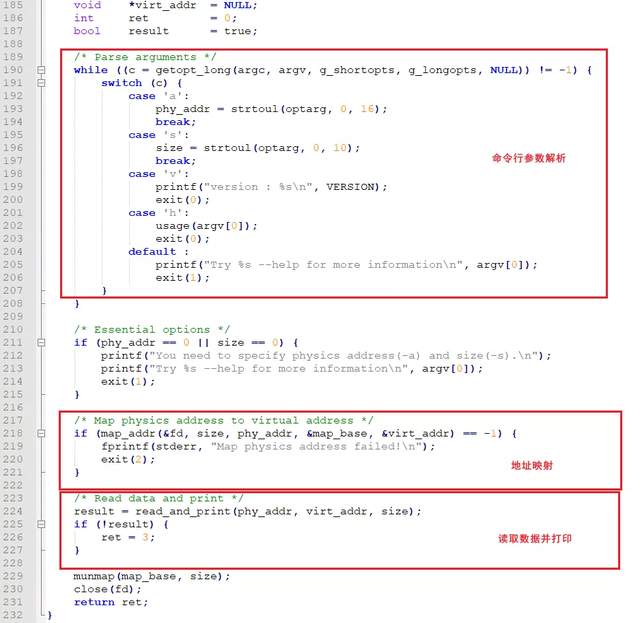

(1) main函數

圖 11

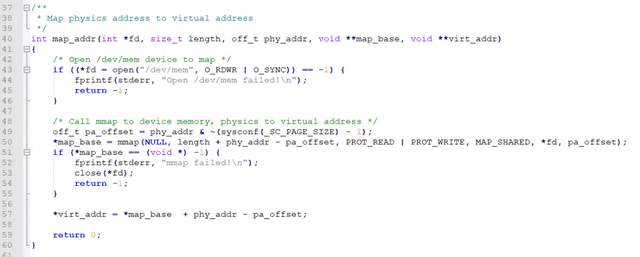

(2) 地址映射。

圖 12

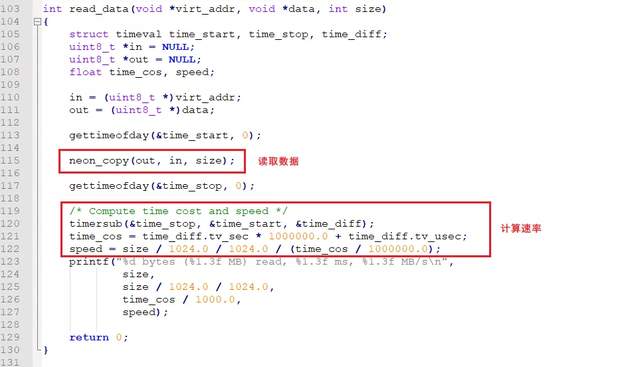

(3) 讀取數據。

圖 13

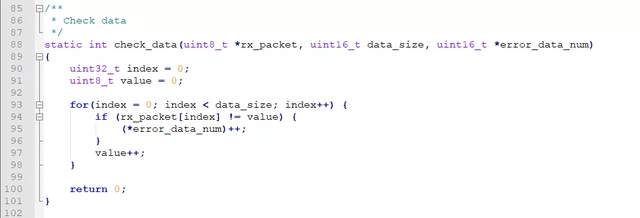

(4) 校驗數據。

圖 14

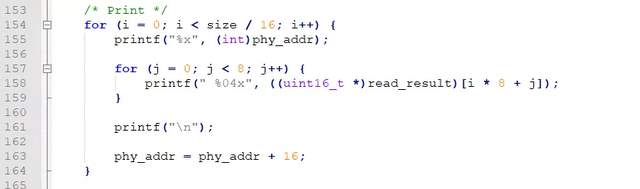

(5) 打印數據。

圖 15

1.4 FPGA工程關鍵代碼

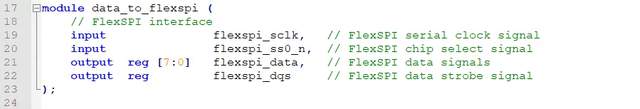

(1) 端口IO定義

flexspi_sclk和flexspi_ss0_n為輸入信號,flexspi_data和flexspi_data為輸出信號。

圖 16

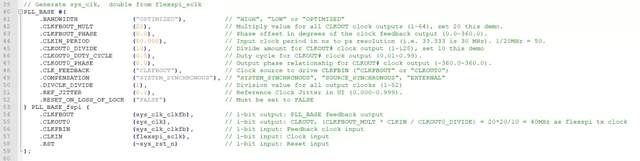

(2) 時鐘輸入信號flexspi_sclk設置為2倍頻

圖 17

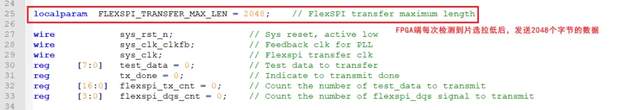

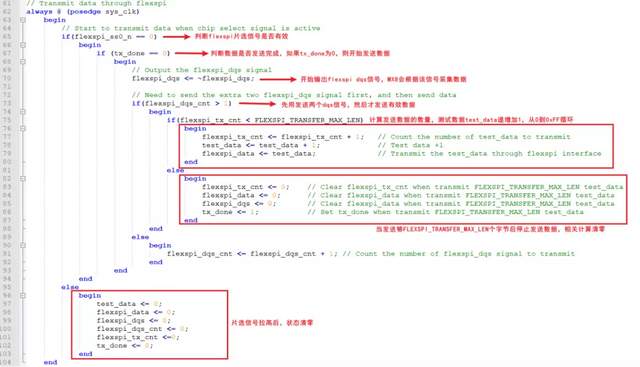

(3) 數據發送

圖 18

圖 19

2 gst_pcie_enc案例

2.1 案例說明

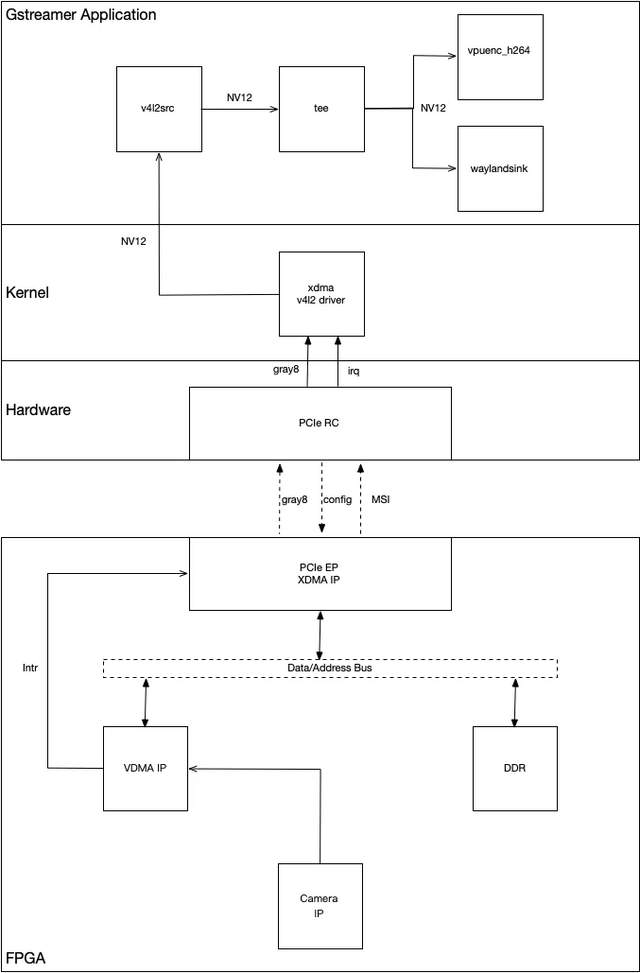

本案例主要演示ARM Cortex-A53通過PCIe接口與FPGA進行通信,實現對CameraLink相機圖像的采集、編碼和顯示。其中ARM端獲取到的原始圖像通過dma-buf機制,在采集、硬件編碼和顯示輸出等功能中進行共享,可實現高效的圖像數據“零拷貝”的錄播方案。

FPGA端:

(1) 采集CameraLink相機圖像;

(2) 通過XDMA IP實現為PCIe EP設備,RC端可通過PCIe接口訪問FPGA端DDR以及對VDMA IP的寄存器進行配置。

ARM端:

(1) 作為PCIe RC設備,配置VDMA IP將圖像存儲到FPGA DDR指定位置、將圖像從FPGA DDR通過XDMA搬運到ARM端DDR;

(2) 調用協處理器VPU進行H264硬件編碼,并將編碼后的數據存儲到文件;

(3) 編碼的同時,通過HDMI顯示實時圖像。

程序工作流程框圖如下所示:

圖 20

2.2 案例測試

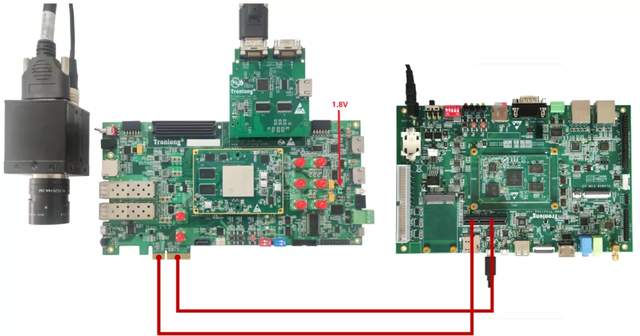

請參考下圖,將創龍科技的TLCamerLinkF模塊連接至TLK7-EVM評估板的FMC2接口,TLK7-EVM評估板J1跳線帽選擇1.8V檔位,以配置FMC IO的BANK電壓為1.8V。將CameraLink相機的CL0通過數據線連接至TLCameraLinkF模塊的CameraLink1接口。再將TLK7-EVM評估板的PCIe插到TLIMX8-EVM評估板的PCIe插槽上,使用HDMI線纜連接TLIMX8-EVM評估板的HDMI OUT接口至HDMI顯示屏。

圖 21

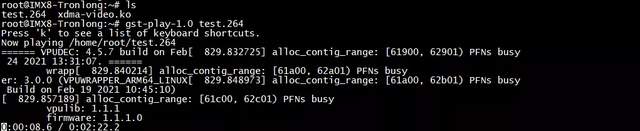

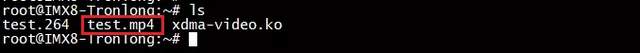

將該案例bin目錄下的驅動文件xdma-video.ko拷貝至TLIMX8-EVM評估板文件系統中,并將案例bin目錄下的.bit或.bin文件加載或固化到TLK7-EVM評估板。

評估板上電,可執行lspci命令檢查PCIe連接是否正常。如不能獲取到如下信息,請檢查硬件連接和FPGA端是否正常運行。

Target# lspci

圖 22

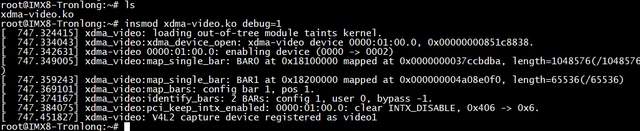

Target# insmod xdma-video.ko debug=1

備注:“debug=1”表示打印幀率信息,可根據實際需求選擇是否配置。若需修改分辨率和幀率,可執行命令“insmod xdma-video.ko width=1280 height=1024 fps=60”,具體的分辨率和幀率大小,請以相機實際可支持范圍為準,分辨率參數需和相機分辨率參數匹配,幀率參數僅作用于軟件上相機參數,不影響實際的相機幀率。

圖 23

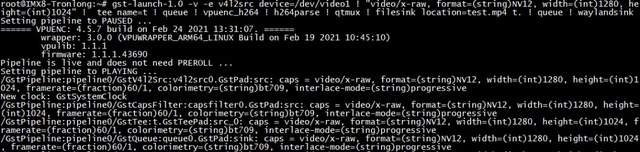

執行如下命令進行圖像的采集、編碼和顯示,編碼后的test.264文件將保存在當前目錄下。

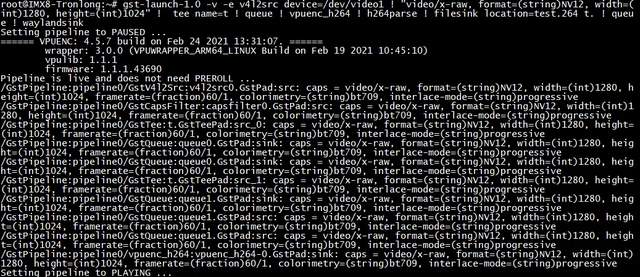

Target# gst-launch-1.0 -v -e v4l2src device=/dev/video1 ! "video/x-raw, format=(string)NV12, width=(int)1280, height=(int)1024" ! tee name=t ! queue ! vpuenc_h264 ! h264parse ! filesink location=test.264 t. ! queue ! waylandsink

其中"/dev/video1"為設備節點,請以實際節點為準,1280和1024為圖像的寬和高。

圖 24

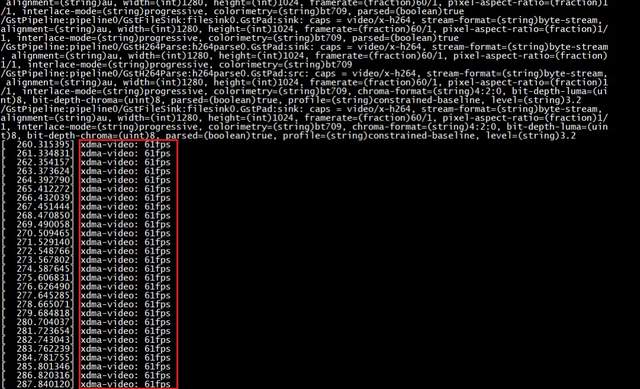

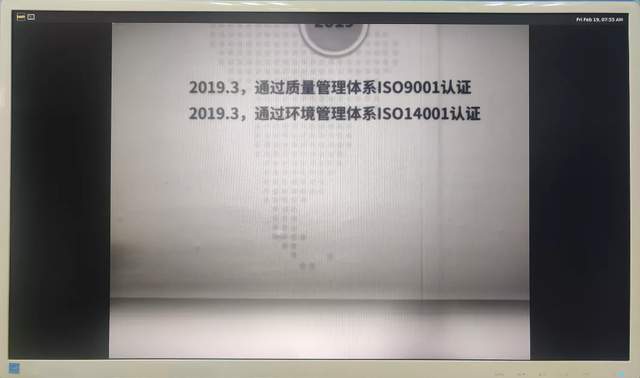

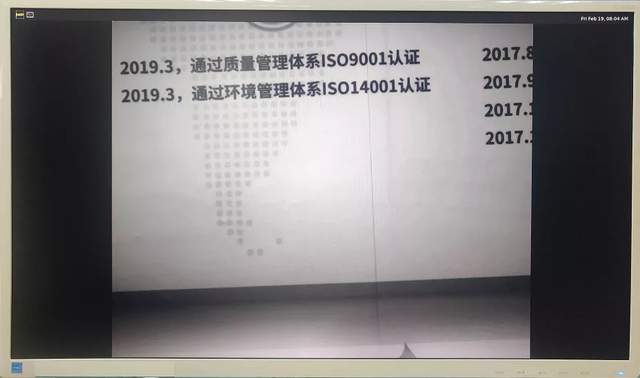

執行成功后可觀察到如下輸出,串口不停打印幀率,并在HDMI顯示器上觀看到實時圖像。

備注:幀率顯示為61fps,是由于CameraLink相機輸出的并不是標準的60fps圖像。

圖 25

圖 26

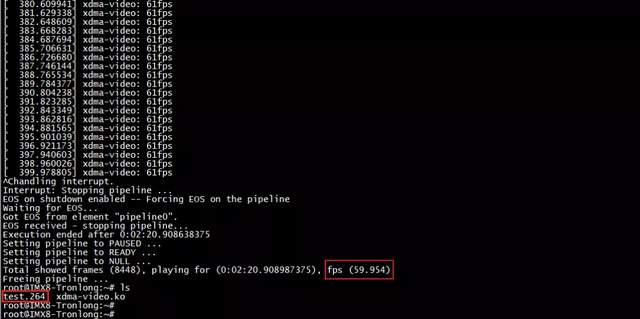

按下“Ctrl+C”停止錄制后,將在當前目錄生成test.264文件,并可觀察到實際幀率為59.954fps。

圖 27

執行如下命令播放編碼后的視頻,HDMI顯示器顯示對應圖像。

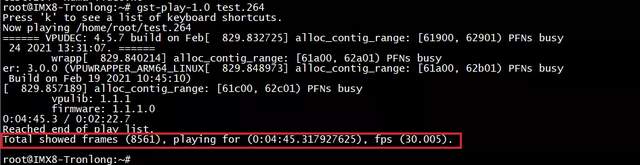

Target# gst-play-1.0 test.264

圖 28

圖 29

播放結束后,將打印視頻時長、幀率信息。

圖 30

備注:由于碼流文件中不包含播放幀率信息,因此在執行“gst-play-1.0 test.264”時未能按60fps進行播放。從串口打印信息可知,實際是以30fps進行播放,并且播放時長為錄制時長的兩倍。在錄制時,將H264碼流封裝成MP4格式可解決此問題,因為封裝成MP4格式時,播放幀率信息將被記錄在MP4文件中。

執行如下命令,可將H264碼流保存成MP4文件。

Target# gst-launch-1.0 -v -e v4l2src device=/dev/video1 ! "video/x-raw, format=(string)NV12, width=(int)1280, height=(int)1024" ! tee name=t ! queue ! vpuenc_h264 ! h264parse ! qtmux ! filesink location=test.mp4 t. ! queue ! waylandsink

圖 31

圖 32

注意:H264碼流保存成MP4文件,程序可正常工作,錄制的視頻文件播放幀率正常,但系統會出現概率性的丟幀。為了避免這種情況,在實際的應用編程中,建議將MP4的保存功能另外建立一個pipeline進行,或改用其它開源MP4庫進行開發。

-

dsp

+關注

關注

553文章

7998瀏覽量

348924 -

FPGA

+關注

關注

1629文章

21736瀏覽量

603384 -

嵌入式

+關注

關注

5082文章

19126瀏覽量

305192 -

Linux

+關注

關注

87文章

11304瀏覽量

209497 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31506

發布評論請先 登錄

相關推薦

PCIe數據傳輸協議詳解

盤古50 pro開發板

盤古50K開發板

PICO-IMX8PL和SRG-IMX8PL:共創您的物聯網集成網關

FPGA的PCIE接口應用需要注意哪些問題

FPGA的高速接口應用注意事項

精選推薦!紫光盤古系列FPGA開發板信息匯總

高速ADDA模塊開箱,FPGA專用,高速信號輸出,數模信號轉換

高速ADDA模塊環路波形展示,FPGA專用

高速ADDA模塊正弦波波形展示,FPGA專用

【正運動】高速高精,超高實時性的PCIe EtherCAT實時運動控制卡 | PCIE464

ELF 1技術貼|在NXP源碼基礎上適配ELF 1開發板的LED功能

【含案例源碼】IMX8基于FlexSPI、PCIe與FPGA的高速通信開發詳解!

【含案例源碼】IMX8基于FlexSPI、PCIe與FPGA的高速通信開發詳解!

評論