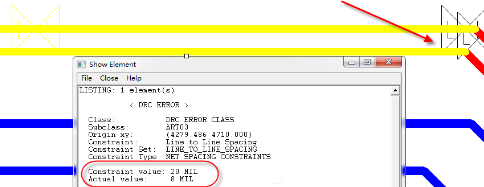

在PCB設計過程中,差分信號是比較重要的信號,一般設置差分信號到其它信號的間距是20mil,但是設置完差分信號到其它信號的間距之后,差分對內PN之間不滿足20mil的間距,會報錯,如1所示:

圖1 差分信號對內報錯示意圖

如圖2所示,差分信號到其它信號的間距是20mil,但是差分按照阻抗線寬走線,間距是8mil,所以出現DRC的錯誤。

本文向大家介紹如何將所有的差分線的設置到其它信號的間距是20mil并滿足自身的阻抗間距不報錯,具體操作步驟如下:

01規則設置

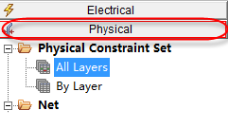

打開規則管理器,執行菜單命令Setup-Constrains,在下拉菜單中選擇Constraint Manager,進行規則設置,左側選擇Physical Constraint Set,如圖2所示,點擊all layers;

圖2 進入物理規則設置示意圖

02設置差分默認間距

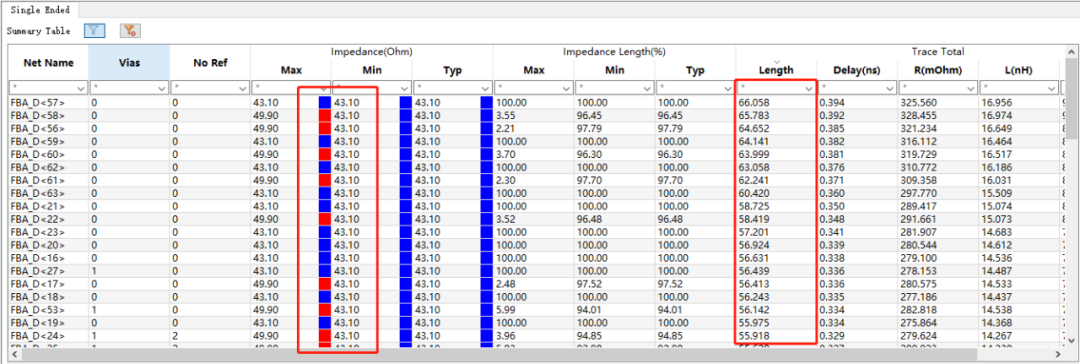

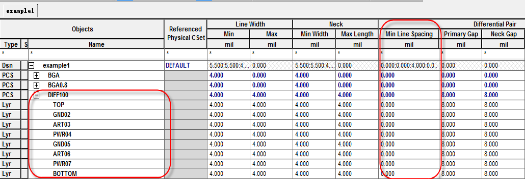

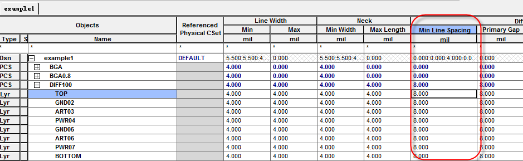

差分走線設置的規則,是DIFF100的規則,在差分屬性的Min Line Spacing最小間距,目前是0,如圖3所示,我們將其設置為差分默認的間距8mil,如圖4所示;

圖3默認差分間距設置示意圖

圖4 差分最小間距設置示意圖

03PCB界面

設置完成以后,回到PCB界面,如圖5所示,差分線已經不會報錯了,對內滿足阻抗要求,對外到其它信號滿足20mil間距。

圖5差分信號不報錯示意圖

-

PCB設計

+關注

關注

394文章

4697瀏覽量

86197

發布評論請先 登錄

相關推薦

高速信號差分線的技術優勢

Altium Designer電氣規則設置后無報錯原因解析

Allegro小技巧 | 如何設置差分線能夠有效減少報錯

Allegro小技巧 | 如何設置差分線能夠有效減少報錯

評論