仿真和驗證是開發任何高質量的基于 FPGA 的 RTL 編碼過程的基礎。在上一篇文章中,我們介紹了面向實體/塊的仿真,即通過在每個輸入信號上生成激勵并驗證 RTL 代碼行為是否符合預期,對構成每個 IP 核的不同模塊進行實體/塊的仿真。

前文回顧

如何測試與驗證復雜的FPGA設計(1)——面向實體或塊的仿真

在本篇文章中,我們將介紹如何在虹科IP核中執行面向全局的仿真,而這也是測試與驗證復雜FPGA設計的第二個關鍵步驟。

面向全局的仿真

全局仿真意味著驗證整個IP實體的正確行為,包括構成產品的每個子模塊。為了適應不同客戶的用例,虹科SoC-e IP核解決方案在設計時充分考慮了靈活性,這意味著虹科所有的IP核都是高度可配置的,無論是在集成時(以優化 FPGA 中的封裝)還是在運行時。借助于有著不同接口選項的寄存器映射(在下面的示例中,使用 AXI4),運行時配置成為可能。

這種靈活性也對仿真過程提出了挑戰,因為需要根據仿真環境中的不同測試用例來配置IP。對此,虹科的合作伙伴SoC-e團隊開發了一個令人驚嘆的智能測試平臺環境,在該環境中可以進行實時配置并實現自動化,開發人員可以通過“點擊即用”的方式來執行復雜的仿真。例如,測試臺可以通過交換機發送以太網幀,并可以通過訪問IP 核的統計寄存器來讀取結果(并檢查輸出是否符合預期)。

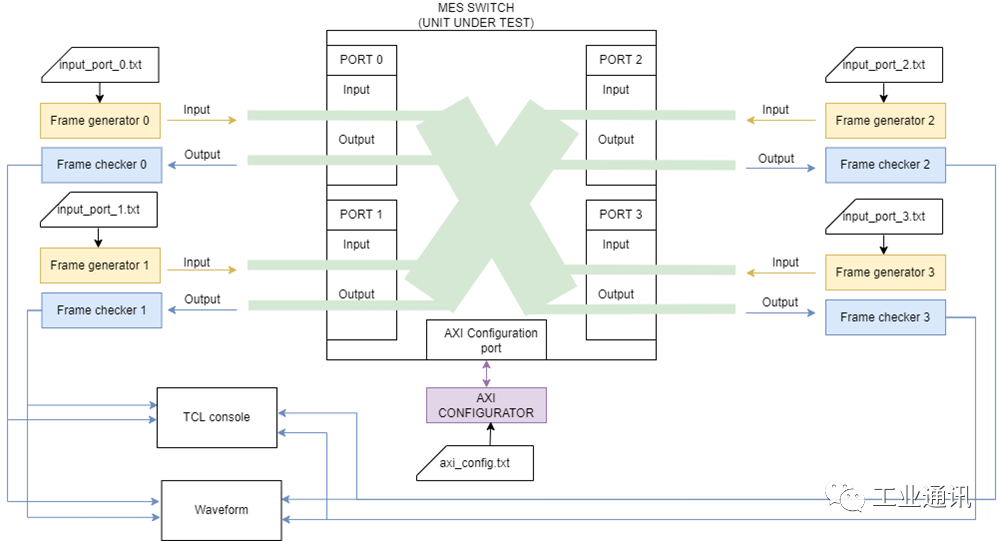

這極大地加快了調試過程,并允許開發團隊執行快速迭代,而這在基于硬件的測試環境中會慢得多。在下圖為具有此類全局測試平臺架構的框圖(基于虹科網管以太網交換機IP核):

網管型以太網交換機 (MES) 表示為UUT。其余的測試臺組件是符合整個環境的不可綜合的 VHDL 模塊:

Frame Generator::該模塊連接到以太網交換機 IP 的入口端口,負責生成激勵(以太網幀)。

Frame Checker:該模塊連接到以太網交換機IP的出端口,負責分析交換機轉發的流量。

AXI Configurator:它控制 AXI4 配置總線以修改配置寄存器的內容(讀/寫操作)。

測試平臺執行流程

正常的測試平臺執行流程如下:首先,AXIConfigurator模塊根據測試用例配置IP核。之后,每個FrameGenerator都會生成測試幀,并將其發送到啟用的入口端口。幀是通過循環重復某些特定測試文件中定義的內容來生成的。最后,Frame Checker接收幀(接收與否,取決于測試用例)。該塊將檢查每個端口對應的統計信息,并根據執行的測試用例確定輸出是否符合預期的。

虹科SoC-e測試平臺架構的一大亮點是Frame Checker可以自動檢測多種錯誤,例如完整性錯誤、轉發錯誤或幀丟失。這是可實現的,因為Frame Generator可以生成具有特定格式的流量(例如有效載荷中的特殊模式、序列號等),Frame Checker可以解釋這些流量。

測試平臺測試計劃

該測試平臺套件的驚人靈活性還與SoC-e定義的嚴格測試計劃相結合。對于每個IP核,都有一個測試計劃,旨在在仿真環境中測試盡可能多的特性。

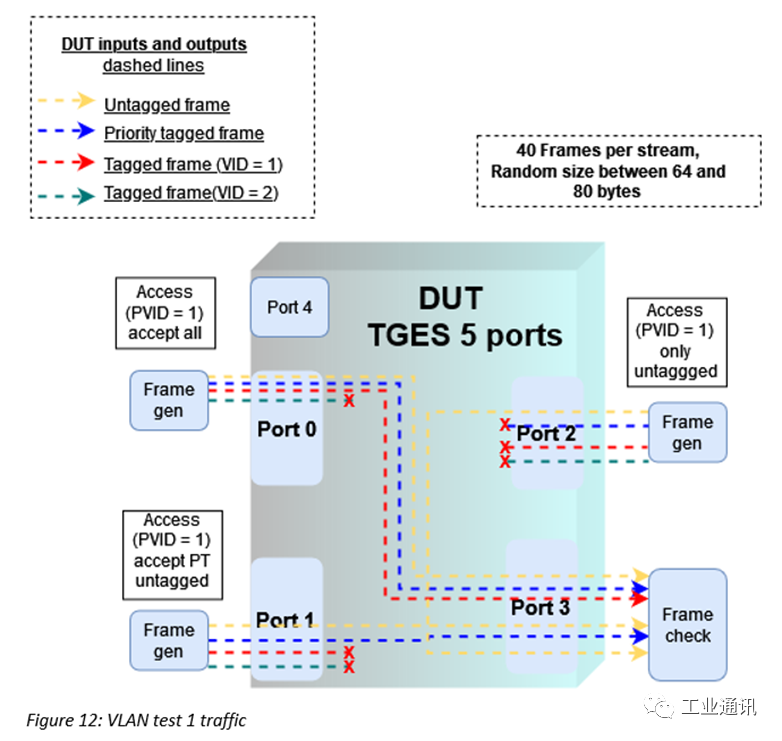

例如,網管以太網交換機IP的測試計劃可以被劃分為五個主要部分:

通用交換

自定義轉發

過濾數據庫

優先隊列

這些部分旨在涵蓋與網絡相關的不同功能的行為,以及不同的流量模式和情況。

測試平臺的結果可以由開發人員或用戶以不同的方式進行分析。TCL控制臺用于快速反饋測試結果。然而,在某些情況下,在仿真的特定時刻深入了解特定信號值可能會很有趣。對于這種情況,還開發了預先格式化的波形,以便于查找特定信號。

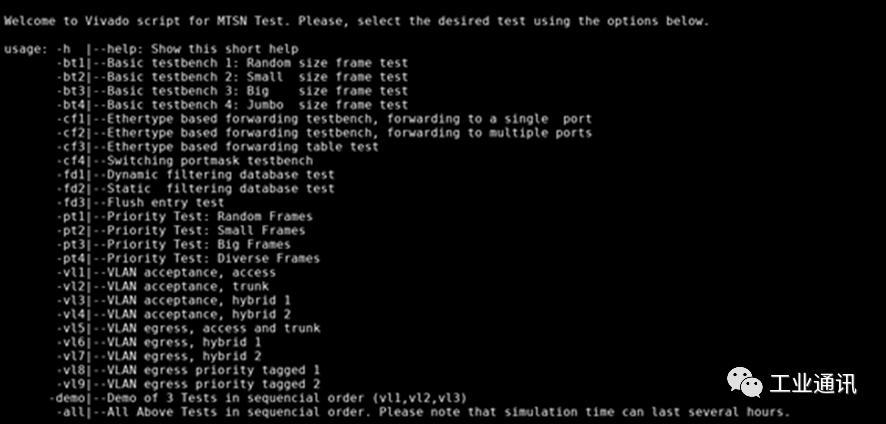

用于測試執行的命令行界面(CLI)

此測試平臺環境中包含的最新功能之一是可以直接從命令行界面(CLI)執行所有測試,而無需打開RTL仿真工具(Vivado或其他工具)。這是一個很大的改進,因為它可以實現更高的測試自動化。它基于使用Vivado編譯器命令的腳本(Python)的使用,以便用戶生成易于解釋的結果。

下圖顯示了向用戶顯示的仿真菜單。用戶只需選擇相應的選項即可執行任何列出的測試:

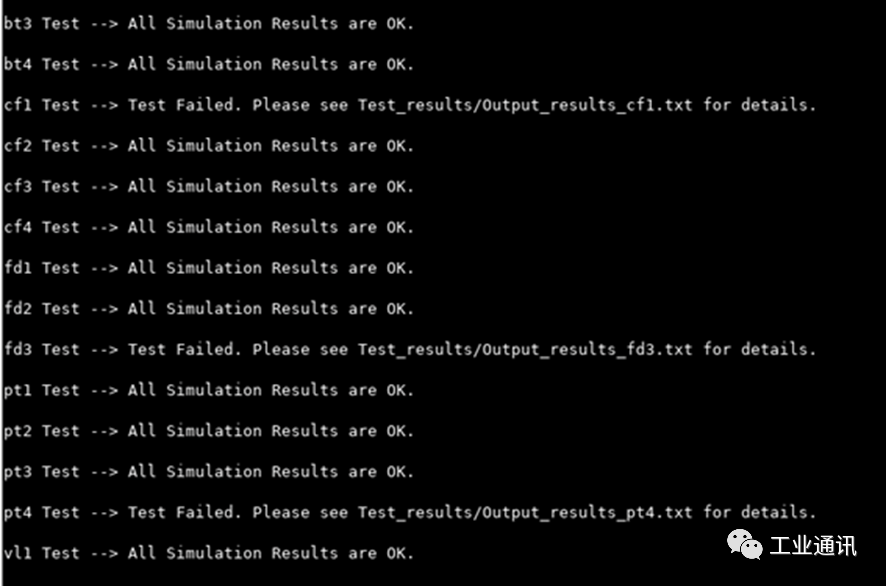

眾所周知,仿真是一個需要大量時間的過程。即使在功能強大的計算機中執行,毫秒或以上范圍內的復雜仿真也需要持續數十分鐘,甚至更長。為了簡化執行所有測試的過程(這需要幾個小時),我們實現了一個“-all”選項,它允許在管道中執行所有測試,且無需用戶交互。完成所有測試后,它將提供有關每個測試的報告消息(如下圖所示),并在測試失敗的情況下生成輸出文件,以便開發人員稍后進行分析。

-

仿真

+關注

關注

50文章

4111瀏覽量

133784 -

IP核

+關注

關注

4文章

330瀏覽量

49558

發布評論請先 登錄

相關推薦

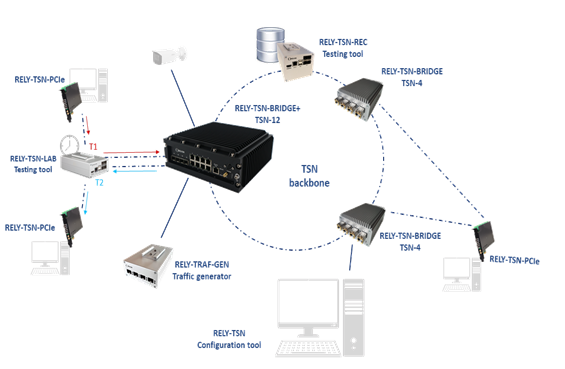

虹科方案 僅需4個步驟!輕松高效搭建虹科TSN測試網絡

虹科技術前沿 TSN網絡中時間感知整形器的性能驗證實測

測試與驗證復雜的FPGA設計(2)——如何在虹科的IP核中執行面向全局的仿真

測試與驗證復雜的FPGA設計(2)——如何在虹科的IP核中執行面向全局的仿真

評論