概述

AT32F4xx使用的是ARM Cortex-M4F內核。ARM Cortex-M4F是帶有FPU內核處理器是一款32位的RISC處理器,具有優(yōu)異的代碼效率,采用通常8位和16位器件的存儲器空間即可發(fā)揮ARM內核的高性能。該處理器支持一組DSP指令,能夠實現(xiàn)有效的信號處理和復雜的算法執(zhí)行。其單精度FPU(浮點單元)通過使用元語言開發(fā)工具,可加速開發(fā),防止飽和。

本文重點介紹基于AT32 MCU的DSP指令相關庫函數及其簡單應用示例,主要內容有:

- ARM Cortex-M4F內核

- ARM官方CMSIS DSP庫概述

- CMSIS DSP庫移植到AT32

- 常用示例展示

- CMSIS NN with DSP

注意:本文是基于AT32F403A的硬件條件,若使用者需要在AT32其他型號上使用,請修改相應配置即可。

AT32 MCU與M4F內核

AT32F403A系列與所有的ARM工具和軟件兼容。這些豐富的外設配置,使得AT32系列微控制器適合于多種應用場合:

- 消費類產品

? 手持云臺? 微型打印機? 條形碼掃描槍? 讀卡器? 燈光控制

- 工業(yè)應用

? 雙CAN應用(OBD-II)? 光電編碼器? 充電樁/BMS? 機器人控制? 電力控制

系統(tǒng)架構

AT32F403A系列微控制器包括ARM CortexTM-M4F處理器內核、總線架構、外設以及存儲器構成。CortexTM-M4F處理器是一種新時代的內核,擁有許多先進功能。對比于CortexTM-M3,CortexTM-M4F處理器支持增強的高效DSP指令集,包含擴展的單周期16/32位乘法累加器MAC、雙16位MAC指令、優(yōu)化的8/16位SIMD運算及飽和運算指令,并且具有單精度IEEE-754浮點運算單元FPU。當設計中使用帶DSP功能的CortexTM-M4F時就能格外節(jié)能,比軟件解決方案更快,使CortexTM-M4F適用于那些要求微控制器提供高效能與低功耗的產品市場。

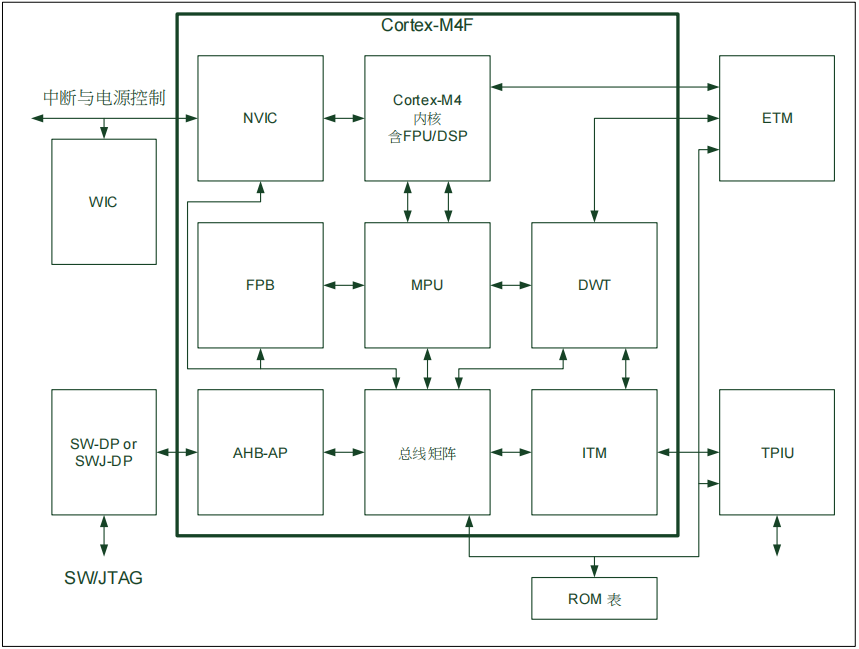

1) Cortex-M4內核架構

圖1. Cortex-M4內核架構

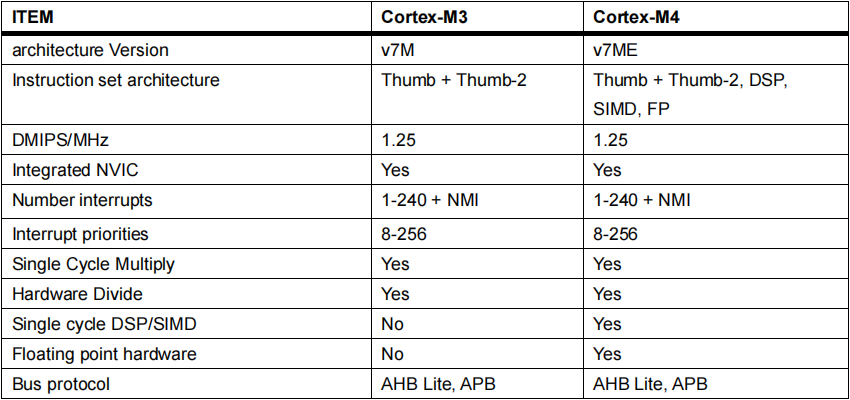

2)Cortex-M4與Cortex-M3的區(qū)別

表1. Cortex-M4與Cortex-M3的區(qū)別

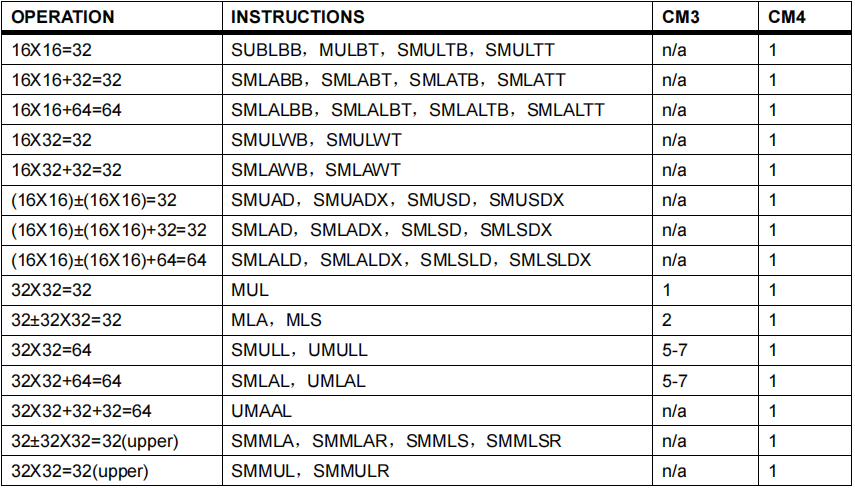

3)部分DSP指令的介紹

表2. 單周期MAC指令介紹 注意:上面所有的指令操作在CM4處理器上都只需一個指令周期。

注意:上面所有的指令操作在CM4處理器上都只需一個指令周期。

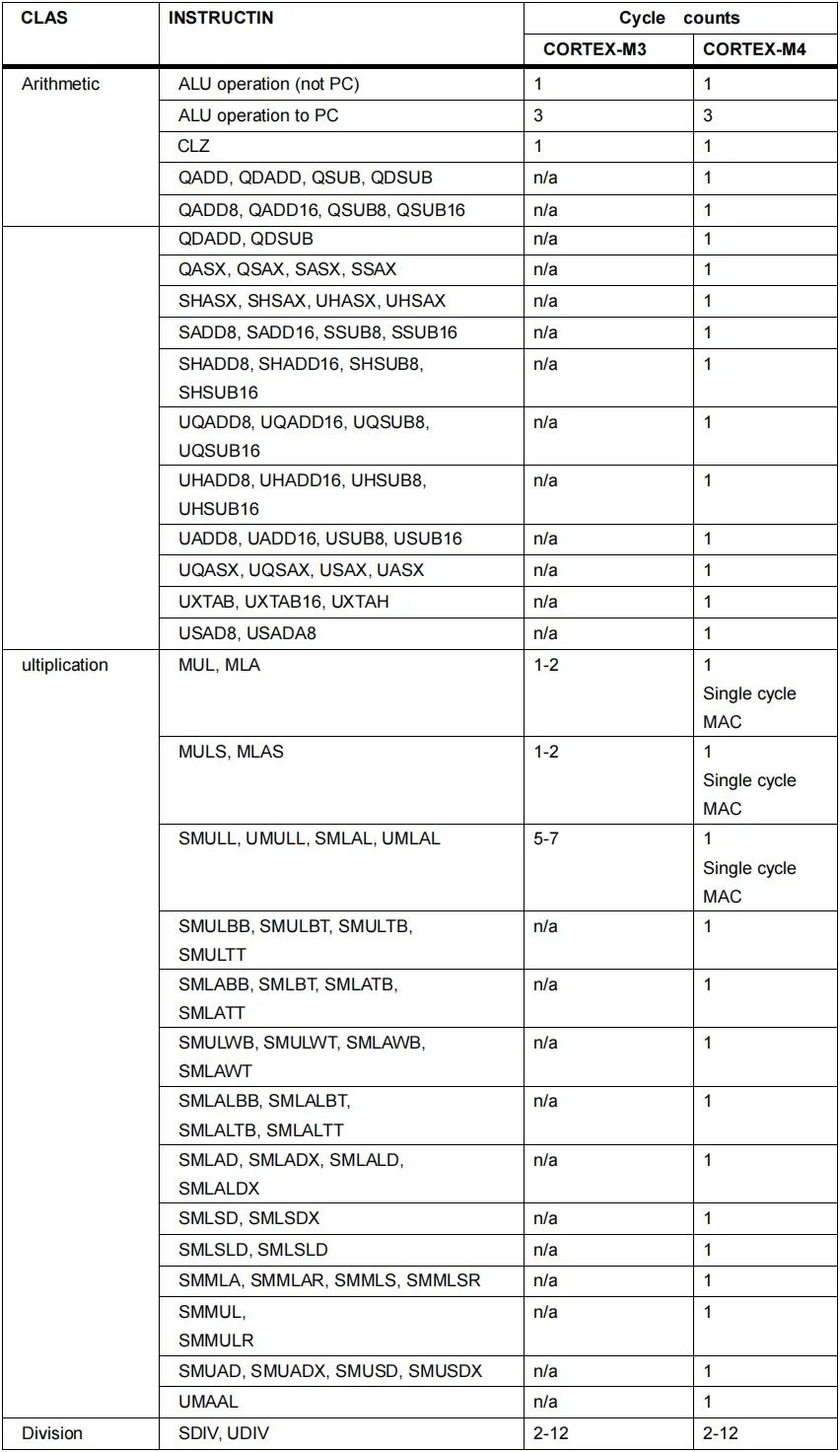

4)Cortex-M4 DSP指令比較

表3. Cortex-M4 DSP指令比較

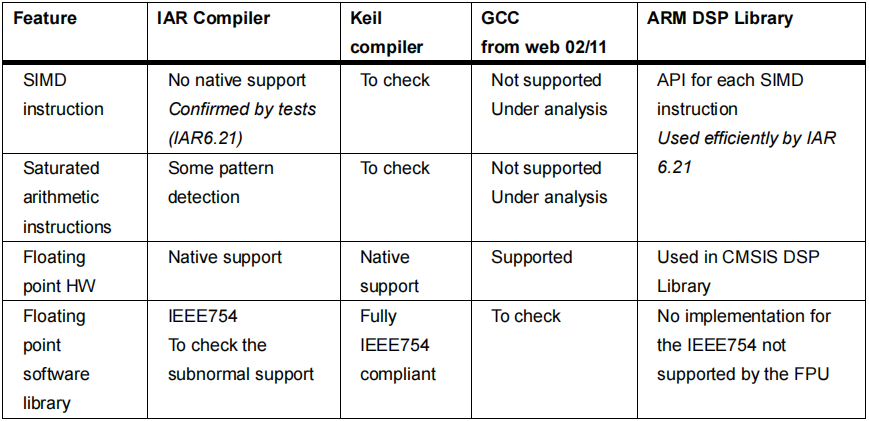

5)編譯器對DSP指令的支持

表4. 編譯器對DSP指令的支持

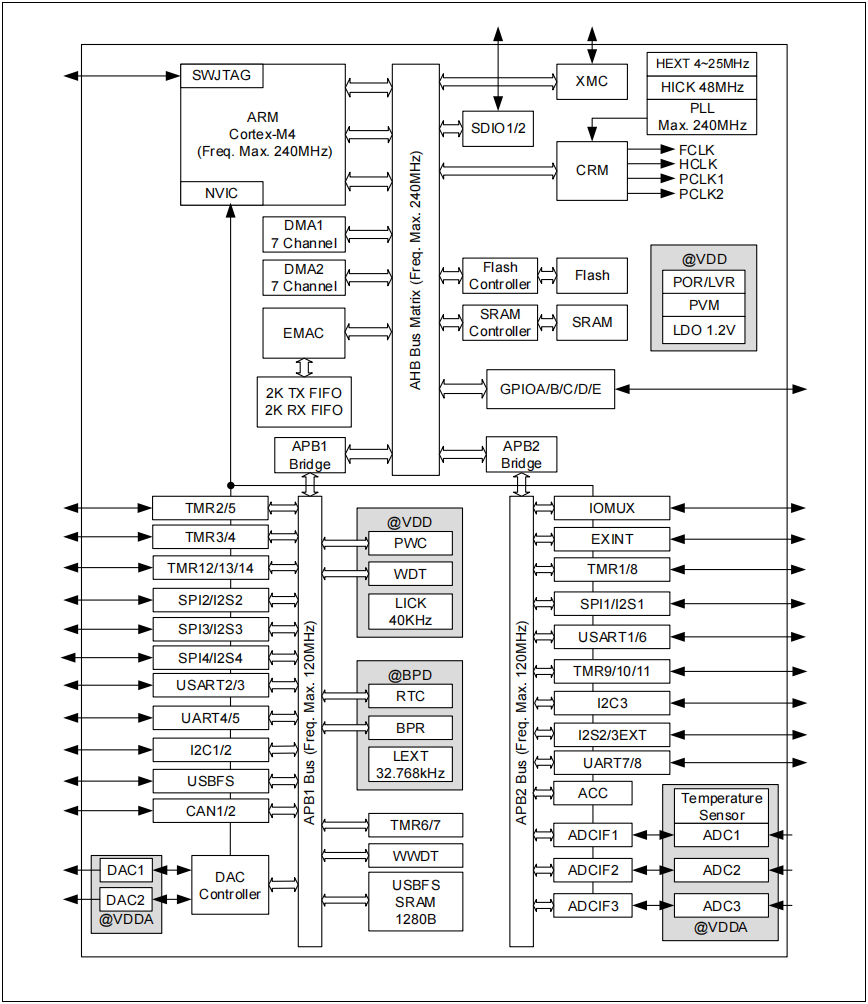

6)AT32F403A系統(tǒng)架構

圖2. AT32F403A系統(tǒng)架構圖 注意:AT32F403A不支持EMAC,AT32F407/407A支持EMAC

注意:AT32F403A不支持EMAC,AT32F407/407A支持EMAC

ARM官方CMSIS DSP庫概述

CMSIS DSP庫說明

CMSIS DSP軟件庫,是針對使用Cortex-M內核芯片提供一套數字信號處理函數。CMSIS DSP庫大部分函數都是支持f32,Q31,Q15和Q7四種格式的。該庫分為以下幾個功能:

- 基本數學函數Basic math functions

- 快速數學函數Fast math functions

- 復數型數學函數Complex math functions

- 濾波器函數Filters

- 矩陣型函數Matrix functions

- 數學變換型函數Transform functions

- 電機控制函數Motor control functions

- 統(tǒng)計型數學函數Statistical functions

- 支持型數學Support functions

- 插補型數學函數Interpolation functions

針對以上每一種類型的庫函數,下文會有詳細介紹其使用方法和使用示例。

CMSIS DSP庫文件

考慮到方便用戶使用,ARM官方已編譯好Cortex-M各型號的.lib庫文件,并放置于Lib文件夾。與AT32F4xx相關的.Lib庫文件主要有以下兩種

- arm_cortexM4lf_math.lib (Cortex-M4, Little endian, Floating Point Unit) for AT32F403 and AT32F413

- arm_cortexM4l_math.lib (Cortex-M4, Little endian) for AT32F415

DSP庫函數的聲明位域頭文件arm_math.h中,用戶只要簡單地將該頭文件和.lib文件添加到自己的工程中,即可呼叫DSP庫函數。該頭文件對于浮點運算單元(FPU)的變量同樣適用。

CMSIS DSP庫示例

該CMSIS DSP庫中的多個示例可以很好地展現(xiàn)DSP庫函數的使用。

CMSIS DSP庫的工具鏈支持

該DSP庫已經可以在5.14版本MDK上開發(fā)和測試過。另外針對GCC編譯器和IAR IDE,已經支持。

編譯生成DSP的.lib庫文件

該DSP安裝包中已包含一個基于MDK的工程,通過編譯該工程可生成需要的.lib庫文件。該MDK工程位于CMSIS\DSP\Projects\ARM文件夾中。工程名為

- arm_cortexM_math.uvprojx

通過打開并編譯該arm_cortexM_math.uvprojx MDK工程,可以生成該DSP的.lib庫文件。這樣用戶就可以根據特定的內核,特定的優(yōu)化選擇去編譯特定DSP的.lib庫文件。同時,通過該MDK工程,用戶也可以查看與修改指定的庫函數原型,便于了解庫函數的實現(xiàn)原理。

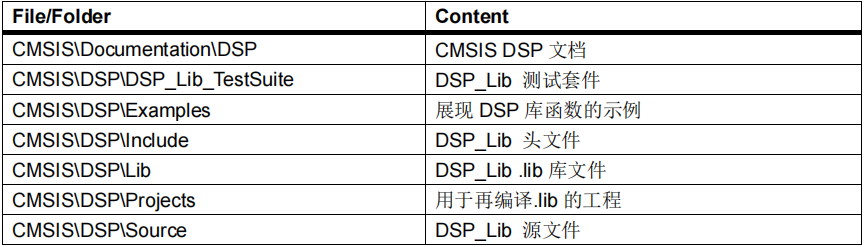

CMSIS-DSP文件夾結構

以下表格展現(xiàn)了CMSIS-DSP文件夾結構表5. CMSIS-DSP文件夾結構

CMSIS DSP庫移植到AT32

本文主要介紹DSP庫在MDK上的移植方法。

ARM官方CMSIS DSP函數詳解

- 基本數學函數Basic math functions

- 快速數學函數Fast math functions

- 復數型數學函數Complex math functions

- 濾波器函數Filters

- 矩陣型函數Matrix functions

- 數學變換型函數Transform functions

- 電機控制函數Motor control functions

- 統(tǒng)計型數學函數Statistical functions

- 支持型數學Support functions

- 插補型數學函數Interpolation functions

詳細使用方法和使用案例請參考1) ARM官網DSP培訓資料地址:http://www.keil.com/pack/doc/CMSIS_Dev/DSP/html/index.html

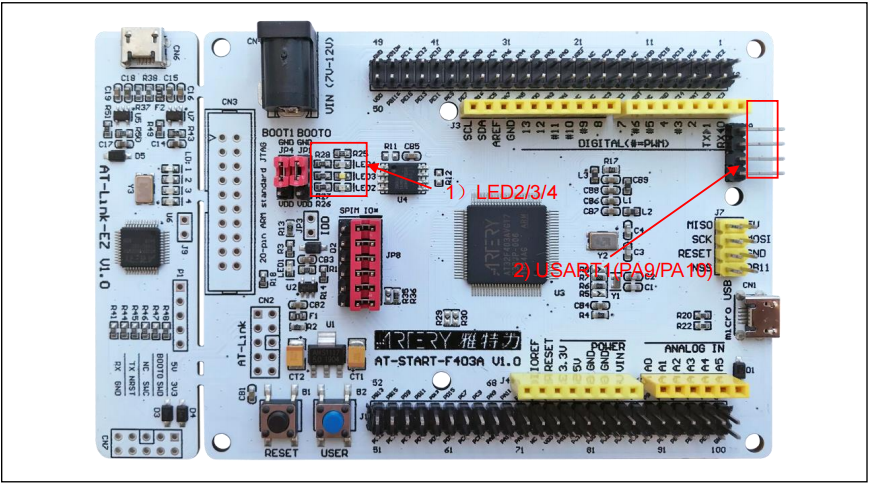

AT32 DSP庫快速使用

硬件資源1) 指示燈LED2/LED3/LED42) USART1(PA9/PA10)3) AT-START-F403A V1.0實驗板圖3. AT-START-F403A V1.0實驗板 注:該DSP demo是基于AT32F403A的硬件條件,若使用者需要在AT32其他型號上使用,請修改相應配置即可。軟件資源

注:該DSP demo是基于AT32F403A的硬件條件,若使用者需要在AT32其他型號上使用,請修改相應配置即可。軟件資源

1) Libraries

- drivers AT32底層驅動庫

- cmsis CMSIS DSP庫和CMSIS NN庫

2) Project\AT_START_F403A

- examples,本文使用到的示例,如5_1_arm_class_marks_example,“5_1”表示章節(jié),“arm_class_marks_example”表示示例名稱

- templates,基于.lib建立的DSP template工程

3) Doc

a) AN0036_DSP_Instruction_and_Library_on_AT32_ZH_V2.x.x.pdf

DSP demo使用1) 打開AT32_DSP_DEMO_2.x.x\project\at_start_xxx\templates,編譯后下載到實驗板

2) 觀察LED2/LED3/LED4,若依次翻轉則表明程序有正確執(zhí)行DSP函數。

常用示例展示

本節(jié)主要通過使用前面介紹的DSP庫函數進行案列展示,展示的示例如下:

班級成績統(tǒng)計示例

描述:演示使用最大,最小,均值,標準差,方差和矩陣函數來統(tǒng)計一個班級的成績。注意:此示例還演示了靜態(tài)初始化的用法。變量說明:

- testMarks_f32:指向20名學生在4門學科中獲得的分數

- max_marks:最高分成績

- min_marks:最低分成績

- mean:所有成績的平均分

- var:所有成績的方差

- std:標準差

- numStudents:學生總數

使用到DSP軟件庫的函數有:

- arm_mat_init_f32()

- arm_mat_mult_f32()

- arm_max_f32()

- arm_min_f32()

- arm_mean_f32()

- arm_std_f32()

- arm_var_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_1_arm_class_marks_example

卷積示例

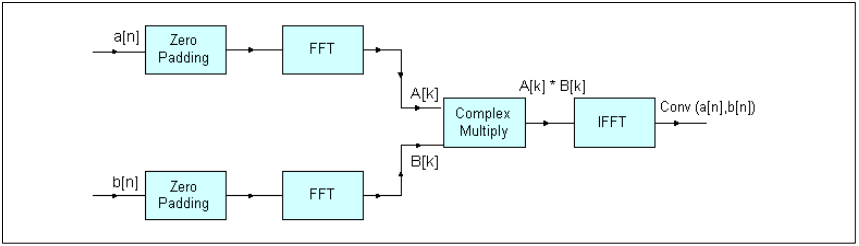

描述:本示例主要展示基于復數 FFT、復數乘法與支持函數的卷積理論。

算法:

卷積理論指出,時域中的卷積對應頻域中的乘法。因此,兩個信號的卷積后的傅里葉變換等于他們各自的傅里葉變換的乘積。使用快速傅里葉變換(FFT)可以有效的評估信號的傅里葉變換。兩個輸入信號a[n]和b[n]填充為零,n1和n2分別對應其信號長度。因此他們的長度將變?yōu)镹,N大于或等于n1+n2-1。由于采用基4變換,因此基數為4。a[n]和b[n]的卷積是通過對輸入信號進行FFT變換,對聯(lián)更新好進行傅里葉變換。并對相乘后的結果進行逆FFT變換來獲得的。

由以下公式表示:

A[k]=FFT(a[n],N)B[k]=FFT(b[n],N)conv(a[n], b[n])=IFFT(A[k]*B[k], N)其中A[k]和B[k]分別是信號a[n]和b[n]的N點FFT。卷積長度為n1+n2-1

框圖:

圖4. 卷積算法框圖 變量說明

變量說明

- testInputA_f32:指向第一個輸入序列

- srcALen: 第一個輸入時序的長度

- testInputB_f32:指向第二個輸入序列

- srcBLen:第二個輸入時序的長度

- outLen:卷積輸出序列的長度,(srcALen+srcBLen-1)

- AxB:指向FFT乘積后輸出數組地址

使用到DSP軟件庫的函數有:

- arm_fill_f32()

- arm_copy_f32()

- arm_cfft_radix4_init_f32()

- arm_cfft_radix4_f32()

- arm_cmplx_mult_cmplx_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_2_arm_convolution_example

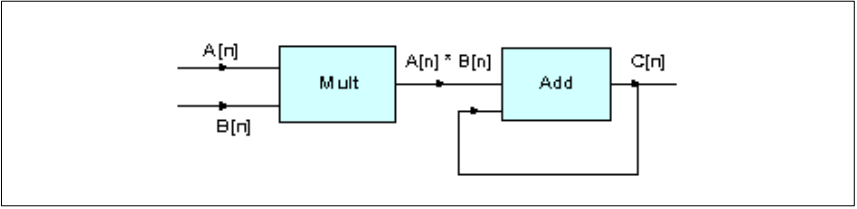

點積示例

描述:本示例主要展示如何使用相乘和相加來實現(xiàn)點積。兩個向量的點積是通過將對應元素相乘并相加來獲得的。

算法:

將長度為n的兩個輸入向量A和B諸個元素相乘,然后相加以獲得點積。

由以下公式表示:

dotProduct=A[0]*B[0]+A[1]*B[1]+...+A[n-1]*B[n-1]

框圖:

圖5. 點積算法框圖

變量描述:

- srcA_buf_f32:指向第一個輸入向量

- srcB_buf_f32:指向第二個輸入向量

- testOutput:存儲兩個向量的點積

使用到DSP軟件庫的函數有:

- arm_mult_f32()

- arm_add_f32()

參考AT32_DSP_DEMO\project\at_start_f403a\examples\5_3_arm_dotproduct_example

頻率倉示例

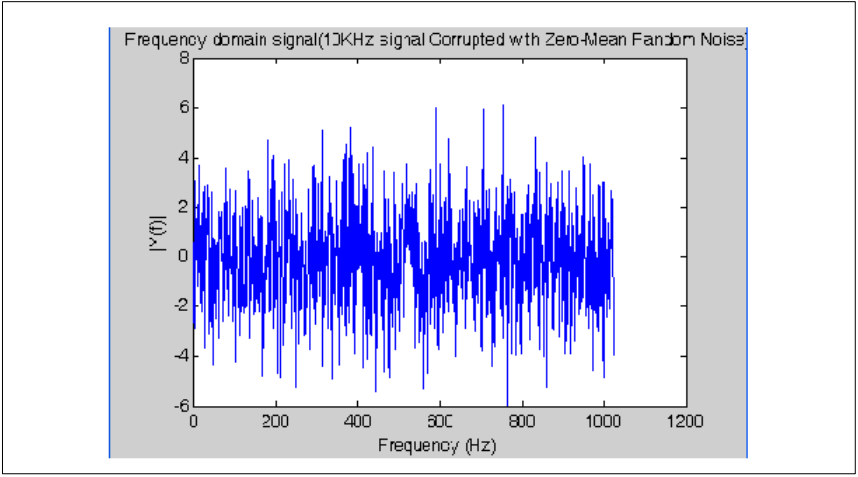

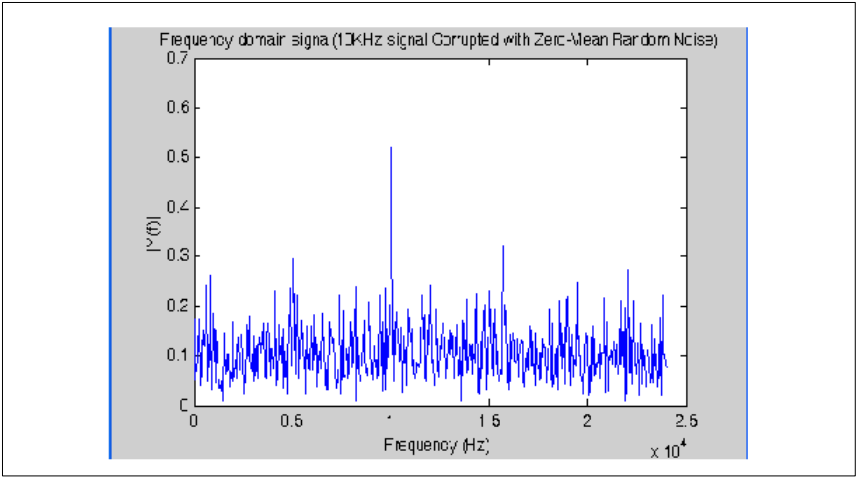

描述:該示例主要展示使用復數FFT,復數幅值和最大值函數在輸入信號的頻域中計算最大能量倉。

算法:

輸入測試信號為一個10 kHz信號,該信號具有均勻分布的白噪聲。通過計算輸入信號的FFT計算可以得到與10 kHz輸入頻率相對應的最大能量倉。

框圖:

圖6. 頻率倉算法框圖

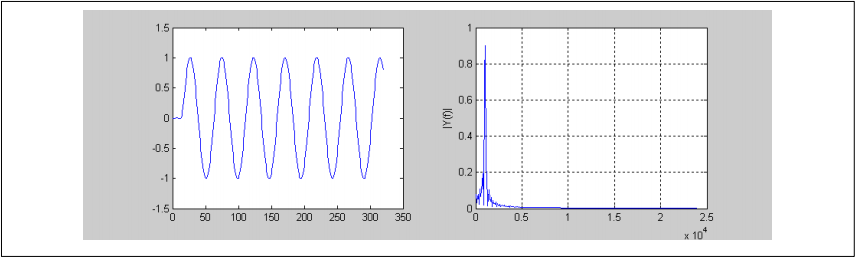

圖8展示了具有均勻分布白噪聲的10 kHz信號的時域信號,圖9展示了這個輸入信號的對應的頻域信號,其中出現(xiàn)最高點的數對應的頻率即為10 kHz信號能量倉。

圖7. 輸入信號的時域

圖8. 輸入信號的頻域

輸入信號的頻域變量描述

輸入信號的頻域變量描述

- testInput_f32_10khz:指向輸入數據

- testOutput:指向輸出數據

- fftSize l:FFT的長度

- ifftFlag flag:用于選擇 CFFT/CIFFT

- doBitReverse Flag:用于選擇是順序還是逆序

- refIndex:參考索引值,在該值處能量最大

- testIndex:計算出的索引值,在該值處能量最大

使用到DSP軟件庫的函數有:

- arm_cfft_f32()

- arm_cmplx_mag_f32()

- arm_max_f32()

參考AT32_DSP_DEMO\project\at_start_f403a\examples\5_4_arm_fft_bin_example

FIR低通濾波示例

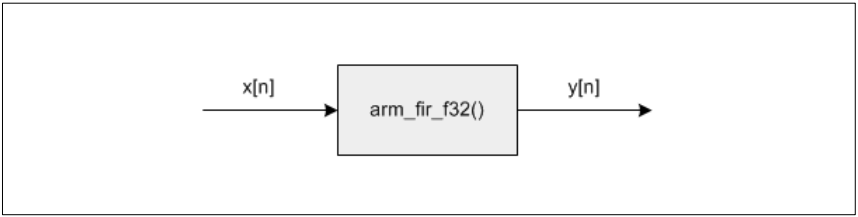

描述:使用FIR低通濾波器從輸入中去除高頻信號部分。本示例展示了如何配置FIR濾波,然后以塊方式傳遞數據。圖9. FIR低通濾波算法框圖

算法:

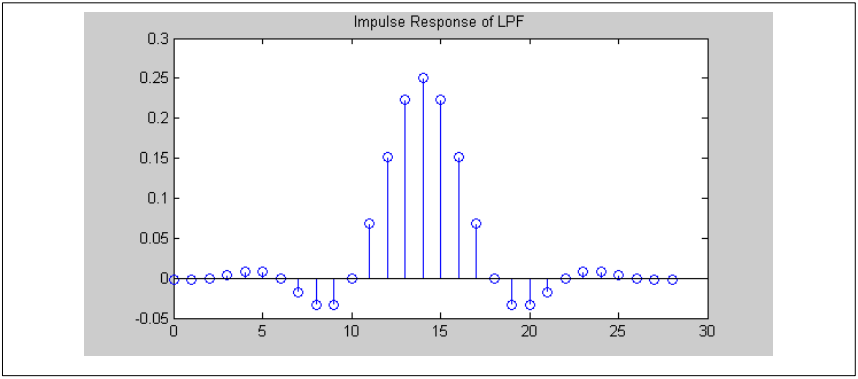

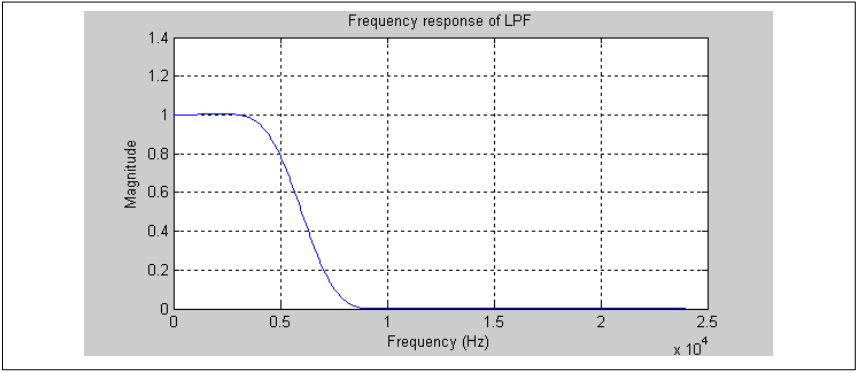

輸入信號時兩個正弦波的疊加:1 kHz and 15 kHz.該信號將被截止頻率為6 kHz的進行低通濾波。低通濾波器濾掉了15 kHz信號,僅留下1 kHz信號輸出。低通濾波器采用MATLAB設計,采樣率為48 kHz,長度為29點。生成濾波器的MATLAB代碼如下:h=fir1(28, 6/24);第一個參數是過濾器的“順序”,并且總是比所需長度小1,。第二個參數是歸一化截止頻率。范圍是0(DC)到1.0(Nyquist)。24 kHz奈奎斯特頻率的6kHz截止頻率為6/24=0.25歸一化頻率。CMSIS FIR濾波器函數要求系數按時間倒序排列。所得濾波器系數如下圖所示。需要注意的是,該濾波器是對稱的(線性相位FIR濾波器的屬性)。對稱點是樣本14,對于所有頻率,該濾波器具有14個樣本的延遲。圖10. 低通濾波時域響應

接下來顯示濾波器的響應。濾波器的帶通增益為1.0,截止頻率為6kHz時達到0.5。

圖11. 低通濾波頻域響應

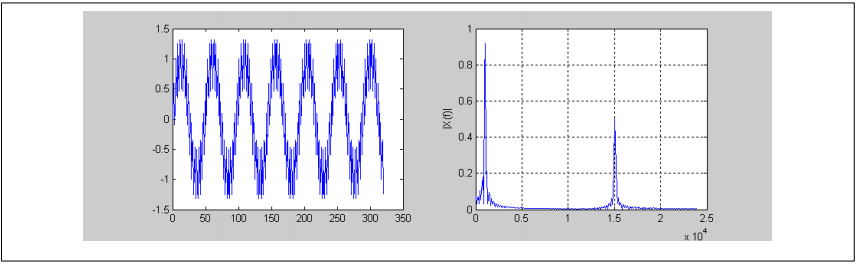

輸入信號如下所示。左側顯示時域信號,右側顯示頻域。可以清楚的看到兩個正弦波分量。

圖12. 輸入信號的時域信號和頻域信號

濾波器輸出如下所示,15kHz分量已被消除。

圖13. 輸出信號的時域信號和頻域信號

變量描述:

- testInput_f32_1kHz_15kHz:指向輸入數據

- refOutput points to the reference output data:指向參考輸出數據

- testOutput points to the test output data:指向測試輸出數據

- firStateF32 points to state buffer:指向狀態(tài)緩沖區(qū)

- firCoeffs32 points to coefficient buffer:指向系數緩沖區(qū)

- blockSize number of samples processed at a time:一次處理的樣本數

- numBlocks number of frames:幀數

使用到DSP軟件庫的函數有:

- arm_fir_init_f32()

- arm_fir_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_5_arm_fir_example

圖形音頻均衡器示例

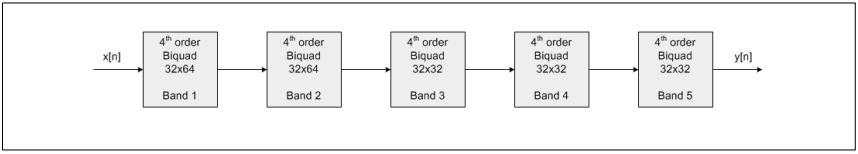

描述:本示例展示了如何使用Biquad級聯(lián)函數構造5頻段圖形均衡器。在音頻應用中使用圖形均衡器來改變音頻的音質。

框圖:

該設計是基于五級濾波器的級聯(lián)圖14. 五級濾波器聯(lián)算法框圖

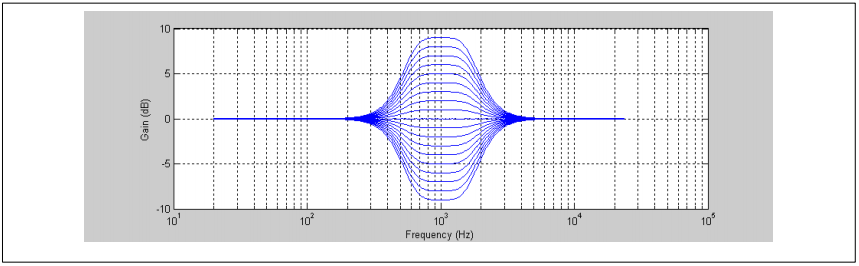

每個濾波器部分均為40階,由兩個Biquad級聯(lián)組成。每個濾波器的標稱為0 dB(線性單位為1.0)并對特定頻率范圍內的信號進行增強或截止。5個頻率段之間的邊緣頻率為100、500、2000和6000 Hz。每個頻段都有一個可調的增強或消減范圍,范圍為+/- 9 dB。列如,從500到2000 Hz的頻寬具有如下所示響應:

圖15. 從200Hz到2KHz的頻寬響應

以1 dB為步長,每個濾波器共有19種不同的設置。在MATLAB中預先計算了所有19中可能設置的頻率器系數,并將其存儲在表格中。使用5個不同表格,總共有5x19=95個不同的4階過濾器。所有95個響應如下所示:

圖16. 19X5頻率系數的過濾器響應

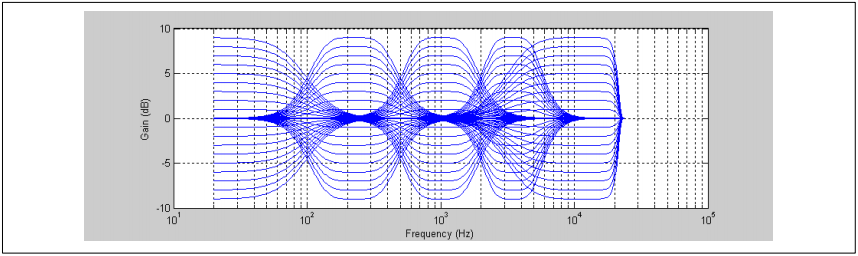

每個4階濾波器具有10個系數,意味著排列成950個不同濾波器系數。輸入和輸出數據為Q31模式。為了獲得更好的噪聲性能,兩個低頻算使用高精度 32x64 位雙二階濾波器。本示例中的輸入信號使用對數線性調頻。

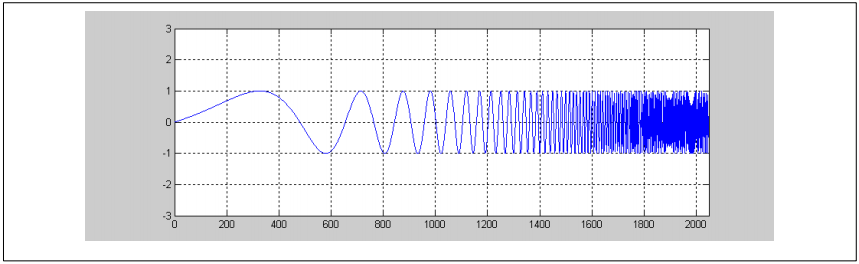

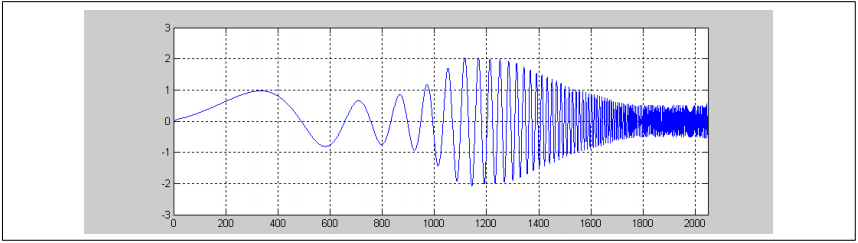

圖17. 輸入信號對數線性調頻

數組bandGains指定以dB為單位的增益應用于每個帶寬。例如,如果bandGains={0, -3, 6, 4, -6};那么輸出信號將是:

圖18. bandGains調頻輸出信號

注意:

輸出線性調頻信號跟隨著每個帶寬的增益或增強而變化。變量描述:

- testInput_f32:指向輸入數據

- testRefOutput_f32:指向參考輸出數據

- testOutput:指向測試輸出數據

- inputQ31:臨時輸入緩沖區(qū)

- outputQ31:臨時輸出緩沖區(qū)

- biquadStateBand1Q31:指向band1的狀態(tài)緩沖區(qū)

- biquadStateBand2Q31:指向band2的狀態(tài)緩沖區(qū)

- biquadStateBand3Q31:指向band3的狀態(tài)緩沖區(qū)

- biquadStateBand4Q31:指向band4的狀態(tài)緩沖區(qū)

- biquadStateBand5Q31:指向band5的狀態(tài)緩沖區(qū)

- coeffTable:指向所有頻段的系數緩沖區(qū)

- gainDB:增益緩沖器,其增益適用于所有頻段

使用到DSP軟件庫的函數有:

- arm_biquad_cas_df1_32x64_init_q31()

- arm_biquad_cas_df1_32x64_q31()

- arm_biquad_cascade_df1_init_q31()

- arm_biquad_cascade_df1_q31()

- arm_scale_q31()

- arm_scale_f32()

- arm_float_to_q31()

- arm_q31_to_float()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_6_arm_graphic_equalizer_example

線性插值示例

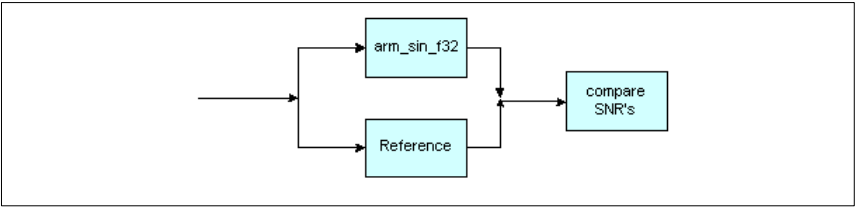

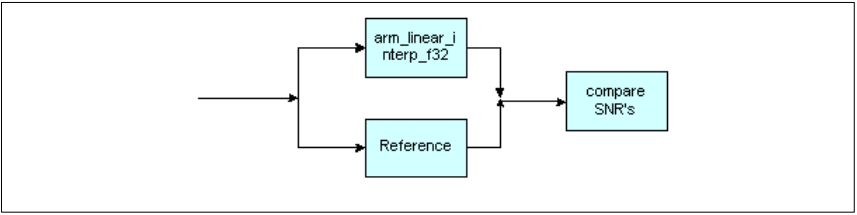

描述:本案示例展示了線性插值模型和快速數學模型的用法。方法1使用快速數學正弦函數通過三次插值計算正弦值。方法2使用線性插值函數并將結果與參考輸出進行比較。示例顯示,與快速數學正弦計算相比,線性插值函數可用于獲得更高的精度。

算法1:使用快速數學函數進行正弦計算

圖19. 快速數學函數算法框圖

算法2:使用插值函數進行正弦計算

圖20. 插值函數算法框圖

變量描述:

- testInputSin_f32指向用于正弦計算的輸入值

- testRefSinOutput32_f32指向由matlab計算得到輸出參考值p

- testOutput指向由三次插值計算得到的輸出緩沖

- testLinIntOutput指向由線性插值計算得到的輸出緩沖

- snr1參考輸出和三次插值輸出的信噪比

- snr2參考輸出和線性插值輸出的信噪比

使用到DSP軟件庫的函數有:

- arm_sin_f32()

- arm_linear_interp_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_7_arm_linear_interp_example

矩陣示例

描述:該示例展示了使用矩陣轉置、矩陣乘法和矩陣求逆函數應用于最小二乘法處理的輸入數據。最小二乘法是用于查找最佳擬合曲線,該曲線可使給定數據及的偏移平方和(最小方差)最小化。

算法:

做考慮參數的線性組合如下:The linear combination of parameters considered is as follows:A*X=B, where X is the unknown value and can be estimated from A & B.其中X表示未知值,可以根據A和B進行估算。最小二乘法估算值X由以下公式算出X=Inverse(AT*A)*AT*B

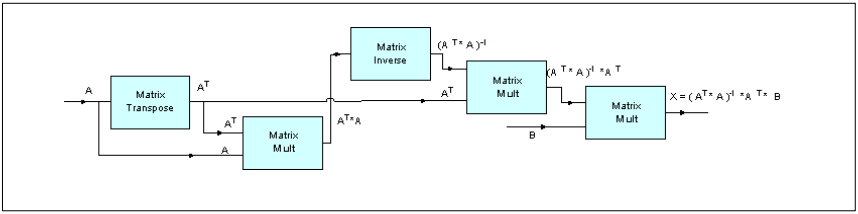

框圖:

圖21. 矩陣算法框圖

變量描述:

A_f32 input matrix:線性組合方程的輸入矩陣B_f32 output matrix:線性組合方程的輸出矩陣X_f32 unknown matrix:矩陣A_f32和B_f32估計而得到的未知矩陣

使用到DSP軟件庫的函數有:

arm_mat_init_f32()arm_mat_trans_f32()arm_mat_mult_f32()arm_mat_inverse_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_8_arm_matrix_example

信號收斂示例

描述:演示了展示了FIR低通濾波傳遞函數的自適應濾波器“學習”能力,使用到的函數有歸一化LMS濾波器,有限沖擊相應(FIR)濾波器和基本數學函數來。

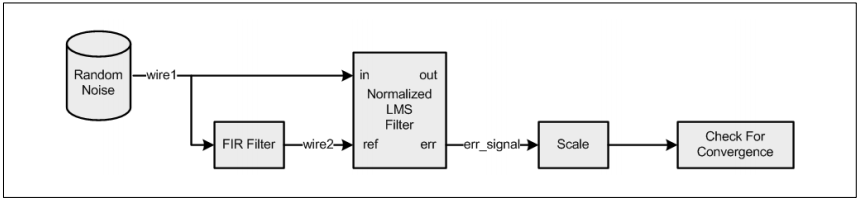

算法:

下圖說明了此示例的信號流。均勻分布的白噪聲通過FIR低通濾波器進行濾波。FIR濾波器的輸出為自適應濾波器(標準化LMS濾波器)的提供參考輸入。白噪聲是自適應濾波器的輸入。自適應濾波器學習FIR濾波器的傳遞函數。該濾波器輸出兩個信號:(1)內部自適應FIR濾波器的輸出(2)自適應濾波器與FIR的參考輸出之間的誤差信號。隨著自適應的濾波器不斷學習學習FIR濾波器的傳遞函數,第一個輸出將會接近于FIR濾波器的參考輸出,誤差信號也會不斷接近于零。即使輸入信號具有大的變化范圍(即,從小到大變化),自適應濾波器也能正確收斂。自適應濾波器的系數初始化為零,在1536個樣本上,內部函數test_signal_converge()找到停止條件。該功能檢查誤差信息的所有值是否都低于閾值DELTA的幅度。

框圖:

圖22. 信號收斂算法框圖

變量描述:

testInput_f32:指向輸入數據firStateF32:指向FIR狀態(tài)緩沖區(qū)lmsStateF32:指向歸一化最小方差FIRFIRCoeff_f32:指向系數緩沖區(qū)lmsNormCoeff_f32:指向歸一化最小方差FIR濾波器系數緩沖區(qū)wire1, wir2, wire3:臨時緩沖區(qū)errOutput, err_signal:臨時錯誤緩沖區(qū)

使用到DSP軟件庫的函數有:

arm_lms_norm_init_f32()arm_fir_init_f32()arm_fir_f32()arm_lms_norm_f32()arm_scale_f32()arm_abs_f32()arm_sub_f32()arm_min_f32()arm_copy_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_9_arm_signal_converge_example

正弦余弦示例

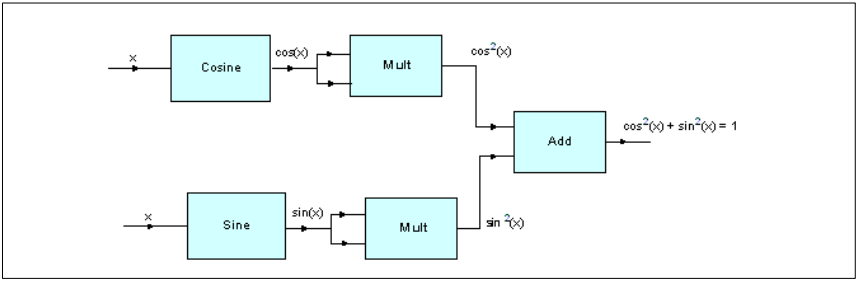

描述:Demonstrates the Pythagorean trignometric identity with the use of Cosine, Sine, Vector Multiplication, and Vector Addition functions.通過使用正弦,余弦,向量乘法和向量加法函數演示三角學的勾股定理

算法:

數學上,勾股三角學恒等式由以下方程式定義:sin(x)*sin(x)+cos(x)*cos(x)=1其中x為弧度值

框圖:

圖23. 使用正弦余弦演示勾股定理算法框圖

變量描述:

testInput_f32:以弧度為單位的角度輸入數組testOutput stores:正弦值和余弦值的平方和

使用到 DSP 軟件庫的函數有:

arm_cos_f32()arm_sin_f32()arm_mult_f32()arm_add_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_10_arm_sin_cos_example

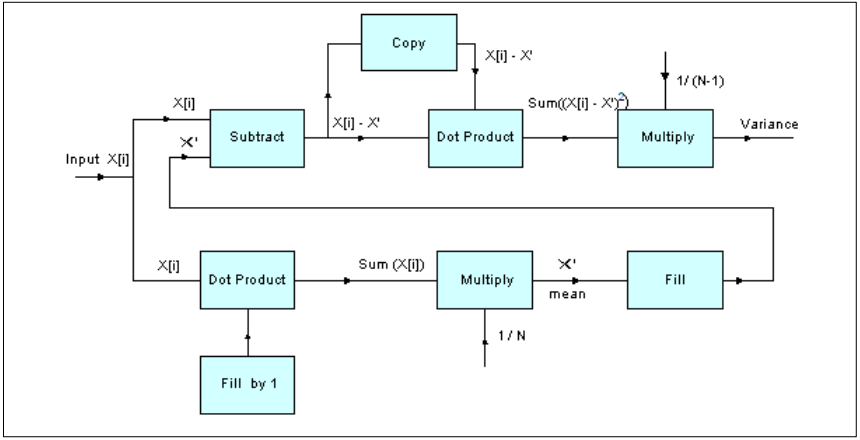

方差示例描述:演示如何使用基本函數和支持函數來計算 N 個樣本的輸入序列的方差,將均勻分布的白噪聲作為輸入。

算法:

序列的方差是各序列與序列平均值的平方差的平均值。

這有以下等式表示:

variance=((x[0]-x')*(x[0]-x')+(x[1]-x')*(x[1]-x')+...+*(x[n-1]-x')*(x[n-1]-x'))/(N-1)其中,x[n]是輸入序列,N輸入樣本數,x是輸入序列x[n]的平均值。

平均值x的定義如下:

x'=(x[0]+x[1]+...+x[n-1])/N

框圖:

圖24. 方差算法框圖

變量描述:

testInput_f32:指向輸入數據wire1, wir2, wire3 :臨時數據緩沖區(qū)blockSize:一次處理的樣本數refVarianceOut:參考方差值

使用到DSP軟件庫的函數有:

arm_dot_prod_f32()arm_mult_f32()arm_sub_f32()arm_fill_f32()arm_copy_f32()

參考

AT32_DSP_DEMO\project\at_start_f403a\examples\5_11_arm_variance_example

CMSIS NN with DSP

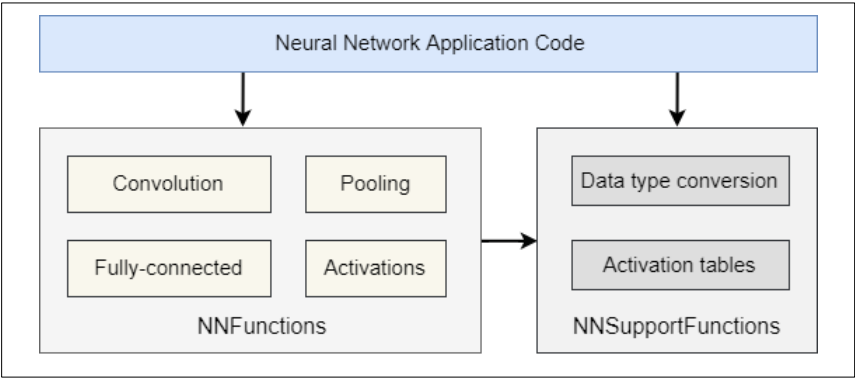

介紹本用戶手冊介紹了CMSIS NN軟件庫,這是一個有效的神經網絡內核的集合,這些內核的開發(fā)旨在最大程度地提高性能,并最大程度地減少神經網絡在Cortex-M處理器內核上的存儲空間。該庫分為多個函數,每個函數涵蓋特定類別:神經網絡卷積函數神經網絡激活功能全連接層功能神經網絡池功能Softmax函數神經網絡支持功能

該庫具有用于對不同的權重和激活數據類型進行操作的單獨函數,包括8位整數(q7_t)和16位整數(q15_t)。功能說明中包含內核的描述。本文[1]中也描述了實現(xiàn)細節(jié)。

圖25. CMSIS NN程序架構

例子

該庫附帶了許多示例,這些示例演示了如何使用庫函數。

預處理器宏

每個庫項目都有不同的預處理器宏。

ARM_MATH_DSP:

如果芯片支持DSP指令,則定義宏ARM_MATH_DSP。

ARM_MATH_BIG_ENDIAN:

定義宏ARM_MATH_BIG_ENDIAN來為大型字節(jié)序目標構建庫。默認情況下,為小端目標建立庫。

ARM_NN_TRUNCATE:

定義宏ARM_NN_TRUNCATE以使用floor而不是round-to-the-nearest-int進行計算

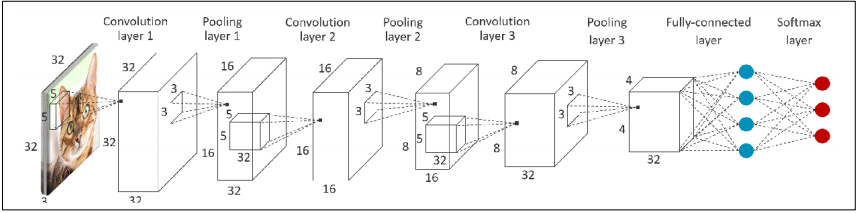

卷積神經網絡示例

描述:演示了使用卷積,ReLU激活,池化和全連接功能的卷積神經網絡(CNN)示例。

型號定義:

本示例中使用的CNN基于Caffe [1]的CIFAR-10示例。該神經網絡由3個卷積層組成,其中散布有ReLU激活層和最大池化層,最后是一個完全連接的層。網絡的輸入是32x32像素的彩色圖像,它將被分類為10個輸出類別之一。此示例模型實現(xiàn)需要32.3 KB的存儲權重,40 KB的激活權和3.1 KB的存儲im2col數據。圖26. CIFAR10 CN算法框圖

神經網絡模型定義

變量說明:conv1_wt,conv2_wt,conv3_wt是卷積層權重矩陣conv1_bias,conv2_bias,conv3_bias是卷積層偏置數組ip1_wt,ip1_bias指向完全連接的圖層權重和偏差input_data指向輸入圖像數據output_data指向分類輸出col_buffer是用于存儲im2col輸出的緩沖區(qū)scratch_buffer用于存儲激活數據(中間層輸出)

CMSIS DSP軟件庫使用的功能:

arm_convolve_HWC_q7_RGB()arm_convolve_HWC_q7_fast()arm_relu_q7()arm_maxpool_q7_HWC()arm_avepool_q7_HWC()arm_fully_connected_q7_opt()arm_fully_connected_q7()

請參閱

AT32_DSP_DEMO\project\at_start_f403a\examples\6_1_arm_nnexamples_cifar10

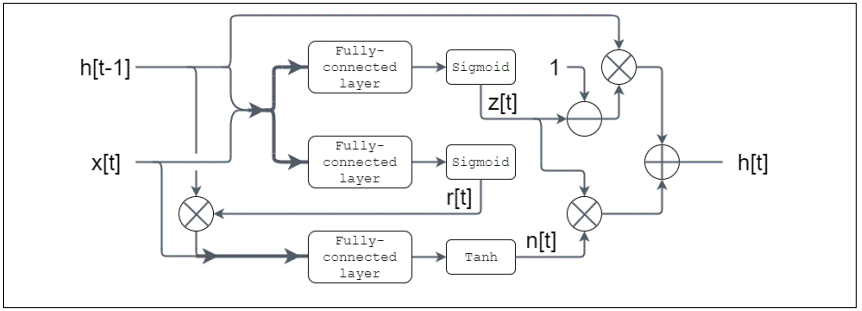

門控循環(huán)單元示例

描述:使用完全連接的 Tanh / Sigmoid 激活功能演示門控循環(huán)單元(GRU)示例。

型號定義:

GRU是一種遞歸神經網絡(RNN)。它包含兩個S型門和一個隱藏狀態(tài)。

計算可以總結為:

z[t]=Sigmoid(W_z?{h[t-1],x[t]})r[t]=sigmoid(W_r?{h[t-1],x[t]})n[t]=tanh(W_n?[r[t]×{h[t-1],x[t]})h[t]=(1-z[t])×h[t-1]+z[t]×n[t]圖27. 門極遞歸單元圖 變量說明:update_gate_weights,reset_gate_weights,hidden_state_weights 是與更新門(W_z),重置門(W_r)和隱藏狀態(tài)(W_n)對應的權重。update_gate_bias,reset_gate_bias,hidden_state_bias是圖層偏置數組test_input1,test_input2,test_history 是輸入和初始歷史記錄

變量說明:update_gate_weights,reset_gate_weights,hidden_state_weights 是與更新門(W_z),重置門(W_r)和隱藏狀態(tài)(W_n)對應的權重。update_gate_bias,reset_gate_bias,hidden_state_bias是圖層偏置數組test_input1,test_input2,test_history 是輸入和初始歷史記錄

緩沖區(qū)分配為:

|重置|輸入|歷史|更新| hidden_state |這樣,由于(復位,輸入)和(輸入,歷史記錄)在存儲器中被物理地隱含,所以自動完成隱含。權重矩陣的順序應相應調整。

CMSIS DSP 軟件庫使用的功能:

arm_fully_connected_mat_q7_vec_q15_opt()arm_nn_activations_direct_q15()arm_mult_q15()arm_offset_q15()arm_sub_q15()arm_copy_q15()

請參閱

AT32_DSP_DEMO\project\at_start_f403a\examples\6_2_arm_nnexamples_gru

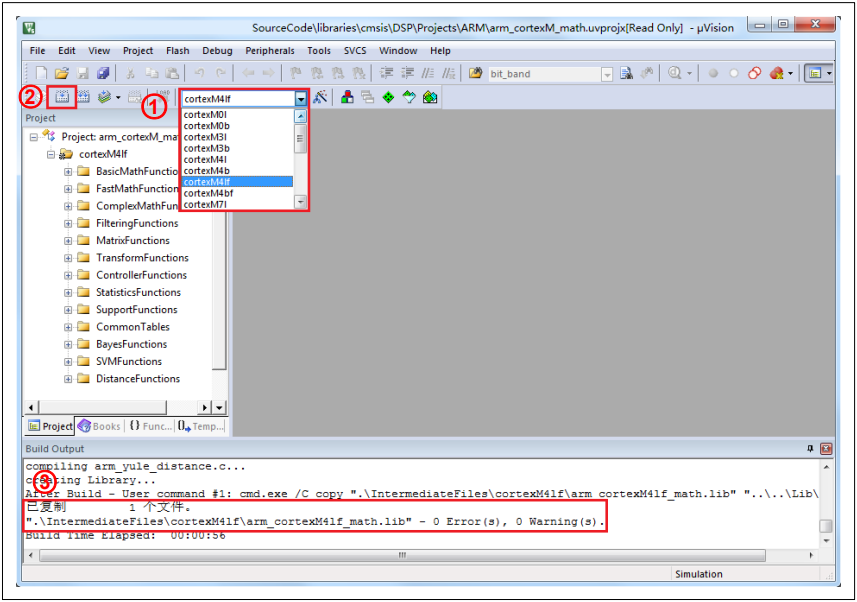

DSP Lib的生成和使用

本節(jié)主要講解如何將DSP源碼打包為不同內核MCU所使用的lib文件。在Artery所提供的DSP包中沒有包含官方所提供的lib文件,但包含了可生成lib文件的ARM、GCC、IAR三種編譯環(huán)境的工程,用戶可根據自己的需要選擇適用的lib文件來進行生成。亦可將生成的lib文件替換掉工程中的DSP源碼。下面分為兩個部分來講解lib文件的生成和使用。

DSP Lib生成

下面以ARM編譯環(huán)境為例,展示如何生成所需的lib文件:1) 打開SourceCode\libraries\cmsis\DSP\Projects\ARM中的Keil工程;2) 在①處select target下拉框選擇所需生成的lib文件;3) 點擊②處進行編譯;4) 待③處顯示lib文件生成信息;5) 在SourceCode\libraries\cmsis\DSP\Lib\ARM中查看生成的lib文件。圖28. DSP Lib生成

DSP Lib使用

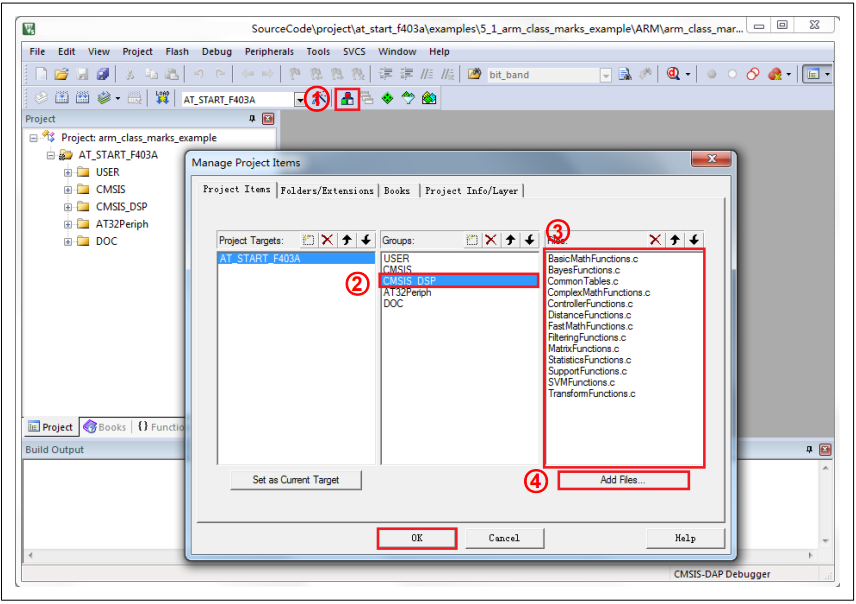

下面以5_1_arm_class_marks_example為例,展示如何使用lib文件:1) 點擊①處打開manage project items界面;2) 點擊②處,將③處內容全部刪除;3) 點擊④處找到SourceCode\libraries\cmsis\DSP\Lib\ARM路徑下的lib文件進行添加;4) 點擊OK,編譯工程。圖29. DSP Lib使用

關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創(chuàng)新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發(fā)與創(chuàng)新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業(yè)界最高主頻288MHz運算效能,并支持工業(yè)級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業(yè)縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯(lián)網、消費、商務及工控等領域。

-

mcu

+關注

關注

146文章

17167瀏覽量

351390

發(fā)布評論請先 登錄

相關推薦

STM32轉AT32代碼轉換

AT32講堂088 | 雅特力AT32F402/F405時鐘配置

雅特力AT32 MCU的隨機數生成

AT32講堂085 | 雅特力AT32 MCU HICK時鐘校準

基于MCU的神經網絡模型設計

移植CMSIS-NN v6.0.0版本到VisionBoard

AT32講堂016 | AT32 MCU DSP使用案例和網絡神經算法CMSIS-NN案例

AT32講堂016 | AT32 MCU DSP使用案例和網絡神經算法CMSIS-NN案例

評論