如圖所示,開關穩(wěn)壓電路的輸入端通常使用大電容,有助于提高電源負載功率的穩(wěn)定性。

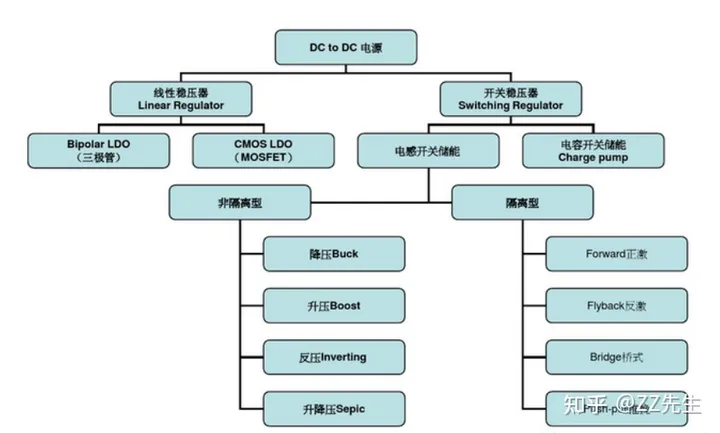

開關穩(wěn)壓電路(降壓、升壓、降壓-升壓、反激等)的最基本模型非常簡單,它們使用電感元件、隔離(在反激式轉換器的情況下)器件和用于穩(wěn)定功率輸出的電容器以及二極管等整流元件。如果您查看典型的開關穩(wěn)壓電路波形,這意味著一切都應表現出所需的、具有低開關噪聲和在連續(xù)導通模式下的

這張圖片有什么問題呢?關于開關穩(wěn)壓電路的基本模型在哪里不完整?答案在于這些電路中的瞬態(tài)行為中。

瞬態(tài)響應可以在電路的三個方面中解決:

在開關節(jié)點,這里MOSFET的引腳電感和柵極電容會導致振鈴

在本文中,我們將研究上述第 3 點,即由于轉換器中的開關動作而在輸入電源網絡中出現噪聲。事實證明,在 DC-DC 轉換器模塊中看到的行為與在高速 PCB 的 PDN 中看到的行為非常相似——在輸入電源波形上可能會發(fā)生的振蕩。這暗示了確保功率穩(wěn)定性的解決方案:更大的電容!

為什么要在電源穩(wěn)壓器上放置輸入電容?

如簡介中所述,由于需要確保功率穩(wěn)定性,因此需要在 DC-DC 轉換器的輸入端口上使用輸入電容。電容器存儲具有一定電勢能的電荷,并且當電容器端子和負載連接時,該能量可以傳遞到負載。為穩(wěn)壓電路提供輸入電壓的電源必須能夠在轉換器運行時快速響應不斷變化的電源需求,以使輸入電源總線穩(wěn)定。

電源、電源轉換器模塊和電池可能沒有足夠低的阻抗和時間常數來響應開關電路中的電流需求。即使電源輸出端存在端接電容,輸出連接和引線也會增加電源輸出阻抗的電阻。但是,有一個簡單的解決方案:添加電容!

當電源調節(jié)器具有緩慢響應(可能未調節(jié))的輸入電源時,在 PCB 上放置輸入電容可提供更快的響應。實際上,開關穩(wěn)壓器從輸入電容器汲取電力,而輸入電源模塊只是簡單地對輸入電容進行再充電。

向輸入電容器和開關電源電路供電

向輸入電容器和開關電源電路供電

添加輸入電容的影響

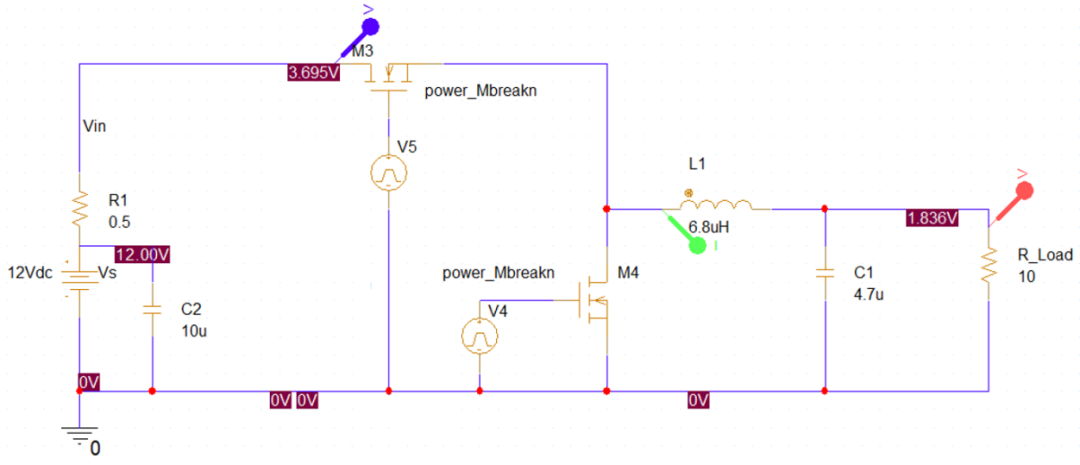

當我們查看開關期間的輸入總線電壓時,我們可以看到增加足夠輸入電容的重要性。考慮如下所示的降壓轉換器設計。在此穩(wěn)壓器中,我們假設輸入的 12 V 電源在輸出上有一些電容(10 uF,C2),但連接器、引線、PCB 上的端子以及制造缺陷會導致在輸出端子上存在額外的 500 mOhms 電阻(R1)。

示例:降壓轉換器設計,其輸出阻抗使用電阻器和電容器建模。

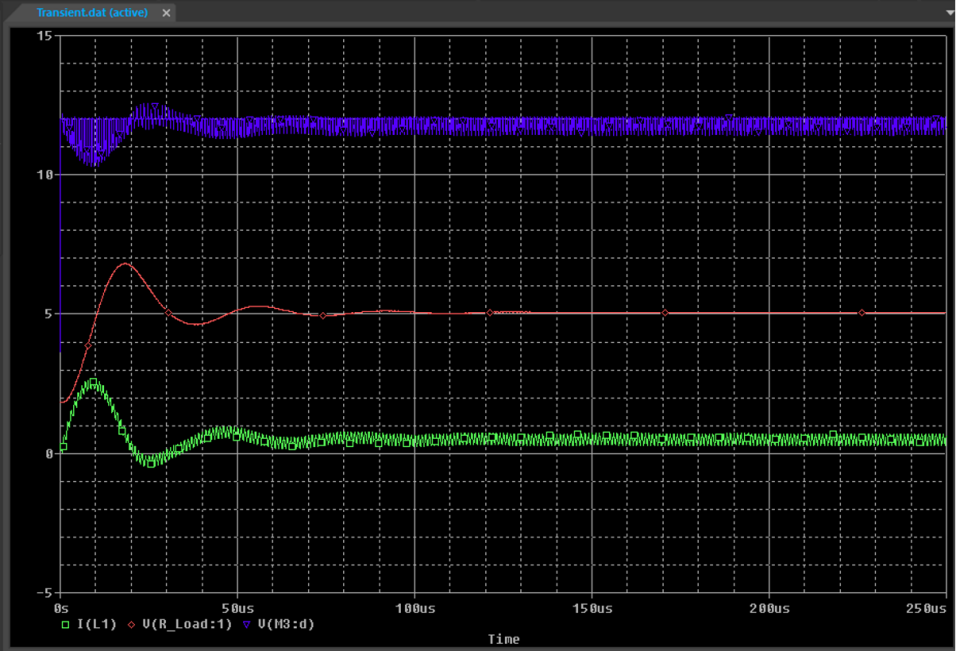

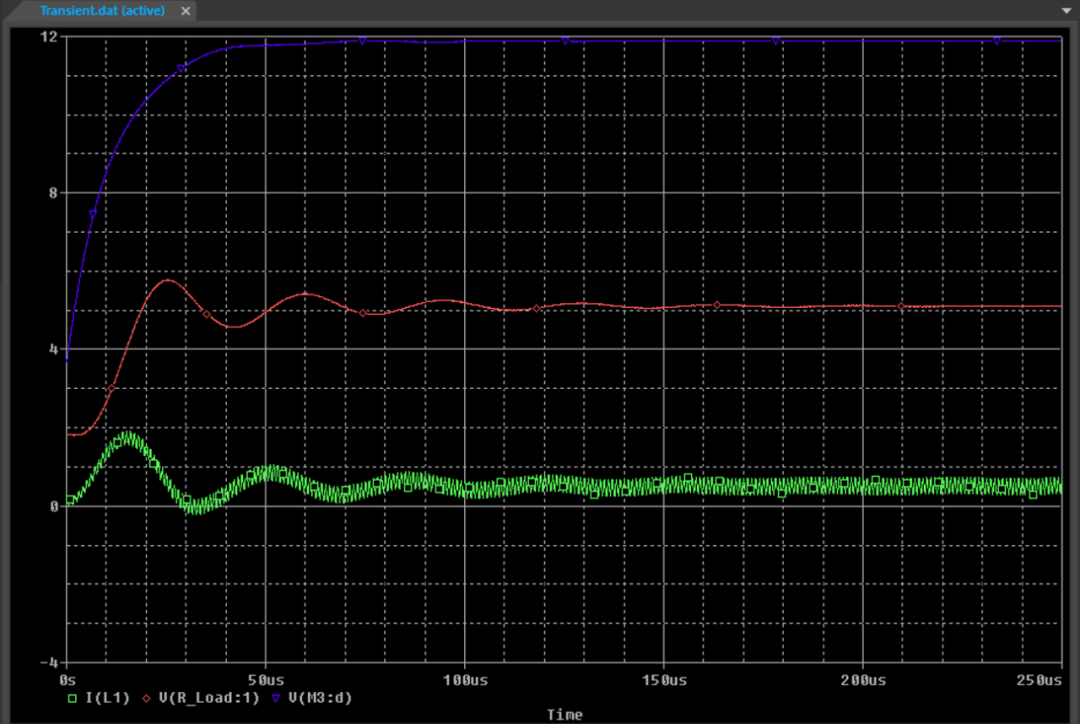

如果我們查看該電路的 PSPICE 仿真結果,我們會看到下圖。從電感電流(綠色)、輸入電壓(藍色)和輸出電壓(紅色)來看,瞬態(tài)響應非常大。在這些圖中可以看到 500 mV 的大過沖和輸入功率變化。

上述降壓轉換器設計示例的 PSPICE 結果

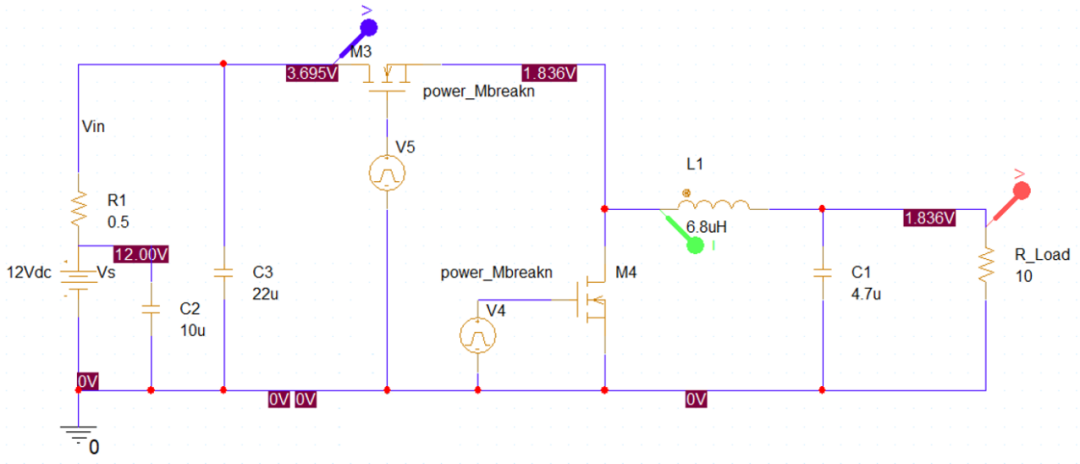

現在讓我們看看如果我們在高側 MOSFET 和 GND 的輸入端增加一些電容 (22 uF) 會發(fā)生什么。這不是一個巨大的輸入電容,但它確實為電源穩(wěn)定性提供了很多好處,我們將在下面一一說明。(在 PCB 上,該電容器應放置在非常靠近 MOSFET 端子的位置。)

帶有輸入電容器的改進型開關穩(wěn)壓電路

帶有輸入電容器的改進型開關穩(wěn)壓電路

下面的瞬態(tài)分析結果很好地表明輸入上的瞬態(tài)響應是穩(wěn)定的。這是由輸入電容器 C3 的濾波作用提供的。該電路仍有一定的開啟時間余量,但開啟時間仍然相當快,為 0.5-1 ms。

使用修改后的開關穩(wěn)壓器的瞬態(tài)分析結果

添加C3后,對電感中的開關電流和輸出電壓有一些影響,但我們可以接受電感瞬態(tài)響應略微增加,以換取極高的功率穩(wěn)定性。您可以在此電路中添加其他的設計決策以提高電路的穩(wěn)定性:

在低側 MOSFET 端子上應用緩沖器,以抑制 PWM 波形和開關節(jié)點電壓上的任何振鈴

對輸出電容器 C1 施加一個非常小的串聯電阻,以稍微抑制其瞬態(tài)響應

應用另一個經過精心設計的輸出濾波器級,以防止在穩(wěn)壓器的傳遞函數中產生新的極點

要準確確定您需要多大的電容,您可以使用與去耦電容器大小時間的相同思路:確定在1個時間常數內需要提供的電荷或電流量,并計算給定施加電壓(在上面的示例中為12 V)的電容。。

電源穩(wěn)定性策略總結

當您開始深入挖掘時,任何開關穩(wěn)壓器電路都將是一個相對復雜的電路,需要大量分析才能正確設計。輸出瞬態(tài)過沖和開關噪聲的問題是互相關聯的,因此需要多種策略來設計能夠提供所需穩(wěn)定性和降噪的電路和PCB布局。下表顯示了一組用于處理 DC-DC 轉換器中各種噪聲源的策略。

| 電源穩(wěn)定性和噪聲問題 | 解決方案 |

| MOSFET開關時振鈴 | 使用體積更小的MOSFET 布線時確保足夠小的引腳/走線電感 在整流元件上使用緩沖器 |

| 輸入電壓振蕩和電壓下降 | 在輸入端使用電容器 布線時,輸入級在PCB上使用小環(huán)路電感 在輸出端使用足夠大的電容 |

| 輸出瞬態(tài)振蕩 | 在輸出端使用足夠大的電容器 在輸出端使用受控ESR電容 添加低通RLC輸出濾波器(串聯RC是分流元件) |

| 輸出開關噪聲 | 使用足夠大的電感器 在輸出端使用足夠大的電容器 使用更高的開關頻率 |

隨著電流需求的增加,DC-DC 轉換器會變得更加復雜,而增加的復雜性帶來了更多在電路的各個點產生噪聲和瞬態(tài)過沖的機會。這就需要進行徹底的電路仿真來識別這些電路的敏感區(qū)域(關鍵部分)。一旦您確定了開關穩(wěn)壓器的易受噪聲影響的部分,請確保您設計了PCB疊層和布線,以確保控制寄生效應,從而不會在設計中引入新的噪聲。

總結

當您準備仿真 DC-DC 轉換器電路并且需要確定輸入電容要求時,Cadence的PSpice是業(yè)界中的最佳電路設計和仿真工具。PSpice 用戶可以訪問強大的 SPICE 模擬器以及專業(yè)設計功能,如模型創(chuàng)建、圖形和分析工具等等。如果您想了解更多產品信息,請關注我們,歡迎您的留言。

-

DC

+關注

關注

9文章

3654瀏覽量

679807

發(fā)布評論請先 登錄

相關推薦

快速輸入轉換速率應用中DC-DC轉換器的設計注意事項

DC-DC Boost電路外圍元器件如何選擇?

DC-DC轉換器控制電路大約多少錢?

基于通用門控振蕩器的DC-DC升壓轉換器LM2623數據表

技術資訊 | 如何使用輸入電容防止 DC-DC 轉換電路振蕩

技術資訊 | 如何使用輸入電容防止 DC-DC 轉換電路振蕩

評論