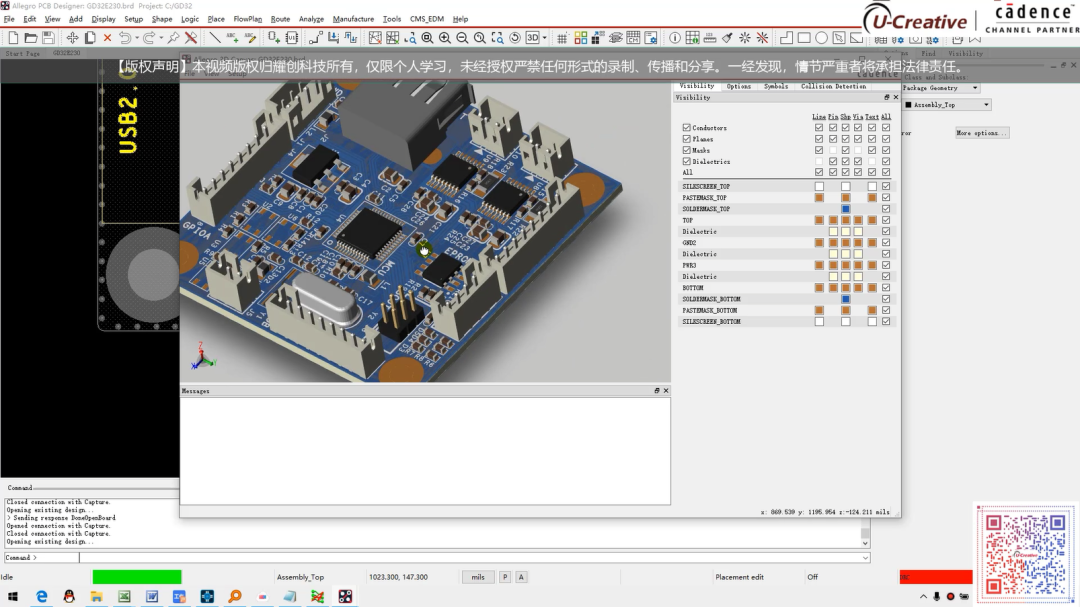

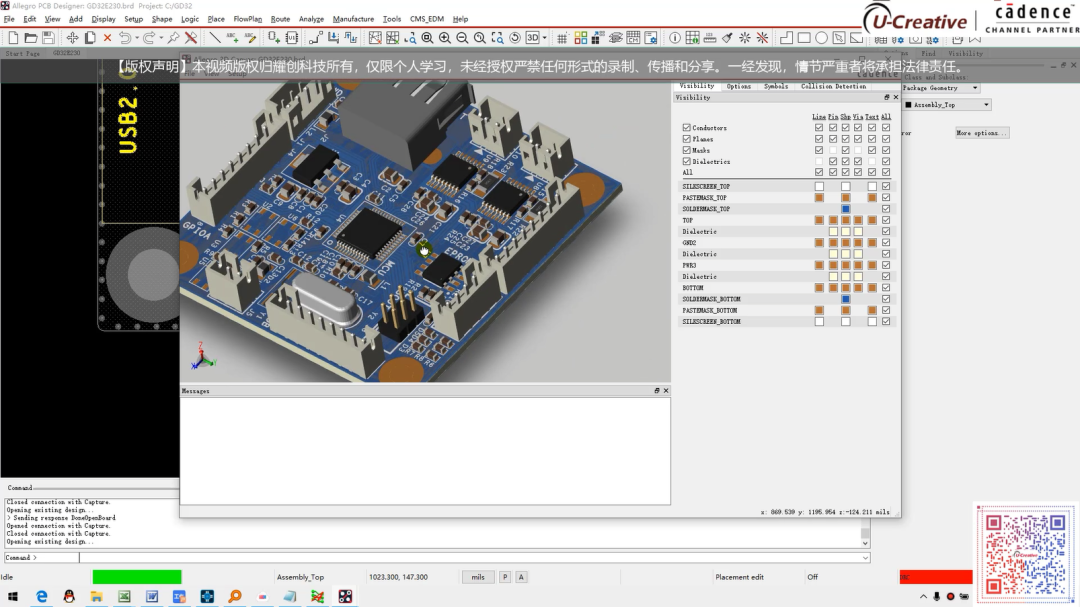

本系列課程采用了 GD32E230 芯片為核心的硬件設(shè)計(jì)基礎(chǔ),以 Cadence Allegro SPB 17.4 版本為設(shè)計(jì)工具,涵蓋了從原理圖的設(shè)計(jì)構(gòu)思開始,到錯(cuò)誤檢查、網(wǎng)絡(luò)表生產(chǎn)、封裝庫(kù)制作;同步進(jìn)入 PCB、3D 模型制作、布局、規(guī)則、布線、文件輸出等全流程經(jīng)典操作。

? ?

?

點(diǎn)擊圖片或在微信后臺(tái)回復(fù)關(guān)鍵詞“GD32”,了解完整課程詳情!

1

第五期:電路原理圖優(yōu)化 DRC

排除的辦法及從原理圖到

PCB 技巧講解

點(diǎn)

擊

文末閱讀原文,開始上課~

第五期課程全長(zhǎng)1.5小時(shí),主要進(jìn)行封裝制作并講解其相關(guān)方法。

2

課程進(jìn)度

章節(jié) | 內(nèi)容 |

1 | GD32 芯片手冊(cè)精讀及常用的芯片外圍配置電路分析 |

2 | 使用 OrCAD Capture 17.4 軟件進(jìn)行 GD32 項(xiàng)目原理圖設(shè)計(jì)的技巧及設(shè)計(jì)辦法 |

3 | 外圍常用電路的原理分析計(jì)算優(yōu)化與原理圖用用接口設(shè)計(jì)技巧 |

4 | 外圍常用電路的原理分析計(jì)算優(yōu)化與原理圖設(shè)計(jì)技巧總結(jié) |

5 | 電路原理圖優(yōu)化 DRC 排除的辦法及從原理圖到 PCB 技巧講解(本期內(nèi)容) |

6 | GD32 小車項(xiàng)目液晶電路的控制技巧與 PCB 的布局布線同步的操作技巧與常用功能總結(jié) |

7 | GD32 PCB 延遲調(diào)整規(guī)則及布線繞線的命令與光繪輸出的相關(guān)操作總計(jì) |

8 | GD32 PCB 設(shè)計(jì)中快捷鍵的設(shè)置方法及 PCB 預(yù)處理標(biāo)注的技巧與布局的技巧總結(jié) |

9 | GD32 PCB 設(shè)計(jì)中布局的操作技巧布局優(yōu)化的辦法三維模型的檢查設(shè)計(jì) |

10 | GD32 PCB 規(guī)則的設(shè)置及模塊布線的技巧內(nèi)電層的處理技巧及絲印的設(shè)置技巧 |

11 | GD32 PCB 的后處理及批量的處理方法光繪的設(shè)置及輸出技巧項(xiàng)目歸類及總結(jié) |

本直播課程系列使用 Allegro SPB 17.4 最新版本,如果想要達(dá)到最佳邊學(xué)邊練效果,建議立刻申請(qǐng)免費(fèi)升級(jí)哦!

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

相關(guān)推薦

FCore2S硬件原理圖_E6

發(fā)表于 01-24 09:56

?0次下載

全志H3_V1.0_原理圖

發(fā)表于 01-21 15:35

?3次下載

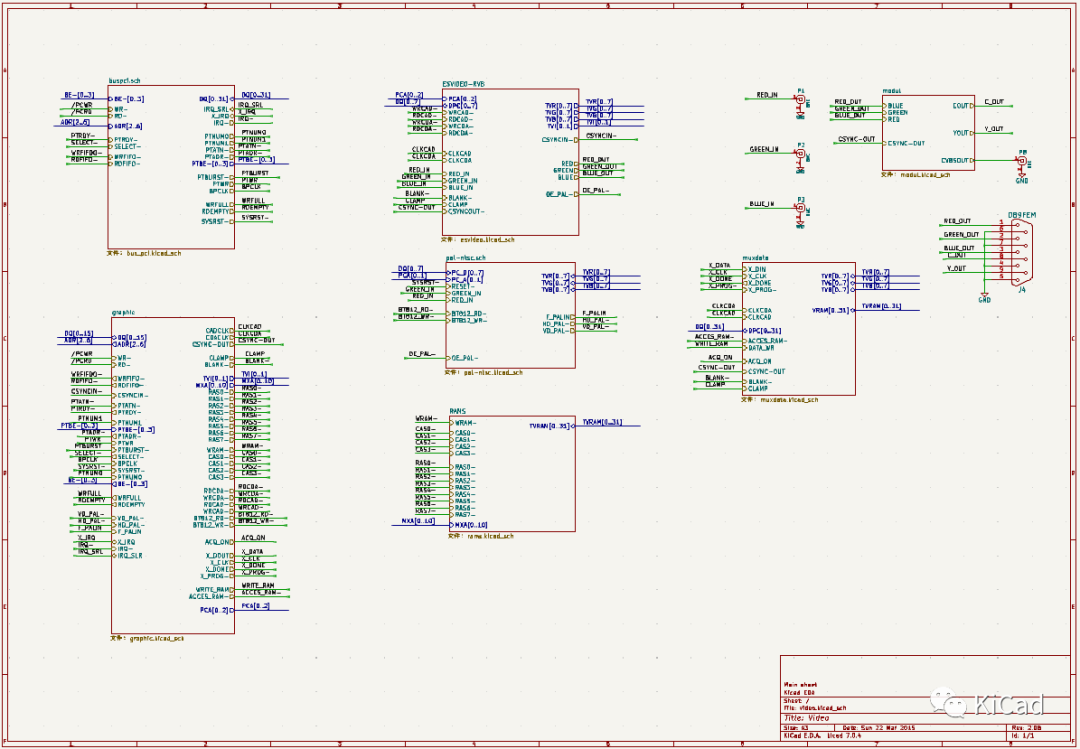

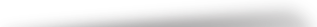

繪制成層次設(shè)計(jì),可以提高原理圖的可讀性,減少重復(fù)繪制。 創(chuàng)建層次原理圖是從根原理圖開始的。其過(guò)程是創(chuàng)建一個(gè)子原理圖,然后在子

![的頭像]() 發(fā)表于

發(fā)表于 11-13 18:06

?1285次閱讀

包括原理圖設(shè)計(jì)所需的所有工具。從 KiCad 包含的符號(hào)庫(kù)中放置符號(hào),繪制導(dǎo)線連接并將原理圖同步到 PCB 中進(jìn)行布局布線。 電氣規(guī)則檢查

![的頭像]() 發(fā)表于

發(fā)表于 11-12 12:23

?408次閱讀

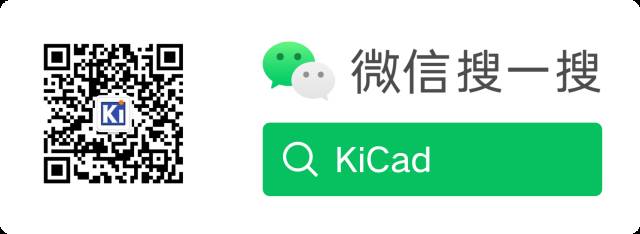

“ ?KiCad可以支持直接導(dǎo)入Altium Designer的原理圖及PCB文件。與其它導(dǎo)入器不同,KiCad導(dǎo)入器可以直接導(dǎo)入源生的二進(jìn)制文件(*.schdoc及*.pcbdoc),而不需要像

![的頭像]() 發(fā)表于

發(fā)表于 11-12 12:21

?1534次閱讀

。以下是實(shí)現(xiàn)原理圖與PCB元件對(duì)應(yīng)的主要步驟: 1. 創(chuàng)建項(xiàng)目和文件 首先,在AD中創(chuàng)建一個(gè)新項(xiàng)目,并分別添加原理圖文件和PCB文件到該項(xiàng)目

![的頭像]() 發(fā)表于

發(fā)表于 09-02 17:25

?4597次閱讀

在Altium Designer 20(簡(jiǎn)稱AD20)中,原理圖和PCB之間的交互是設(shè)計(jì)流程中的一個(gè)重要環(huán)節(jié),它允許設(shè)計(jì)師在邏輯設(shè)計(jì)和物理實(shí)現(xiàn)之間自由切換,確保設(shè)計(jì)的準(zhǔn)確性和一致性。以下是AD20

![的頭像]() 發(fā)表于

發(fā)表于 09-02 17:19

?3255次閱讀

在Altium Designer(簡(jiǎn)稱AD)中,將原理圖和PCB相關(guān)聯(lián)是一個(gè)重要的設(shè)計(jì)步驟,它確保了從邏輯設(shè)計(jì)到物理實(shí)現(xiàn)的順利過(guò)渡。以下是實(shí)現(xiàn)原理圖

![的頭像]() 發(fā)表于

發(fā)表于 09-02 16:34

?8091次閱讀

在Altium Designer(簡(jiǎn)稱AD)中,將畫完的原理圖導(dǎo)入到PCB(Printed Circuit Board,印制電路板)是一個(gè)關(guān)鍵的設(shè)計(jì)步驟。以下是導(dǎo)入過(guò)程: 一、準(zhǔn)備階段

![的頭像]() 發(fā)表于

發(fā)表于 09-02 16:32

?8738次閱讀

在Altium Designer中,將原理圖導(dǎo)入到PCB設(shè)計(jì)是一個(gè)關(guān)鍵的步驟,它確保了電路設(shè)計(jì)的準(zhǔn)確性和可制造性。這個(gè)過(guò)程涉及到多個(gè)階段,包

![的頭像]() 發(fā)表于

發(fā)表于 09-02 16:27

?2369次閱讀

在Altium Designer中,將原理圖轉(zhuǎn)換為PCB(Printed Circuit Board,印制電路板)圖是一個(gè)關(guān)鍵的設(shè)計(jì)步驟。以下是將原

![的頭像]() 發(fā)表于

發(fā)表于 09-02 16:20

?3044次閱讀

我們一、原理圖繪制及檢查流程階段流程原理圖繪制根據(jù)已有原理圖或資料(數(shù)據(jù)手冊(cè)、方案書)繪制原理圖

![的頭像]() 發(fā)表于

發(fā)表于 07-24 08:11

?1200次閱讀

流程,功能設(shè)計(jì)更智能化,界面操作更人性化,讓硬件工程師使用得更愉悅、順暢。為昕科技旨在通過(guò)新技術(shù)提高硬件工程師設(shè)計(jì)原理圖的效率,加速完善國(guó)產(chǎn)EDA布局,面向電子系統(tǒng)/產(chǎn)品研發(fā)

發(fā)表于 07-22 17:07

電路原理圖和電路仿真圖是電子工程領(lǐng)域中兩種常見的圖形表示方法,用于描述電子電路的結(jié)構(gòu)和工作原理。雖然二者在某些方面有所不同,但它們也有密切的

![的頭像]() 發(fā)表于

發(fā)表于 04-21 10:17

?6700次閱讀

為昕原理圖設(shè)計(jì)EDA軟件(Jupiter)是一款符合中國(guó)國(guó)情的原理圖設(shè)計(jì)軟件,聚焦核心功能,覆蓋原理圖設(shè)計(jì)全流程,功能設(shè)計(jì)更智能化,界面操作

發(fā)表于 04-12 14:30

?

?

GD32 ARM 設(shè)計(jì)硬件全流程 I 第五期:電路原理圖優(yōu)化 DRC 排除的辦法及從原理圖到 PCB 技巧講解

GD32 ARM 設(shè)計(jì)硬件全流程 I 第五期:電路原理圖優(yōu)化 DRC 排除的辦法及從原理圖到 PCB 技巧講解

評(píng)論