Allegro和 Sigrity 軟件最新發(fā)布了一系列的產(chǎn)品更新(SPB17.4 QIR4 release)。我們將通過實例講解、視頻演示讓您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期內(nèi)容)、Sigrity Aurora、Sigrity SystemSI、Sigrity SystemPI(本期內(nèi)容)等產(chǎn)品的新功能及用法,助力提升設(shè)計質(zhì)量和設(shè)計效率。

隨著現(xiàn)代高速信號的速率越來越快,信號邊沿越來越陡,芯片的供電電壓進一步降低,時鐘頻率和數(shù)據(jù)讀取速率的增加需要消耗更多的電能。在進行電子系統(tǒng)信號完整性分析研究的同時,如何提供穩(wěn)定可靠的電源給電子系統(tǒng)也已成為重點研究方向之一。

Sigrity SystemPI 是一款系統(tǒng)級的電源完整性仿真工具,能提供直流電壓降分析和電源時域噪聲與電源PDN 阻抗分析,同時也能支持電源完整性分析的流程定制。Sigrity SystemPI 主要應(yīng)用于直流和交流電源完整性問題中,能為IC 封裝、互連電纜、PCB、連接器等系統(tǒng)互連電源完整性問題提供解決方法。幫助工程師在不增加項目額外成本,不影響項目進度的前提下,實現(xiàn)項目的設(shè)計改進與性能提升。

四大功能優(yōu)勢如下:

#1

Sigrity SystemPI 中建立了通用拓撲和標(biāo)準(zhǔn)接口,允許其與 Cadence Celsius Thermal Solver 集成 Sigrity Advanced PTI 從通用拓撲互連環(huán)境中執(zhí)行自動分析并且同步到電源完整性分析中去。

高度靈活的拓撲環(huán)境能夠支持從發(fā)送電壓源到接收電流源的所有組件的電源完整性分析及電熱混合仿真分析。拓撲接口的靈活性允許進行早期分析,和執(zhí)行假設(shè)分析,幫助推動跨多結(jié)構(gòu)電源分配網(wǎng)絡(luò) PDN 的性能規(guī)范分析。隨著設(shè)計工作的進行,可以交換替代提取的 PDN 模型,以拓展出設(shè)計中的更多細節(jié)。

#2

允許使用從 Sigrity PowerSI 和 Cadence Clarity 3D Solver 中提取 Z 參數(shù)模型用于 PDN 分析,也能夠兼容其他互連建模工具及 3D 求解器的 Z 參數(shù)建模結(jié)果,能夠支持 Cadence Voltus 創(chuàng)建的仿真模型,進而支持實現(xiàn) IC 芯片的電源完整性解決方案。

#3

通過模塊化的設(shè)計思路,Sigrity SystemPI 可以快速搭建出電源完整性仿真的原理圖模塊電路,可視化仿真和模擬整個 PDN,包括 VRM、PCB、封裝、連接器及 S 參數(shù)模型,提供一站式 PDN 分析結(jié)果。

#4

在同一環(huán)境中進行 IR 直流電壓降分析、電壓紋波噪聲分析、電源 PDN 阻抗分析。

Sigrity SystemPI

系統(tǒng)電源仿真亮點——

2#允許自定義搭建鏈路進行系統(tǒng)級PDN和電源紋波分析

接下來使用一個實例來講解使用 Sigrty SystemPI 搭建鏈路進行系統(tǒng)級 PDN 和電源紋波分析的方法。

實例講解 · 圖文版

1

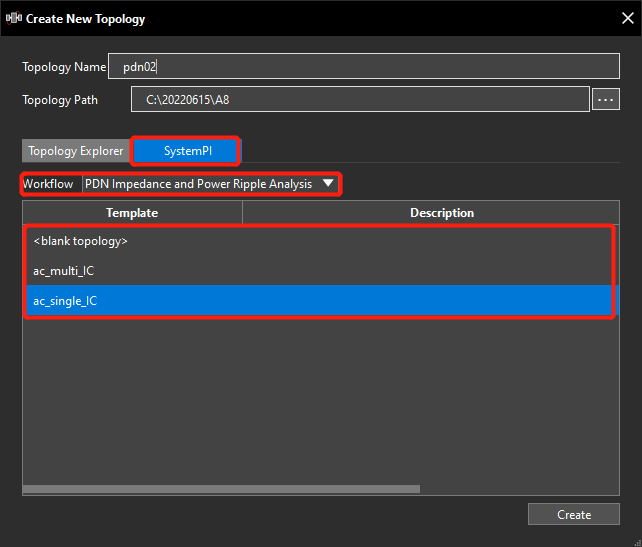

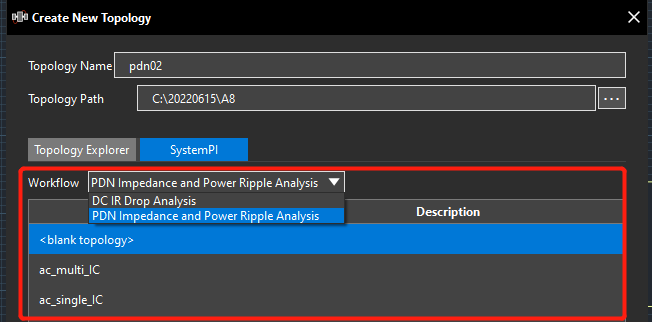

先,選擇 PDN Impedance and Power Ripple Analysis 進入PDN 和電源紋波分析模式,選擇 blank Topology 空白拓撲,ac_multi_IC 內(nèi)置的交流多路分析模板,ac_single_IC 內(nèi)置的交流單路分析模板。

2

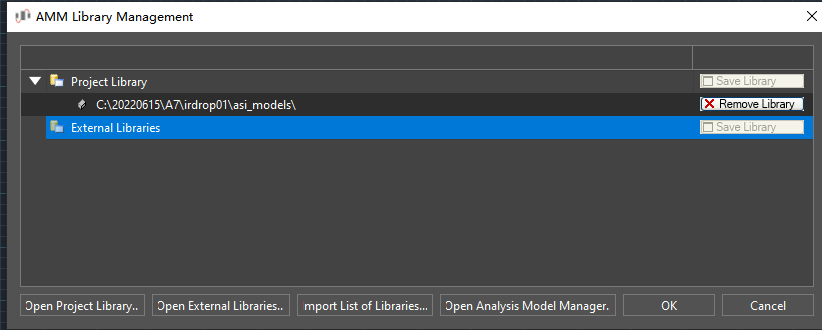

Component Model Setup 設(shè)置元件模型配置,Manage Libraries 用來配置和管理模型的庫,允許支持對本地項目庫的設(shè)置和編輯管理,也允許調(diào)用 AMM 外部系統(tǒng)庫。能導(dǎo)入 AMM 外部庫,導(dǎo)入庫的清單,打開和管理分析庫文件等。

3

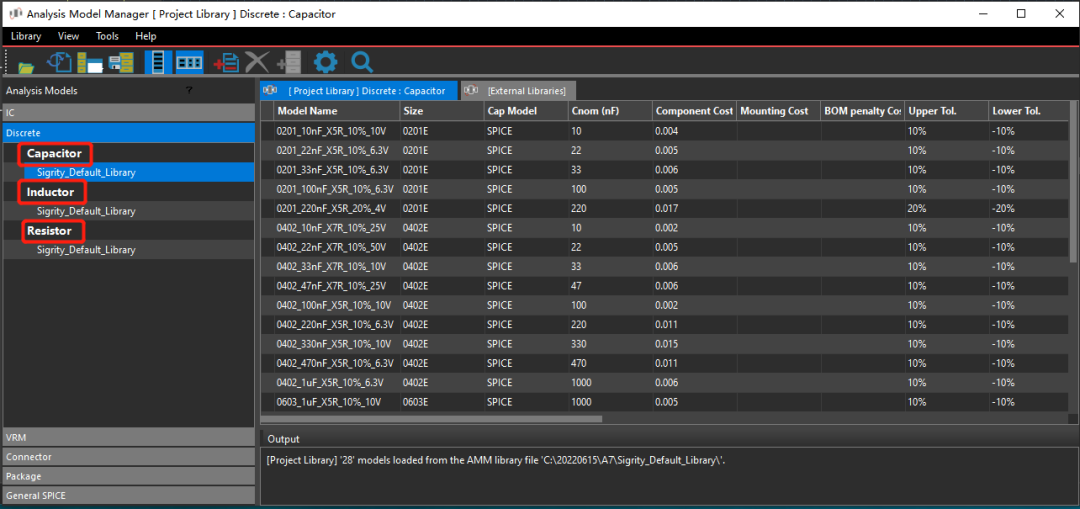

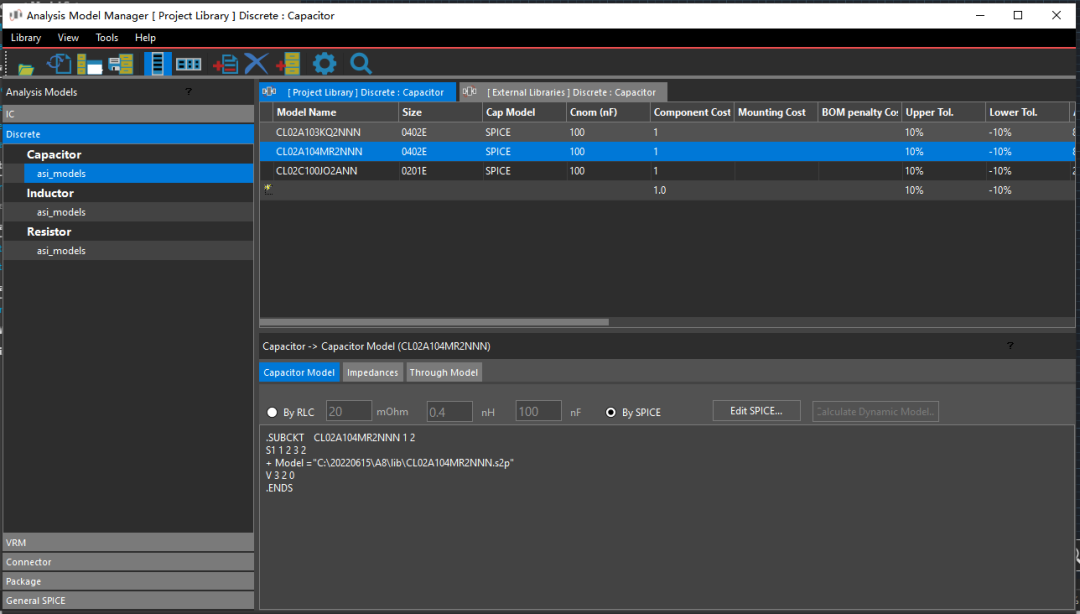

Launch Analysis Model Manager 用來啟動元件的模型管理器,在模型管理器窗口中,能夠?qū)椖繋旌屯獠康膸煳募M行查閱、編輯、刪除、修改等管理。并且可以分析模型庫中元件的參數(shù),包括電容、電阻,電感、VRM、連接器、封裝、SPICE模型等。

4

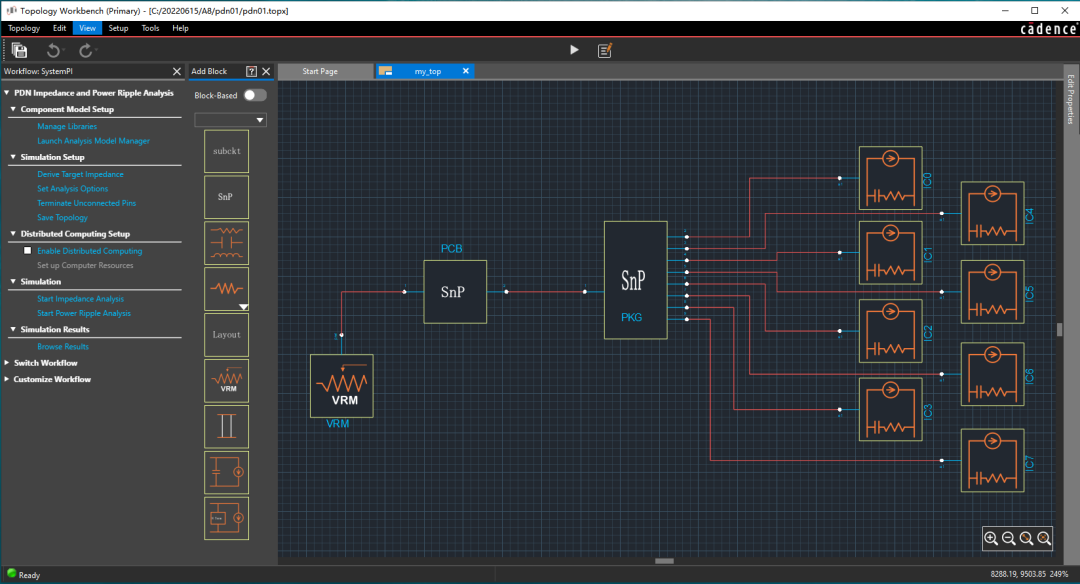

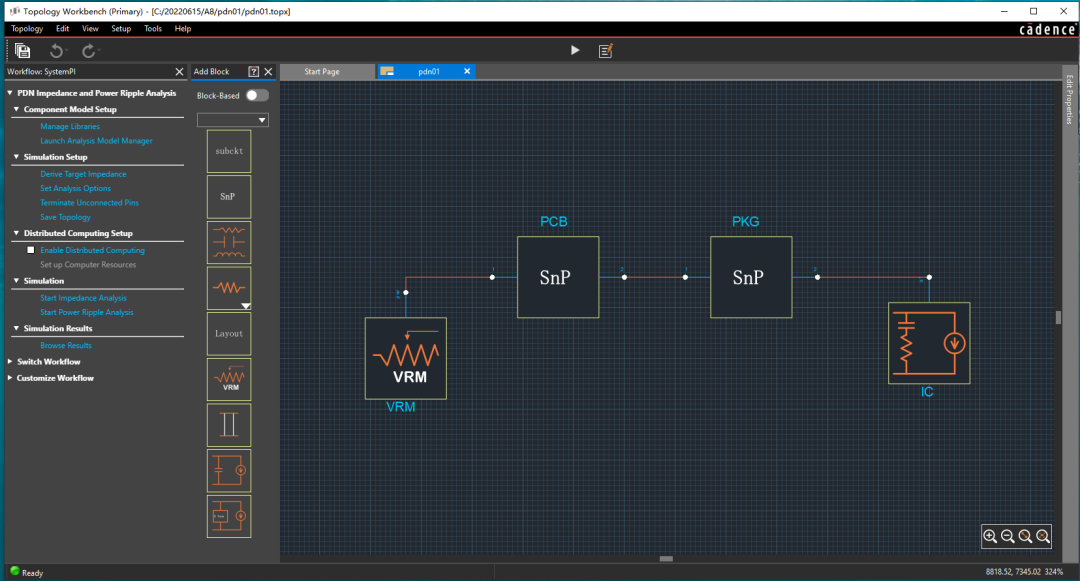

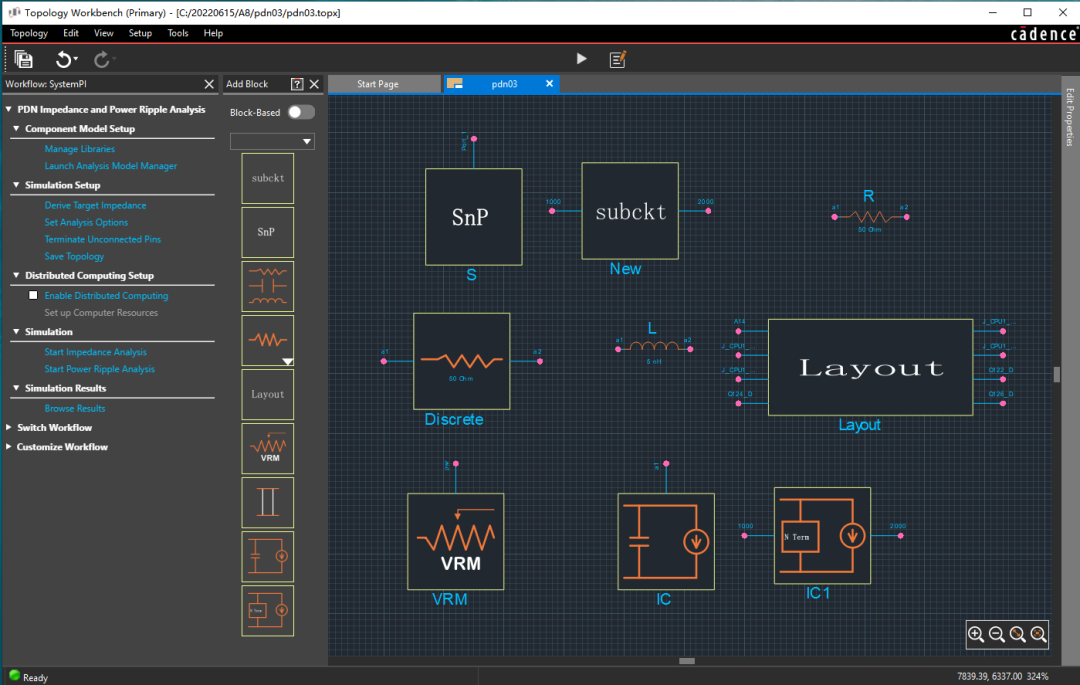

使用 Block 模塊可以搭建仿真的互連鏈路,也可以按照需要仿真的互連來搭建仿真模塊原理圖。

5

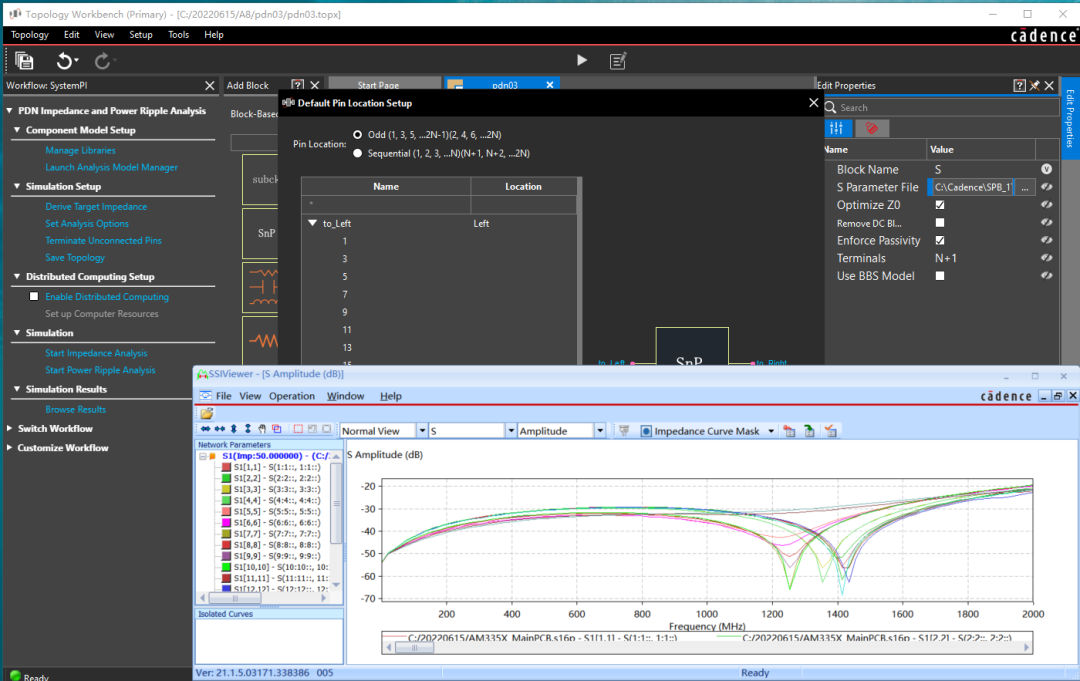

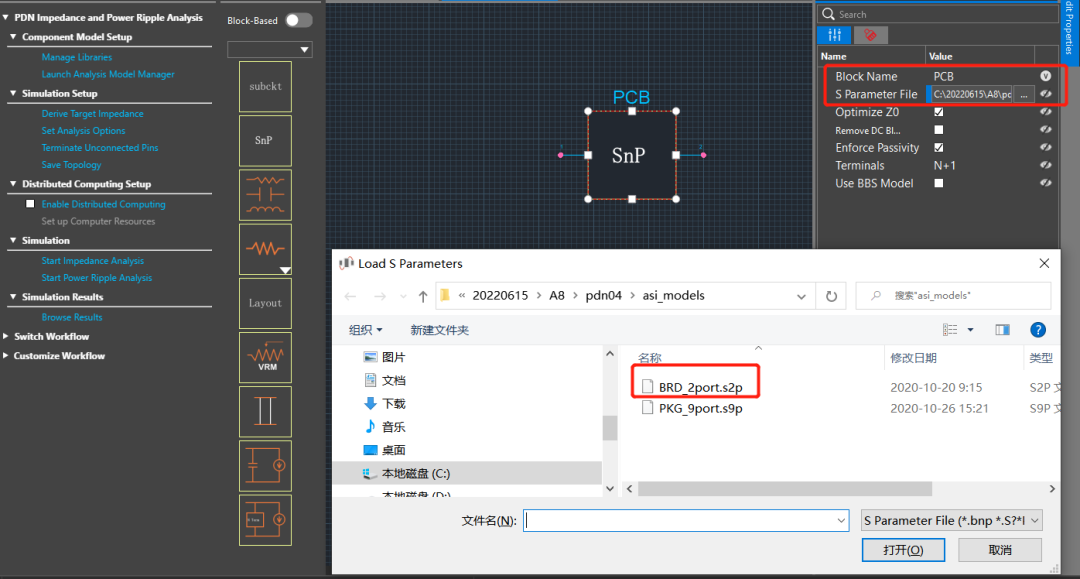

選項 SnP 的 Block 在屬性里面可導(dǎo)入 S參數(shù)。設(shè)置端口后導(dǎo)入的 S參數(shù) 就會以 Block 模塊的方式顯示出來,S參數(shù)的端口會按照設(shè)置好的方式進行排列。

6

選項 SnP 的 Block 在屬性里面可以導(dǎo)入 PCB 的參數(shù)。

7

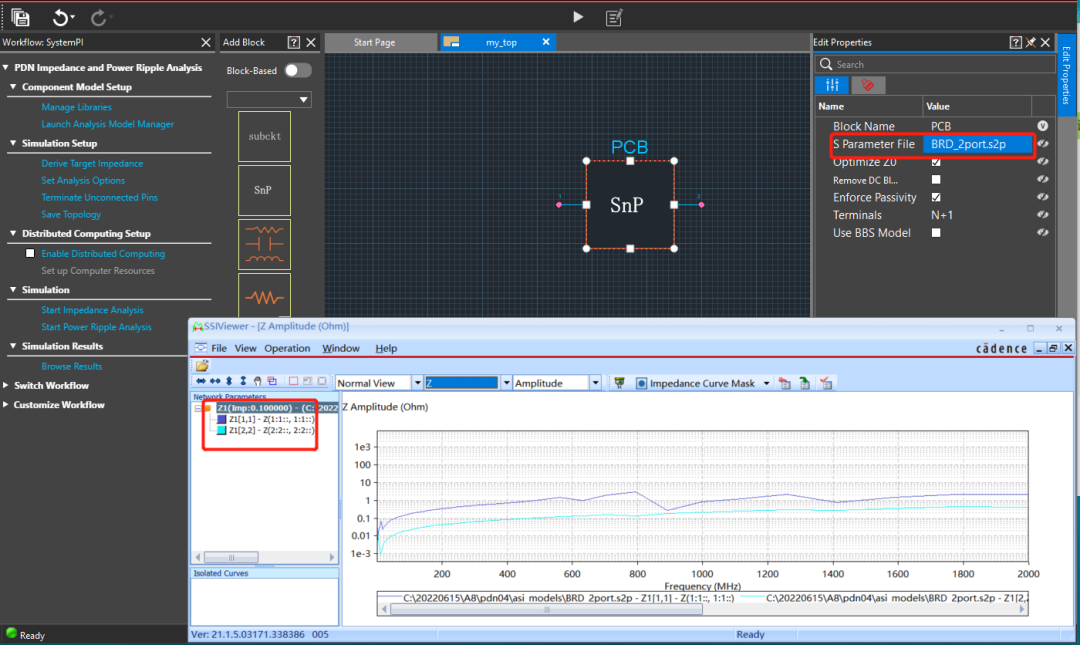

選項 SnP 的 Block 在屬性里面可導(dǎo)入 PCB 的參數(shù)。可以顯示 PCB 電源網(wǎng)絡(luò) Z 阻抗曲線,可以對阻抗進行檢查和參數(shù)分析。

8

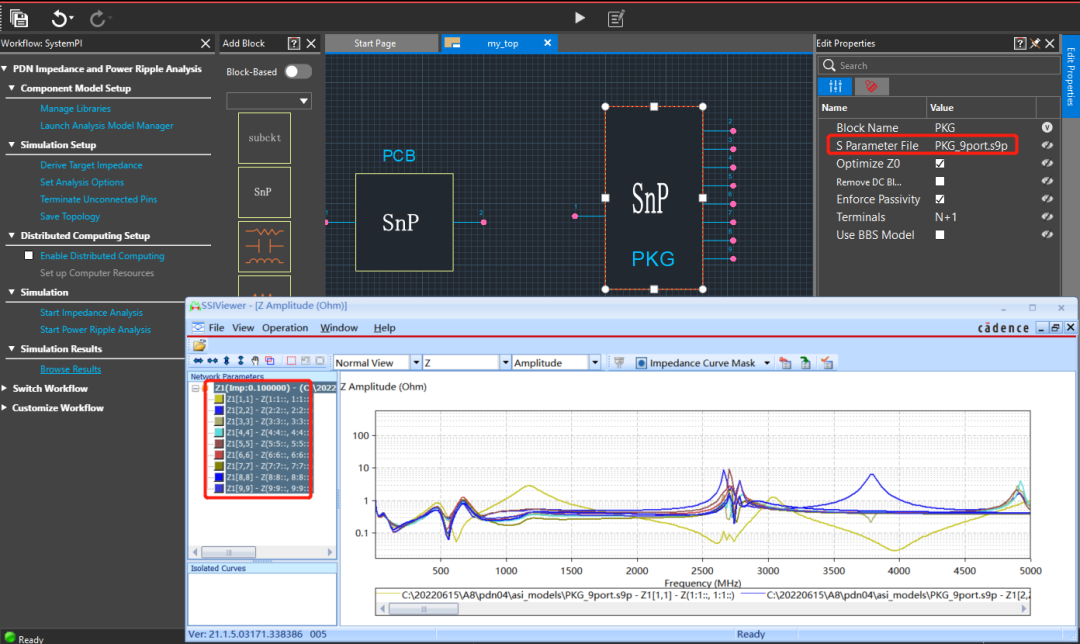

選項 SnP 的 Block 在屬性里面也可以帶入封裝 PKG 的參數(shù)。顯示封裝電源網(wǎng)絡(luò) Z 阻抗曲線,可以對阻抗進行檢查和參數(shù)分析。

9

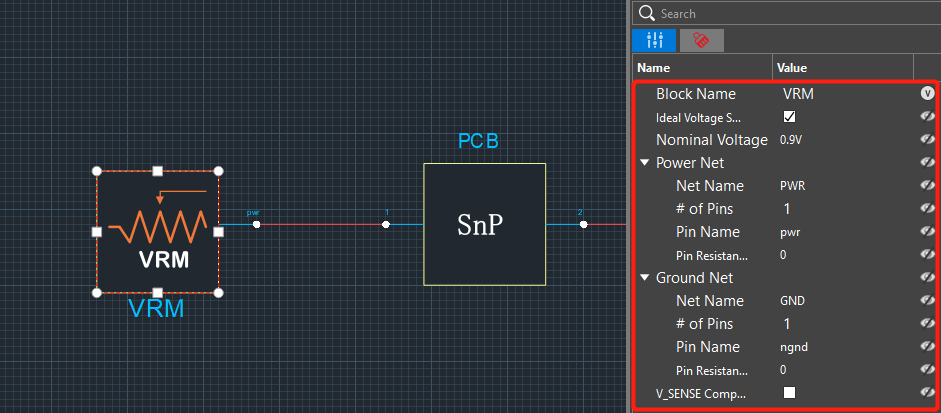

添加電壓源 VRM 模型,VRM 電壓源模型支持對名稱、電源的 PIN 網(wǎng)絡(luò)名稱、PIN 的數(shù)量、PIN 寄生電阻進行修改。Ground Net 是 GND 網(wǎng)絡(luò),支持 GND 網(wǎng)絡(luò)名稱修改、GND 的 PIN 數(shù)量、GND PIN的名稱、寄生電阻進行設(shè)置修改。點擊端口可以拉出連接線關(guān)聯(lián)到 SnP 與 S 參數(shù)形成互連鏈路。

10

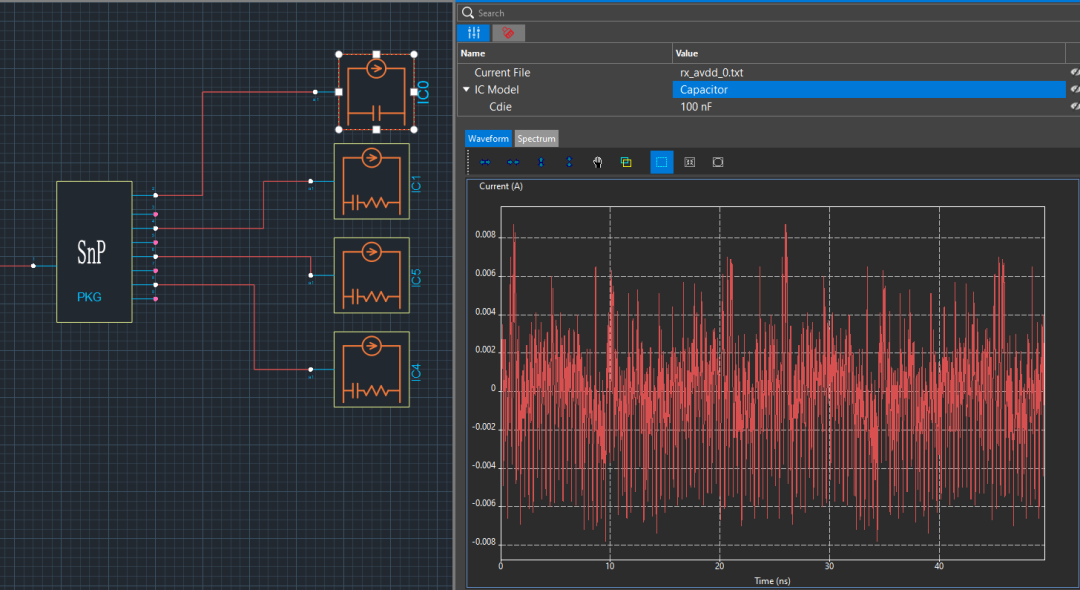

添加 IC 模型,擺放 IC 模型到合適的位置后點擊端口可以拉出連接線關(guān)聯(lián)到 SnP 與 S參數(shù) 形成互連鏈路。

11

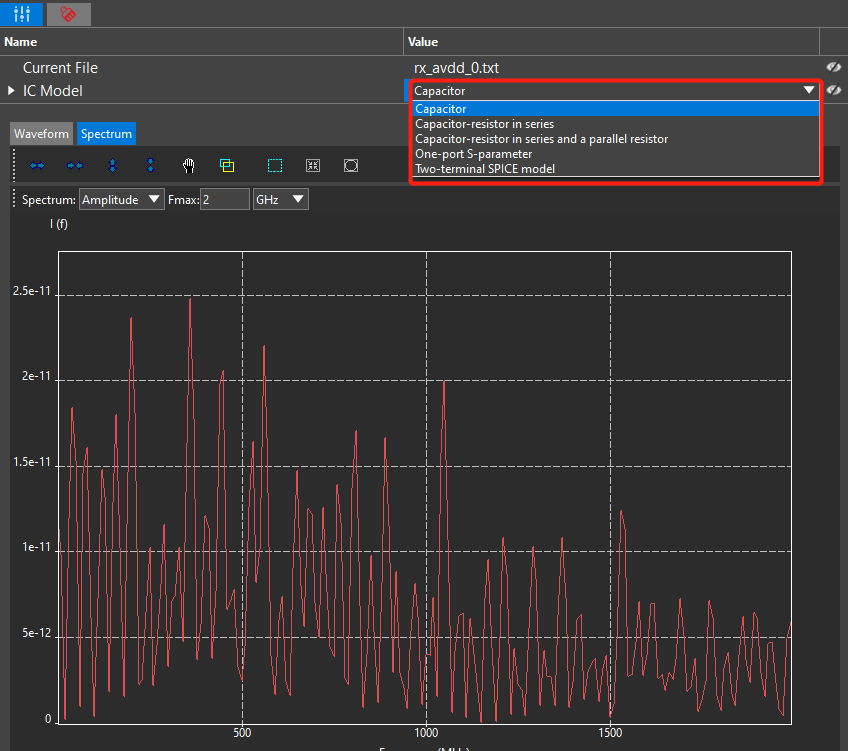

IC模型類型支持 Capacitor, Capacitor-Resistor in series、Capacitor-resitor in series and a parallel resistor、One-port S-parameter、Two-terminal SPICE model。

12

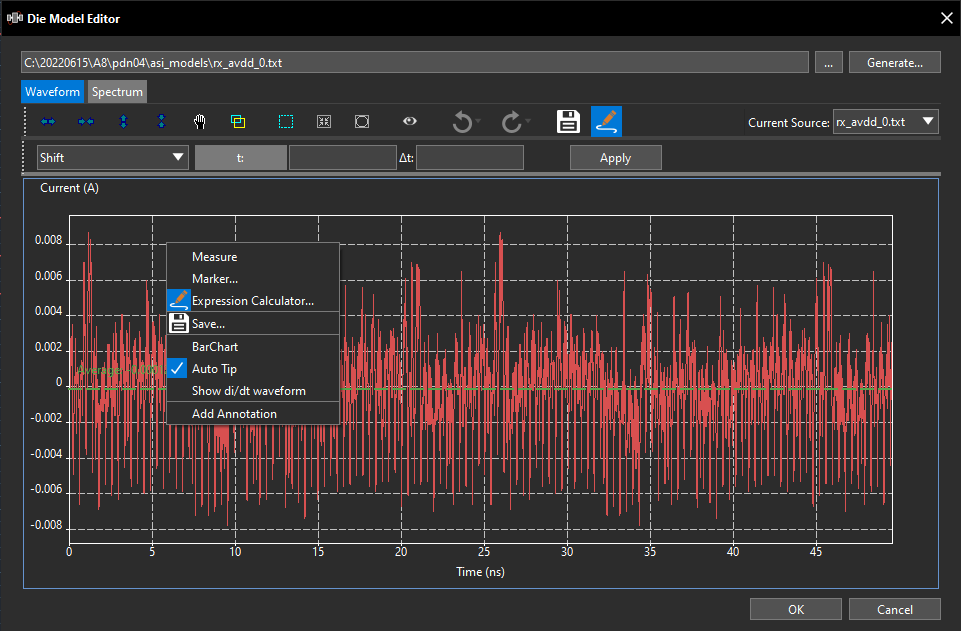

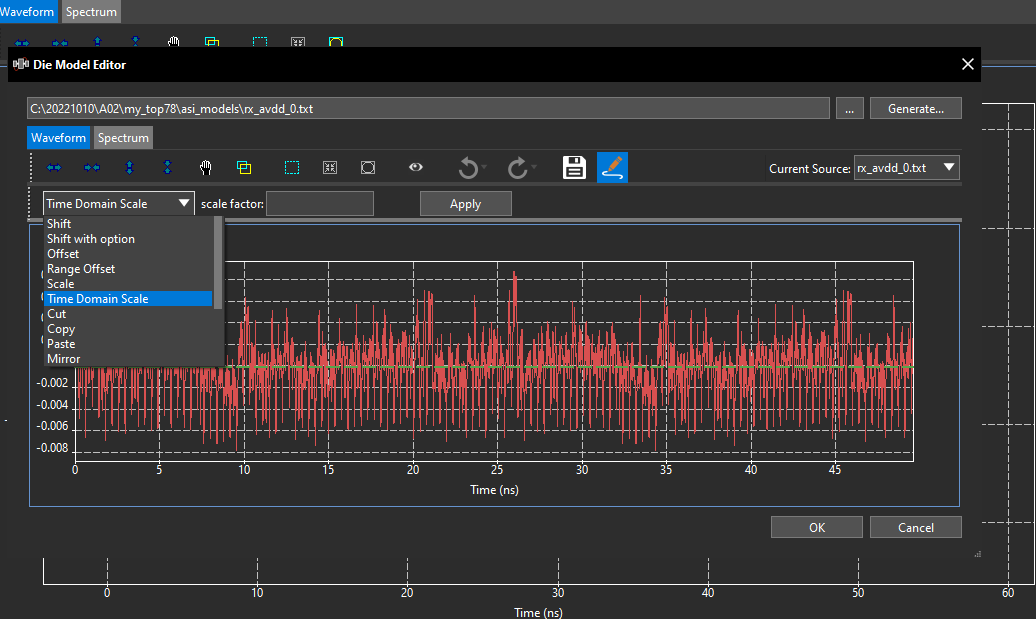

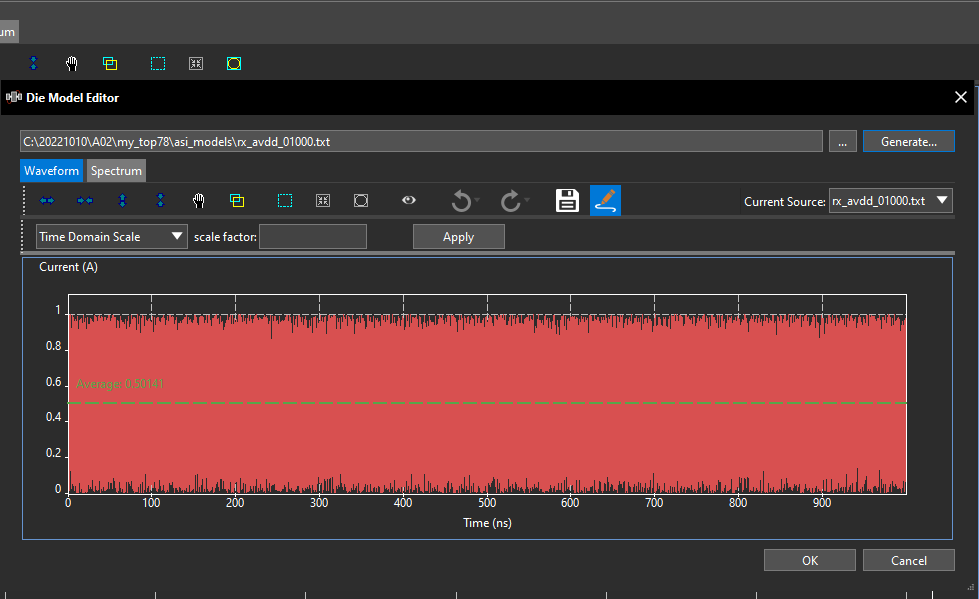

IC 模型支持修改,Die Model Editor 芯片 DIE 模型設(shè)置及編輯,可以按照模型的參數(shù)配置,配置完成后生成的 IC模型,并使用到仿真中。

13

新版本中支持 IC DIE 模型的設(shè)置,對 IC 芯片的模型設(shè)置進行了加強,能夠支持對 IC 芯片的模型進行建模曲線的設(shè)置及生成操作,允許按照設(shè)置的條件來生成 IC 芯片的電流模型。

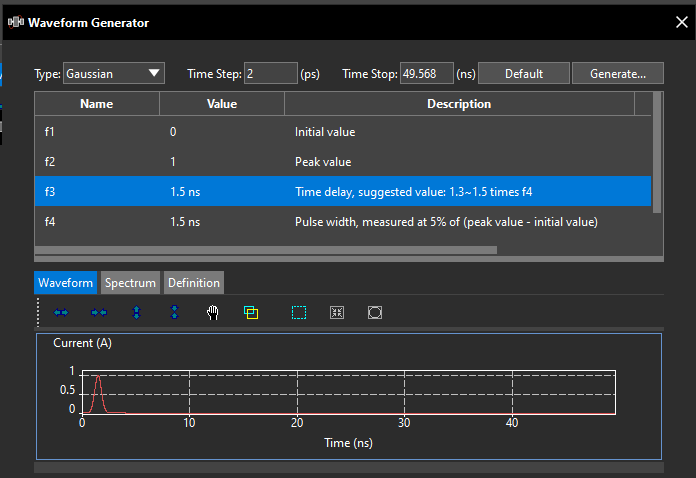

14

能夠支持高斯函數(shù)曲線對 IC 芯片的進行建模設(shè)置,通過定義高斯參數(shù)可以生成曲線電流模型,用來模擬多樣的 IC 電流變化情況。

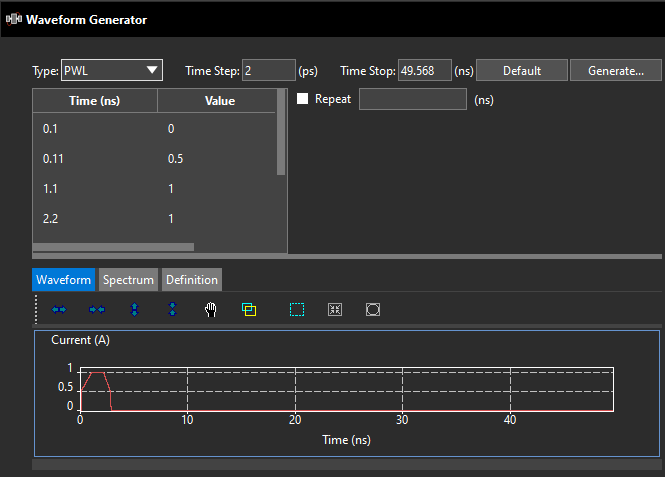

15

能夠支持 PWL 函數(shù)曲線對 IC 芯片的進行建模設(shè)置,通過定義 PWL 函數(shù)曲線可以生成曲線電流模型,用來模擬多樣的 IC 電流變化情況。

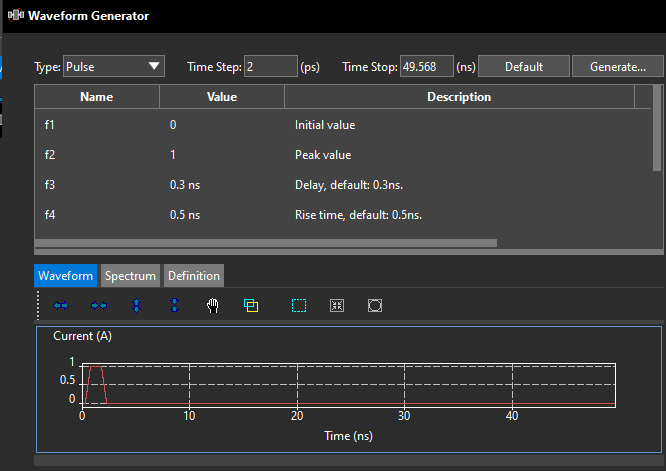

16

能夠支持 Pulse 激勵函數(shù)曲線對 IC 芯片的進行建模設(shè)置,通過定義 Pulse 函數(shù)曲線可以生成曲線電流模型,用來模擬多樣的 IC 電流變化情況。

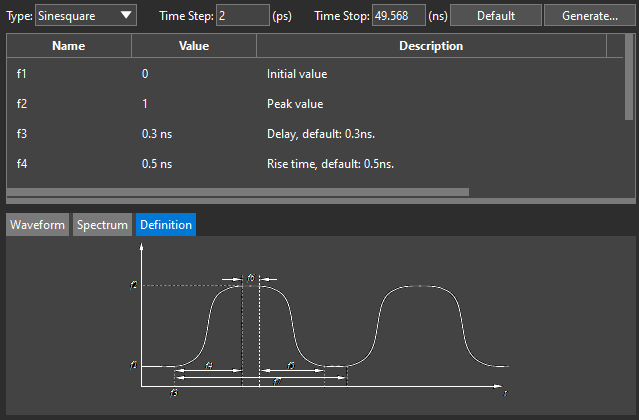

17

能夠支持正弦激勵函數(shù)曲線對 IC 芯片的進行建模設(shè)置,通過定義正弦函數(shù)曲線可以生成曲線電流模型,用來模擬多樣的 IC 電流變化情況。

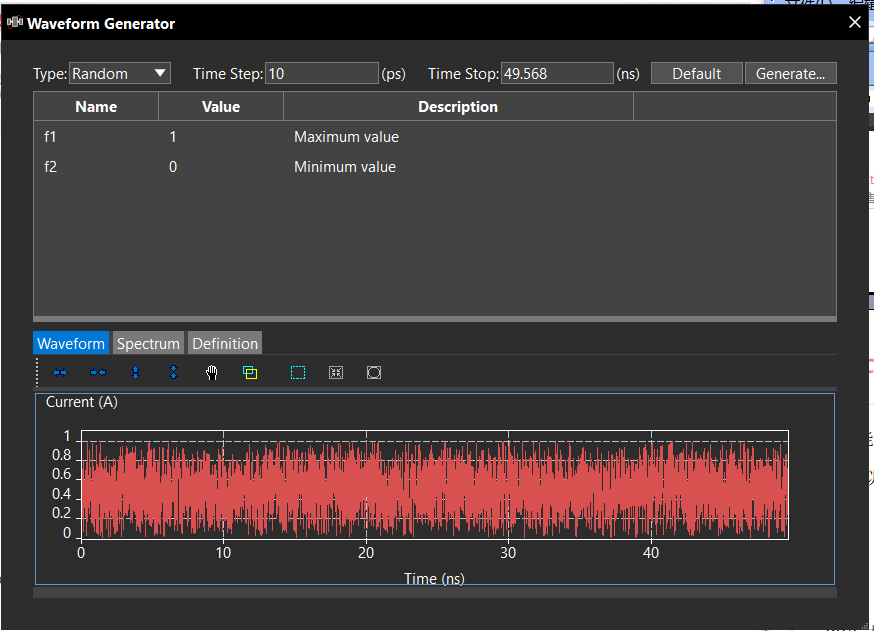

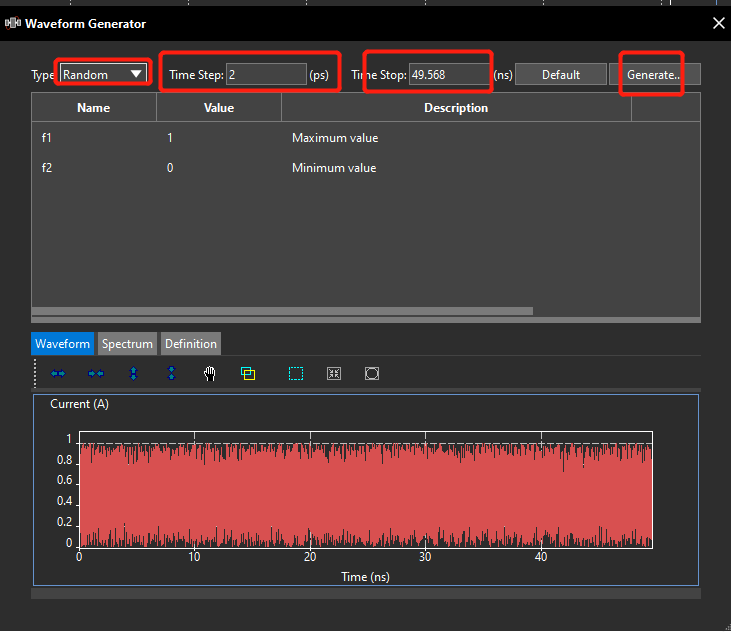

18

能夠支持隨機函數(shù)曲線對 IC 芯片的進行建模設(shè)置,通過定義隨機函數(shù)曲線可以生成曲線電流模型,用來模擬多樣的 IC 電流變化情況。

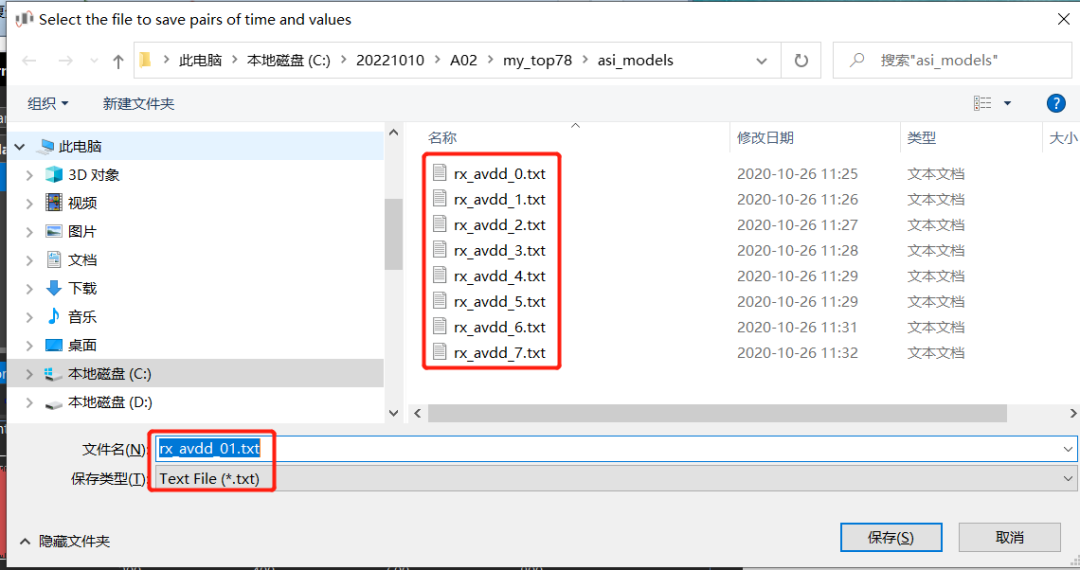

19

生成 IC 芯片的模型文件可以支持進行建模保存成 TXT 文件。

20

新的 IC 芯片的模型后的 IC 模型結(jié)果顯示,通過設(shè)置建立出新的 IC 電流模型。

21

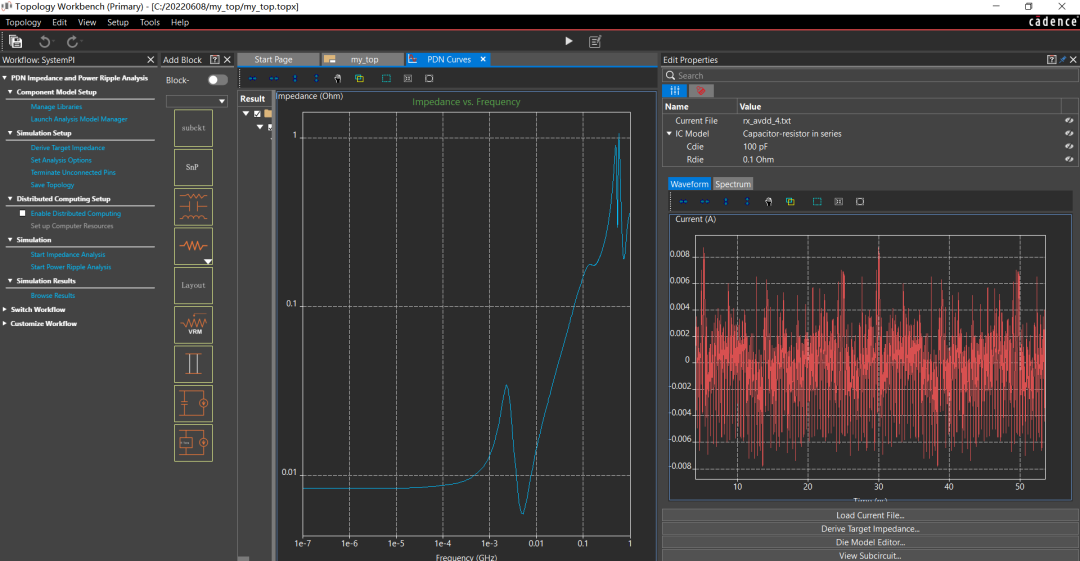

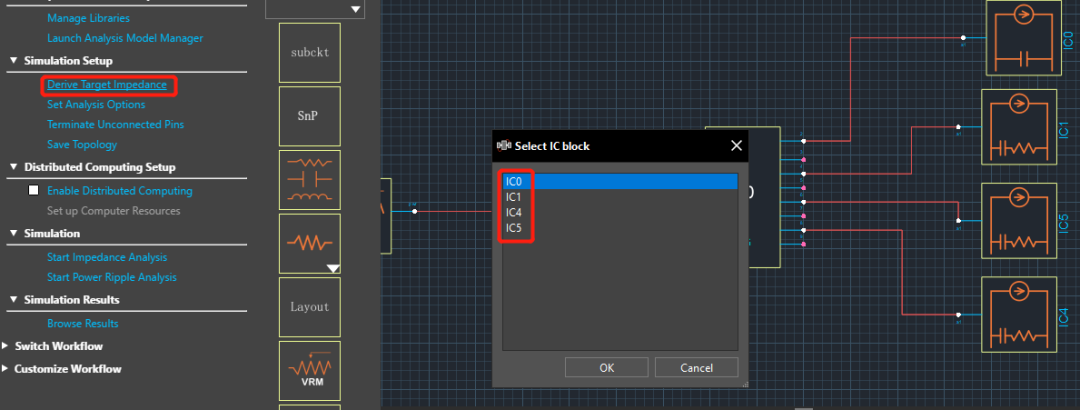

設(shè)置器件的目標(biāo)阻抗,選擇 Derive Target Impedance 可以進行 IC 芯片的目標(biāo)阻抗的設(shè)置。不同的 IC 芯片可以設(shè)置成不同的目標(biāo)阻抗。

22

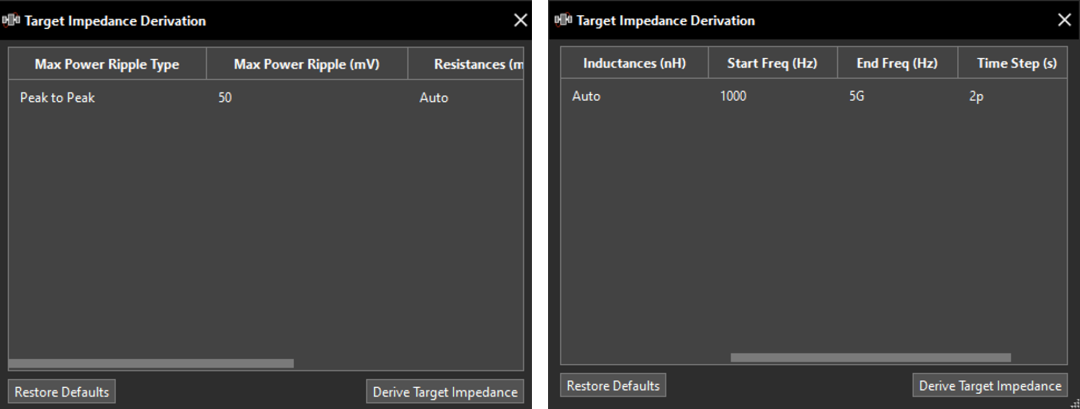

IC 芯片設(shè)置目標(biāo)阻抗,關(guān)鍵參數(shù)設(shè)置峰峰紋波噪聲,最大的電源紋波、電阻、開始頻率、截至頻率、等參數(shù)設(shè)置。不同的 IC 芯片可以設(shè)置成不同的目標(biāo)阻抗。

23

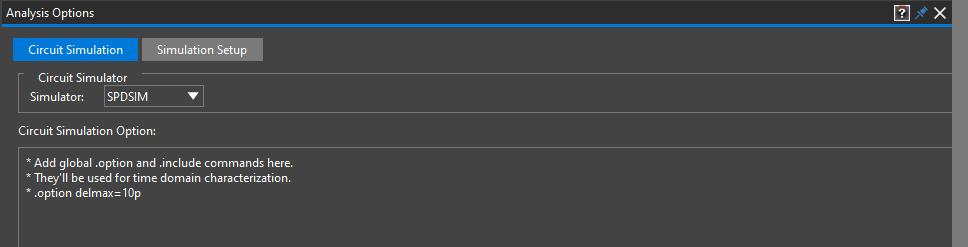

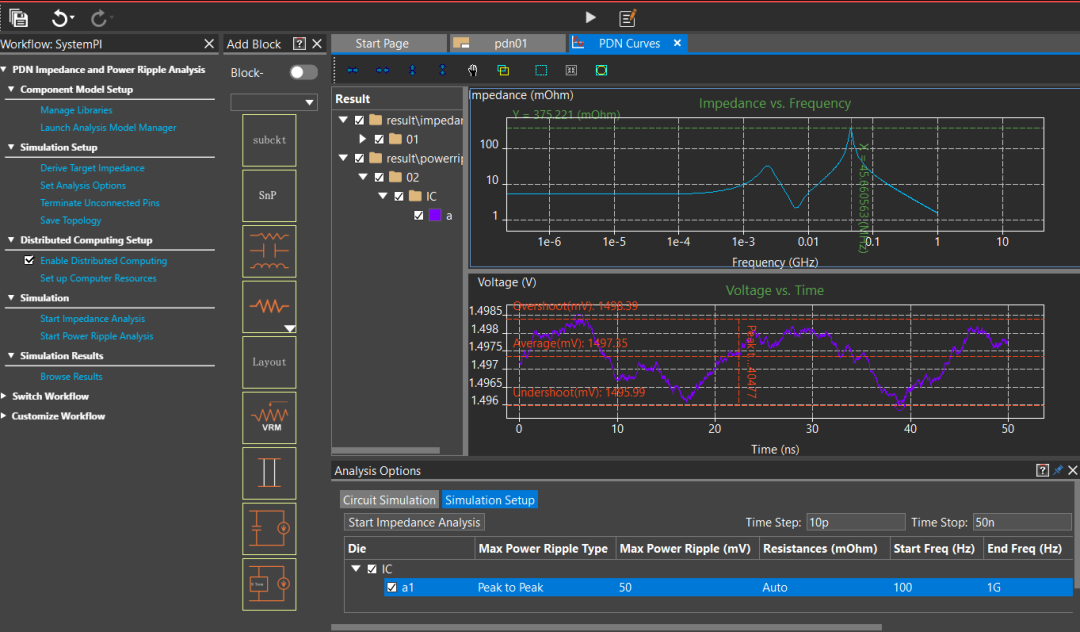

Set Analysis Options 用來設(shè)置分析的可選項,Circuit Simulation 引擎使用 SPDSIM。

24

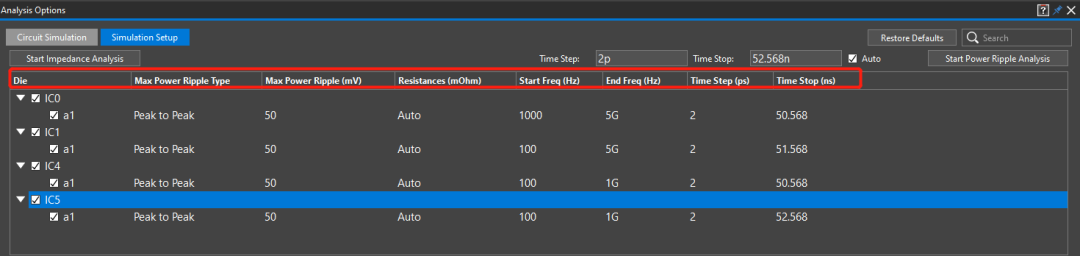

Simulation Setup 用來配置仿真參數(shù),關(guān)鍵參數(shù)設(shè)置峰峰紋波噪聲,最大的電源紋波、電阻、開始頻率、截至頻率、等參數(shù)顯示為已經(jīng)設(shè)置完成的參數(shù)。Time Step 設(shè)置仿真時間步長,Time Stop 設(shè)置仿真結(jié)束時間。在需要進行仿真的 IC 芯片上打勾表示參與本次仿真。

25

Terminate Unconnected Pins 端接未使用的 PIN 的模設(shè)置,未使用的電源 PIN 的設(shè)置,Ground PIN 的設(shè)置。

26

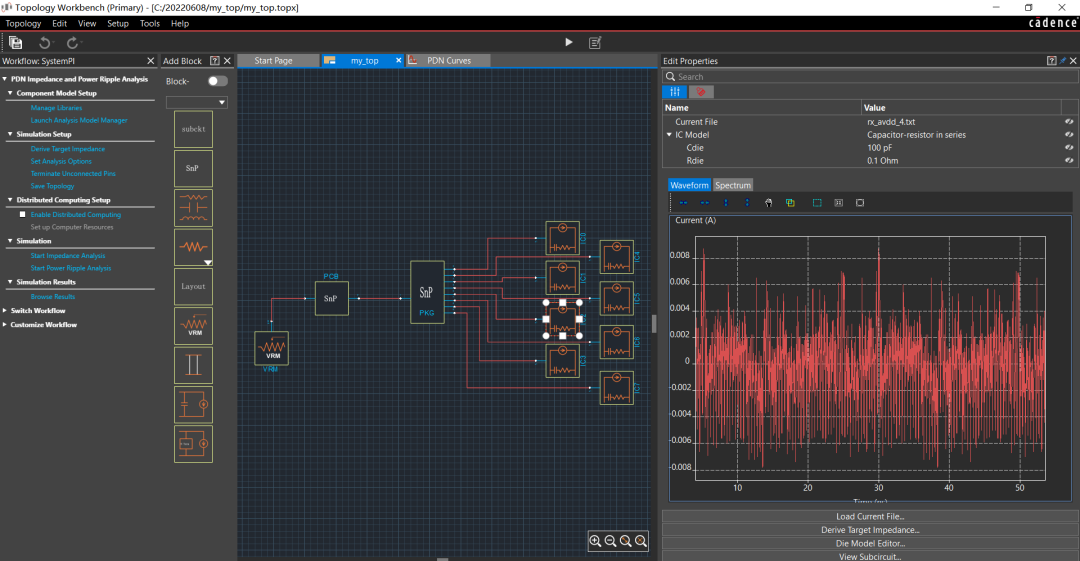

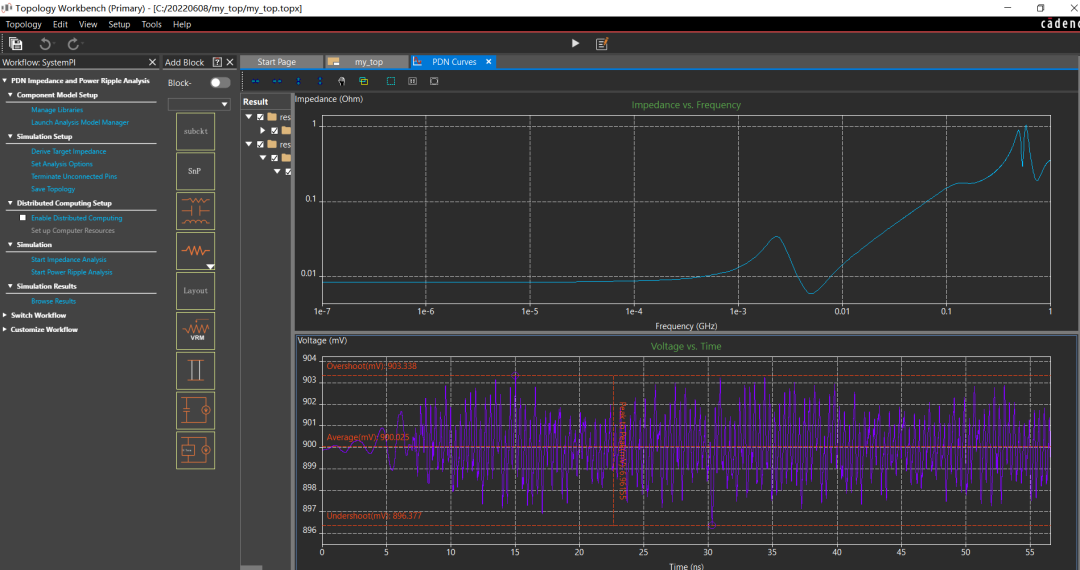

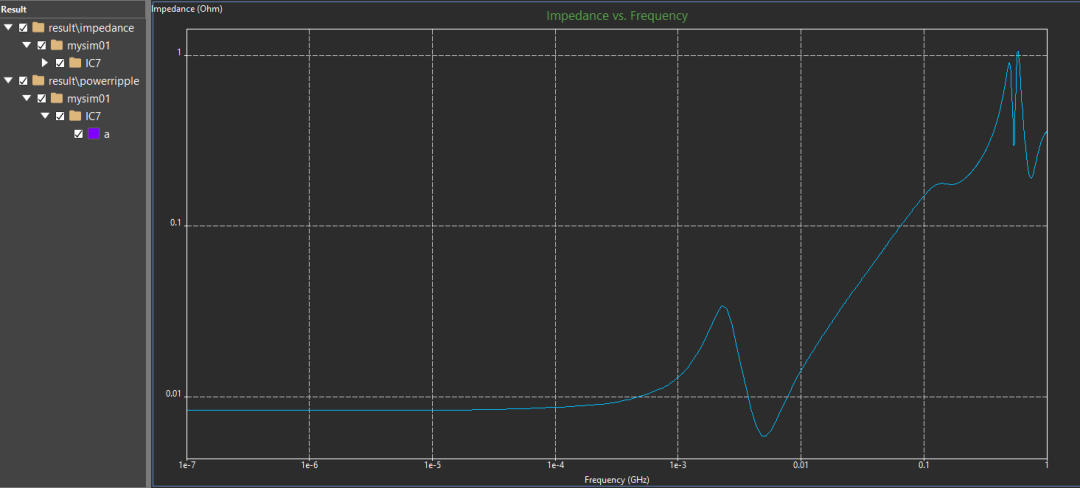

Start Impedance Analysis 執(zhí)行仿真以后,可以得到 PDN 阻抗仿真結(jié)果。

27

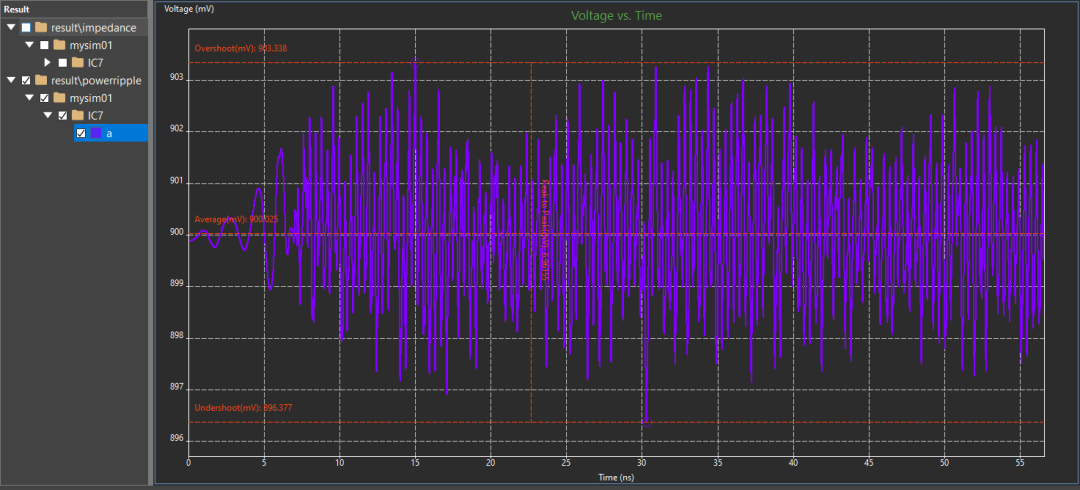

Start Power Ripple Analysis 執(zhí)行仿真,可以得到源紋波噪聲仿真結(jié)果。

28

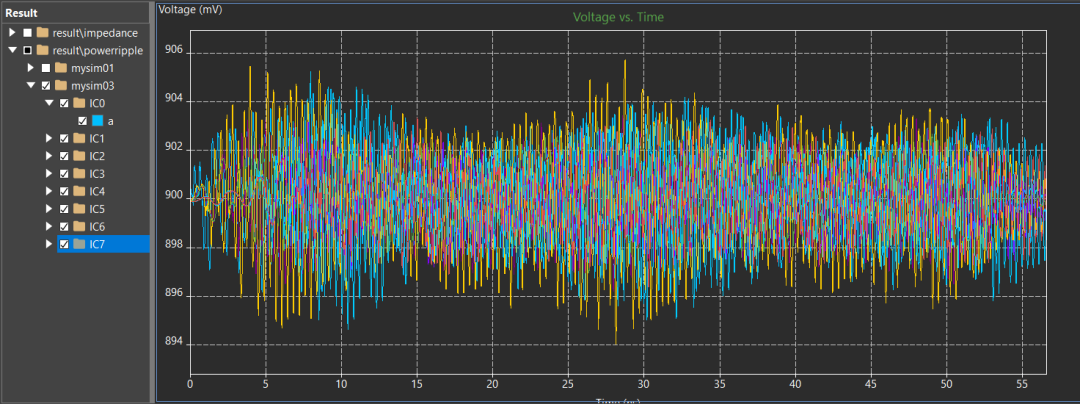

在需要進行仿真的 IC 芯片上打勾,對 IC 芯片的噪聲進行仿真,完成后可以得到電源紋波噪聲仿真結(jié)果。

29

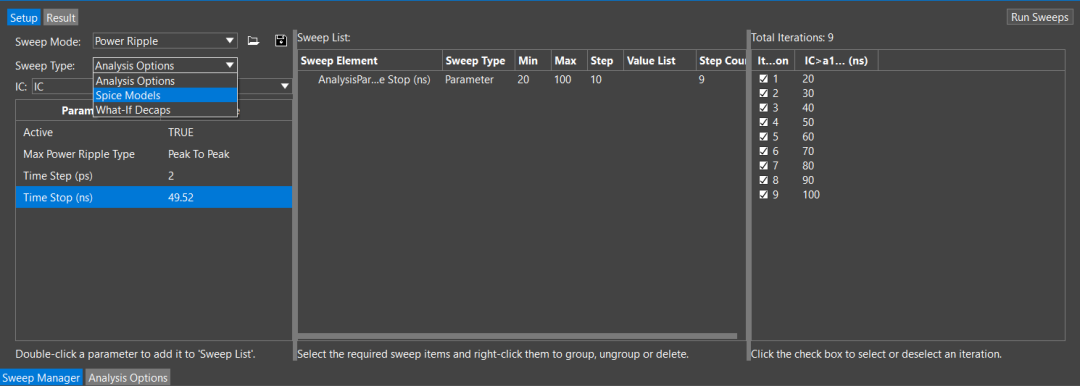

Sweep Manager 掃描管理器中可以支持對仿真電路的參數(shù)進行掃描,支持對 Analysis Options 分析參數(shù)設(shè)置,Spice Models 元件 spice 模型,What-If Decaps 假設(shè)電容優(yōu)化。可以支持單一或者多參數(shù)進行掃描。

30

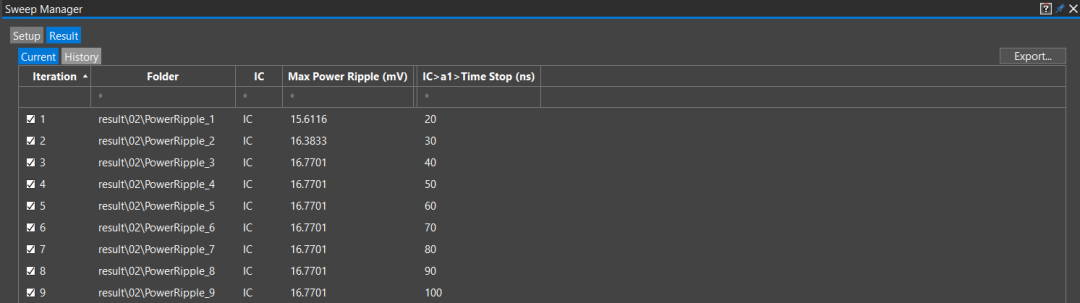

Sweep Manager 掃描管理器仿真執(zhí)行完成以后,可以得到掃描參數(shù)的掃描結(jié)果。

31

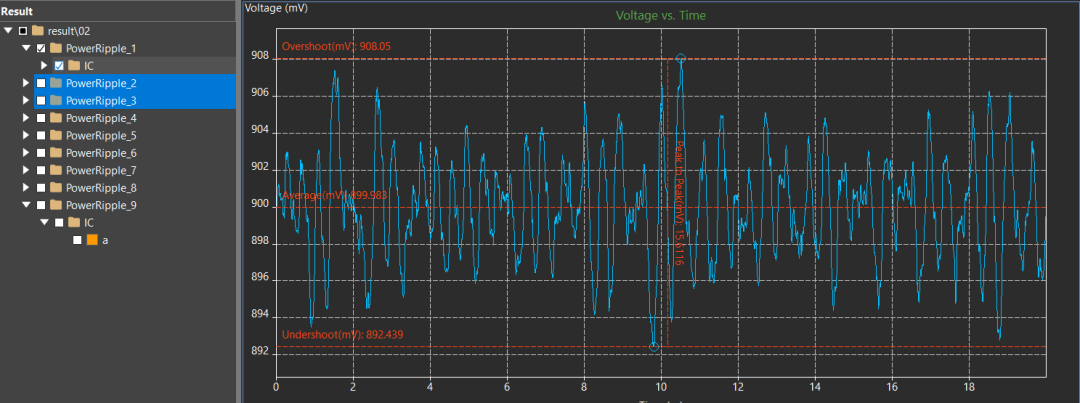

Sweep Manager 掃描管理器仿真執(zhí)行完成以后,可以查看到掃描仿真得到的結(jié)果。

32

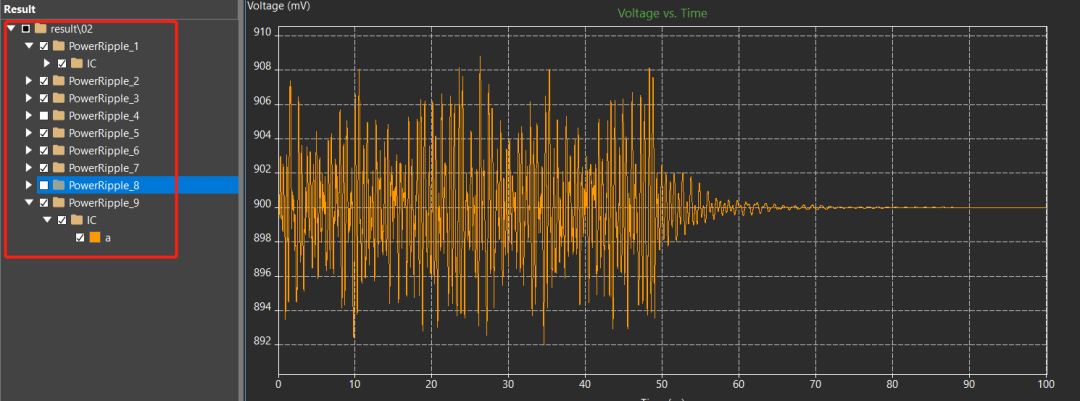

Sweep Manager 掃描管理器仿真執(zhí)行完成以后可以查看到掃描仿真得到的結(jié)果,多參數(shù)掃描結(jié)果可以分別查看或者集中結(jié)果顯示。

Sigrity SystemPI 軟件中自定義搭建鏈路進行電源PDN 阻抗分析和交流電壓紋波分析,已經(jīng)都講解完成啦,請大家快在自己的軟件里面嘗試下吧~

-

allegro

+關(guān)注

關(guān)注

42文章

660瀏覽量

145343

發(fā)布評論請先 登錄

相關(guān)推薦

think-cell:自定義think-cell(四)

think-cell;自定義think-cell(一)

Simulink自定義模塊開發(fā)教程 Simulink 在控制系統(tǒng)中的應(yīng)用

創(chuàng)建自定義的基于閃存的引導(dǎo)加載程序(BSL)

如何自定義內(nèi)存控制器的設(shè)置

搞定電源完整性,不如先研究PDN!

ChatGPT免費用戶可試駕自定義GPT模型及分析圖表等功能

e203自定義指令硬件模塊設(shè)計,在vivado硬件里自定義指令識別為非法指令怎么解決?

Chrome移動版支持自定義菜單欄功能

HarmonyOS開發(fā)案例:【 自定義彈窗】

TSMaster 自定義 LIN 調(diào)度表編程指導(dǎo)

鴻蒙ArkUI實例:【自定義組件】

利用Sigrity Aurora進行PCB布線后的仿真分析-阻抗及寄生參數(shù)析

2022 SPB 17.4 版本更新 I Sigrity SystemPI 允許自定義搭建鏈路進行系統(tǒng)級PDN和電源紋波分析

2022 SPB 17.4 版本更新 I Sigrity SystemPI 允許自定義搭建鏈路進行系統(tǒng)級PDN和電源紋波分析

評論