引言:氮化鎵作為第三代寬禁帶半導體材料的代表之一,因其優越的性能,例如高電子遷移率、高電子飽和速 率、耐高溫及高熱導率等優點吸引了越來越多的關注,也正是因為這些優點,垂直氮化鎵功率晶體管在未來的電 力電子領域中具有很大的發展和廣泛的應用前景.本文列出氮化鎵材料和其他半導體材料主要的物理參數、氮化 鎵單晶制備及其外延生長的主要方法,闡述了氮化鎵功率器件在目前環境下的優勢.針對器件結構,列出了橫向器 件本身存在的問題和垂直器件的優點,解釋了垂直器件為何能夠成為未來功率器件的主流結構.在此基礎上,詳細 介紹了垂直電流孔徑氮化鎵晶體管、垂直氮化鎵溝槽金屬氧化物半導體場效應晶體管、基于原位氧化氮化鎵夾 層的垂直溝槽金屬氧化物半導體場效應晶體管和垂直氮化鎵鰭式場效應晶體管的結構、工作原理、研究進展及 所存在的一些問題,并將文中所提及的垂直氮化鎵功率晶體管的性能參數按器件種類和時間順序進行歸納,為未 來氮化鎵功率晶體管的發展提出了大致的方向.針對集成電路系統,歸納了氮化鎵功率器件在驅動芯片方面的特 殊要求和關鍵技術.最后,針對當下的市場環境,列舉了垂直氮化鎵功率晶體管在中、低壓范圍內比較熱門且發展 前景較好的應用場景。

電力電子技術是一項使用電力電子器件將電能進 行轉換并加以控制的技術,其核心就是功率半導體器 件,它可以快速高效地完成弱電對強電的控制,是保證 設備正常使用的關鍵技術.功率器件可分為兩類:一類 是以功率二極管、晶閘管、絕緣雙極型晶體管為主的 雙功率半導體器件;另一類是以垂直雙擴散金屬氧化 物晶體管(vertical double diffusion power metal oxide semiconductor, VDMOS)為代表的功率金屬氧化物半導 體(metal oxide semiconductor, MOS)器件為主的單極功 率半導體器件.自1958年以來,硅基金屬氧化物半導體 場效應晶體管就一直在全球微電子行業占據主導地位,并應用于各種電子設備當中.隨著5G技術、汽車、無 線通信、航天航空等技術的高速發展,電氣化程度的 提高對耐高溫、耐高壓、高頻及大功率的性能有著迫 切需求,例如在汽車領域,內部各設備所需的電壓范圍 為600~1500 V,而傳統的硅基器件以及橫向晶體管(如高電子遷移率晶體管, high electron mobility transistor, HEMT)都存在一些問題,如材料性能不足以滿足一 些特殊場景或器件結構所帶來的弊端,導致它們都無 法承擔這一重任。

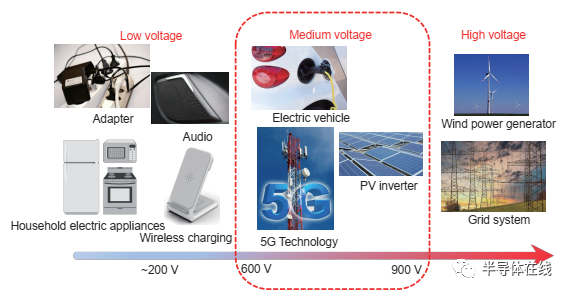

功率半導體器件的進步,核心就是半導體材料的 發展.氮化鎵(GaN)作為第三代寬禁帶半導體的代表之 一,擁有著寬禁帶、高擊穿場強、高熱導率和高電子 漂移速率等優點,制備出的氮化鎵器件導通電阻小、電子遷移率高、熱導性好,而且在散熱、能耗、體積 等方面也有著很大的優勢,不僅能夠極大地提升新興 電力電子器件的性能,還能達到節省能源的效果.如圖1所示,氮化鎵材料在低、中、高壓下都有著很多的應 用場景,適用范圍十分廣泛.加入三代半交流群,加VX:tuoke08。近年來,不管是同質外延,還是異質外延,氮化鎵外延層的碳背景濃度和位錯密 度都在逐漸降低,氮化鎵自支撐襯底的成本逐漸下降,質量逐漸提高,為制備氮化鎵垂直器件打下了堅實的基礎。

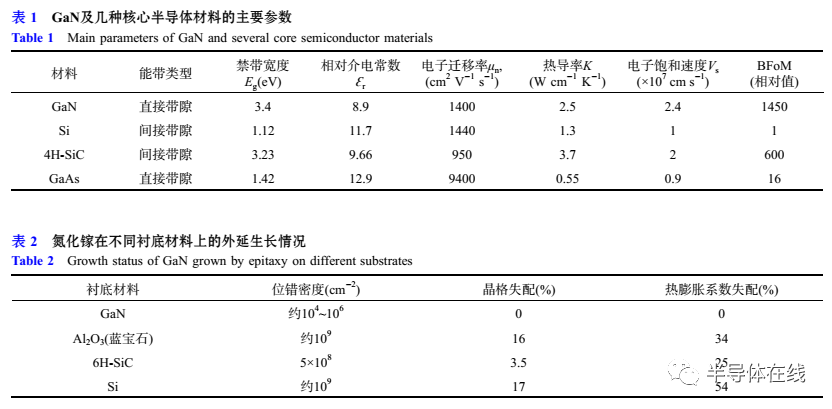

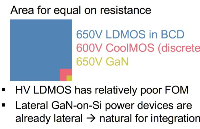

圖 1 (網絡版彩色)氮化鎵功率器件的應用情況本文總結氮化鎵材料與其他半導體材料的主要物 理參數及氮化鎵外延生長的主流方法,主要介紹目前 氮化鎵電流孔徑垂直晶體管、垂直氮化鎵溝槽金屬氧 化物半導體場效應晶體管、基于原位氧化物氮化鎵夾 層的垂直溝槽金屬氧化物半導體場效應晶體管以及氮 化鎵垂直鰭式功率晶體管的發展狀況,概括了氮化鎵 驅動集成電路(integrated circuit, IC)的關鍵技術,列出 了氮化鎵功率晶體管的一些實際應用場景。1氮化鎵材料及其制備方法 1.1氮化鎵材料應用于功率器件的優勢 電力電子器件的蓬勃發展與半導體材料的發展息 息相關.硅材料的出現使得電子器件領域發生了巨大 的變化.隨著單晶硅生產工藝的發展,硅材料很快就占 據了半導體集成電路的主要市場,廣泛應用于各個領 域當中,即便是今天,硅在半導體材料領域依然占有很 高的份額.隨著功率器件的發展,硅基電力電子器件的 性能逐漸逼近材料極限,很難有更大的突破.第二代半 導體砷化鎵(GaAs)具有更高的電子遷移率和飽和電子 速度等優勢,稍微緩解了這一現象,但是由于GaAs材料 的禁帶寬度、熱導率、擊穿場強及制作成本與硅(Si)材料相比并沒有太大的優勢,導致其在高壓高頻率領 域中得不到廣泛的應用.因此,以GaN為代表的第三代 半導體橫空出世,掀起了研究GaN基器件的熱潮.表1列出了GaN與其他半導體材料的主要參數。從表1可以看出, GaN是直接間隙半導體,其禁帶 寬度達到3.4 eV,與Si、碳化硅(4H-SiC)和GaAs相比, GaN在擊穿場強、熱導率和電子飽和速度等方面有著 更大的優勢.同時, GaN的功率品質因數(Baliga figure of merit, BFoM)比其他材料大得多,這也就意味著GaN基器件能夠更好地在高溫、高壓和高頻率的環境下 工作。

圖 1 (網絡版彩色)氮化鎵功率器件的應用情況本文總結氮化鎵材料與其他半導體材料的主要物 理參數及氮化鎵外延生長的主流方法,主要介紹目前 氮化鎵電流孔徑垂直晶體管、垂直氮化鎵溝槽金屬氧 化物半導體場效應晶體管、基于原位氧化物氮化鎵夾 層的垂直溝槽金屬氧化物半導體場效應晶體管以及氮 化鎵垂直鰭式功率晶體管的發展狀況,概括了氮化鎵 驅動集成電路(integrated circuit, IC)的關鍵技術,列出 了氮化鎵功率晶體管的一些實際應用場景。1氮化鎵材料及其制備方法 1.1氮化鎵材料應用于功率器件的優勢 電力電子器件的蓬勃發展與半導體材料的發展息 息相關.硅材料的出現使得電子器件領域發生了巨大 的變化.隨著單晶硅生產工藝的發展,硅材料很快就占 據了半導體集成電路的主要市場,廣泛應用于各個領 域當中,即便是今天,硅在半導體材料領域依然占有很 高的份額.隨著功率器件的發展,硅基電力電子器件的 性能逐漸逼近材料極限,很難有更大的突破.第二代半 導體砷化鎵(GaAs)具有更高的電子遷移率和飽和電子 速度等優勢,稍微緩解了這一現象,但是由于GaAs材料 的禁帶寬度、熱導率、擊穿場強及制作成本與硅(Si)材料相比并沒有太大的優勢,導致其在高壓高頻率領 域中得不到廣泛的應用.因此,以GaN為代表的第三代 半導體橫空出世,掀起了研究GaN基器件的熱潮.表1列出了GaN與其他半導體材料的主要參數。從表1可以看出, GaN是直接間隙半導體,其禁帶 寬度達到3.4 eV,與Si、碳化硅(4H-SiC)和GaAs相比, GaN在擊穿場強、熱導率和電子飽和速度等方面有著 更大的優勢.同時, GaN的功率品質因數(Baliga figure of merit, BFoM)比其他材料大得多,這也就意味著GaN基器件能夠更好地在高溫、高壓和高頻率的環境下 工作。 1.2氮化鎵襯底及其外延層的制備 在過去10年中,同質外延生長GaN的成本很高,為 降低器件的制造成本,采用了在Si、SiC和藍寶石上異 質外延生長的方法,以上這些襯底相比單晶氮化鎵襯 底具有更低的成本,因此在市場上應用廣泛.但是,異 質外延生長的GaN內部存在著較大的晶格失配及熱失 配等問題.表2給出了在不同襯底上外延生長GaN的缺 陷濃度、晶格失配和熱失配情況.這些失配將會導致 外延層產生晶格扭曲,從而形成較高的位錯密度,甚至 破裂等問題,會嚴重影響GaN基器件的性能和使用 壽命,這是目前GaN基器件的性能遠低于其材料理論 極限的重要原因之一。高質量的GaN單晶材料是制備高性能器件的基礎,也是根本保障.獲得高質量GaN外延層的最佳方案就 是同質外延,即在塊狀GaN襯底上外延生長GaN層.目 前, GaN單晶材料的生長方式主要分為氣相外延和液 相外延.其中,氣相外延包括金屬有機物化學氣相沉積(metal organic chemical vapor deposition, MOCVD)、氫 化物氣相外延(hydride vapor phase epitaxy, HVPE)及其 衍生方法,特點在于生產速率快、尺寸大,但晶體質量 有待提高,產品一致性較差.液相外延主要采用氨熱法 和助溶劑法,其特點是可制備高純度、高晶體質量且 重復性高的GaN單晶襯底,但是對設備的要求高,并且 生長速率較低.在商業應用中,較低成本HVPE應用最 廣泛也最成熟,并且隨著改良,與氨熱法和鈉助熔劑法 結合,生產的GaN單晶襯底的位錯密度在不斷降低,晶 圓尺寸在逐漸增大,制備成本也在不斷地降低。HVPE生產出的GaN是未摻雜的,其載流子濃度只 有1016~1017cm?3,難以用于半導體器件的制備,需針 對不同的器件引入不同的摻雜劑,從而改變GaN的電 學性質.其中,淺施主摻雜劑有硅和鍺,淺受主摻雜 劑有鎂,深能級摻雜劑有鐵和碳,可分別實現GaN的N型、P型和半絕緣電特性,再加上高純半絕緣GaN的發展,可以有效提高器件的耐壓能力,從而滿足 各種器件的要求。

1.2氮化鎵襯底及其外延層的制備 在過去10年中,同質外延生長GaN的成本很高,為 降低器件的制造成本,采用了在Si、SiC和藍寶石上異 質外延生長的方法,以上這些襯底相比單晶氮化鎵襯 底具有更低的成本,因此在市場上應用廣泛.但是,異 質外延生長的GaN內部存在著較大的晶格失配及熱失 配等問題.表2給出了在不同襯底上外延生長GaN的缺 陷濃度、晶格失配和熱失配情況.這些失配將會導致 外延層產生晶格扭曲,從而形成較高的位錯密度,甚至 破裂等問題,會嚴重影響GaN基器件的性能和使用 壽命,這是目前GaN基器件的性能遠低于其材料理論 極限的重要原因之一。高質量的GaN單晶材料是制備高性能器件的基礎,也是根本保障.獲得高質量GaN外延層的最佳方案就 是同質外延,即在塊狀GaN襯底上外延生長GaN層.目 前, GaN單晶材料的生長方式主要分為氣相外延和液 相外延.其中,氣相外延包括金屬有機物化學氣相沉積(metal organic chemical vapor deposition, MOCVD)、氫 化物氣相外延(hydride vapor phase epitaxy, HVPE)及其 衍生方法,特點在于生產速率快、尺寸大,但晶體質量 有待提高,產品一致性較差.液相外延主要采用氨熱法 和助溶劑法,其特點是可制備高純度、高晶體質量且 重復性高的GaN單晶襯底,但是對設備的要求高,并且 生長速率較低.在商業應用中,較低成本HVPE應用最 廣泛也最成熟,并且隨著改良,與氨熱法和鈉助熔劑法 結合,生產的GaN單晶襯底的位錯密度在不斷降低,晶 圓尺寸在逐漸增大,制備成本也在不斷地降低。HVPE生產出的GaN是未摻雜的,其載流子濃度只 有1016~1017cm?3,難以用于半導體器件的制備,需針 對不同的器件引入不同的摻雜劑,從而改變GaN的電 學性質.其中,淺施主摻雜劑有硅和鍺,淺受主摻雜 劑有鎂,深能級摻雜劑有鐵和碳,可分別實現GaN的N型、P型和半絕緣電特性,再加上高純半絕緣GaN的發展,可以有效提高器件的耐壓能力,從而滿足 各種器件的要求。

2垂直氮化鎵功率晶體管 按電流在器件內部的流動方向,目前GaN基器件 的結構可分為橫向結構和垂直結構.橫向器件(主要是HEMT)的內部電場分布不均勻,峰值電場會集中在漏 極和柵極邊緣(電場集中效應),該處的電場強度大于GaN材料的臨界擊穿場強,導致器件提前擊穿,難以發 揮GaN材料耐高壓的優勢.而且,擊穿電壓和柵極-漏極 的間距成正比,即要提高器件的耐壓水平就必須增大 器件面積,這不僅增加了制作成本,還不利于后期的集 成;橫向器件對緩沖層的厚度和晶體質量也有一定的 要求,增加了器件外延生長的生產成本和復雜性;再加 上表面陷阱態和電場擁擠的影響,很容易使器件產生 電流崩塌,從而達不到預計的電流值。垂直GaN器件的電流方向平行于GaN外延層的生 長方向,這種設計可以有效地提高器件的導通電流和 擊穿電壓.在不改變器件尺寸的情況下,增加GaN漂移 層的厚度即可提高器件的擊穿電壓.垂直器件無需考 慮表面陷阱對其的影響=,內部電場在遠離表面的GaN層中達到峰值,提高了器件耐壓水平的下限.最重要的是, GaN垂直功率器件具有雪崩能力,即存在雪崩 擊穿,這是橫向結構不可能有的,該優點提高了器件的 可靠性,避免了過度設計設備.下面分別介紹垂直結構 的氮化鎵電流孔徑晶體管、氮化鎵溝槽金屬氧化物半 導體場效應晶體管、基于原位氧化物氮化鎵夾層的垂 直溝槽金屬氧化物半導體場效應晶體管和氮化鎵鰭式 晶體管的原理、結構及主要發展情況。

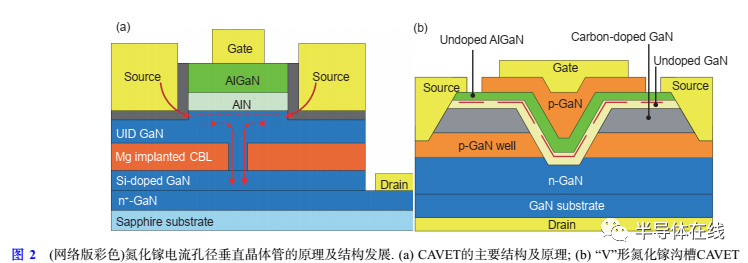

2.1氮化鎵電流孔徑垂直晶體管 電流孔徑垂直晶體管(current aperture vertical electron transistor, CAVET)是橫向拓撲和縱向拓撲的有效 結合,目的是發揮AlGaN/GaN異質結處二維電子氣溝 道(two-dimensional electron gas, 2DEG)的高導電性以 及垂直結構所帶來的優勢.第一個用于高壓應用的GaN基CAVET結構由Ben-Yaacov等人開發完成,其 結構與雙擴散MOS(double diffused metal oxide semiconductor, DDMOS)結構類似,如圖2(a)所示.其中,電 流阻擋層(current-blocking layer, CBL)是通過在GaN層 中摻雜Mg實現的,用來將電流限制在柵極下方的小孔 徑區域.通過對柵極施加偏壓從而控制2DEG的開啟和 關斷,不同于橫向結構的HEMT,這種開關的優勢是:在 電壓阻斷的情況下,高電場區將主要位于柵極下方,即 表面發生擊穿的可能性下降,可提供更高的擊穿電壓.然而,由于CAVET的AlGaN/GaN溝道依賴于柵極調控,因此該器件通常處于常開狀態。 為了提高開關速度和安全性,增強型(enhance mode, E-mode)器件是大功率設備的優先選擇. Chowdhury等人通過使用Mg離子注入的GaN作為非 合金源的電流阻擋層,并在柵極金屬化之前對柵極區 域進行10 min的CF4處理,制作了第一個增強型CAVET,其最大源漏電流為5.6×103A/cm2,實現了高達0.6 V的 閾值電壓.在該器件的制備過程中,因為異質結層(AlGaN/GaN)是在M g摻電流阻擋層形成之后通過MOCVD再生長的, Mg離子的向上擴散使得器件的閾 值電壓發生了明顯的變化.于是, Chowdhury等人改 變了AlGaN/GaN層的生長方式,通過分子束外延(molecular beam epitaxy, MBE)進行再生長,制備出的器件在 源柵電壓為–15 V條件下,擊穿電壓約為250 V,比導通 電阻為2.2 mΩ cm2。 為保持p-GaN的導電性, Yeluri等人通過掩埋導 電p-GaN層作為電流阻擋層.其中, p-GaN層通過MOCVD再生長,溝道則通過氨分子束外延來完成,制 備出的器件比導通電阻降至0.4 mΩ cm2,導通電流可達10.9 kA/cm2. Nie等人在原結構基礎上增加了邊緣終 端結構,并在柵極和AlGaN阻擋層之間新增一層pGaN,使其可以正常地關閉操作,制備出的晶體管表現 出大于2.3 A的飽和電流、1.5 kV的擊穿電壓、2.2 mΩ cm2的比導通電阻及1.0×109V2/cm2的品質因數(figure of merit, FOM). 2010年,松下公司制備了一種擊穿電 壓為1.7 kV,導通電阻為1.0 mΩ cm2的“V”形溝槽CAVET,如圖2(b)所示,其中p-GaN/AlGaN/GaN三層在漂 移層上形成的“V”形槽上外延再生長.該溝道利用了半 極性面,降低了AlGaN/GaN界面處薄層載流子濃度,實 現了2.5 V的高閾值電壓和穩定的開關操作.值得一提 的是,溝道下方的p-GaN阱層上形成了含碳摻雜的絕緣GaN層,該層能夠抑制截止狀態下源極和漏極之間的 穿通電流,實現了良好的截止狀態特性,并在400 V/15 A條件下實現了快速開關。 Ji等人的器件制備流程與上述提及的類似,不同 點在于移除了柵極下方的p-GaN層,得到了閾值電壓為20 V、擊穿電壓為225 V的常關型溝槽CAVET.在隨后 的研究中,他們通過改善柵極溝槽蝕刻質量和采用 柵極電介質使擊穿電壓達到了880 V,比導通電阻為2.7 mΩ cm2,減少了柵極與漏極之間的泄漏.由于柵極采用 金屬-絕緣層-半導體(metal insulation semiconductor, MIS)結構,閾值電壓從20 V變為21 V. 2022年, Danielraj等人采用一種三角形(“▽”形)凹槽的GaN CAVET,實現了1513~1590 V的擊穿電壓及1.24 mΩ cm2的低導 通電阻,但因為該器件的柵極長度可縮放,其性能及可 靠性可能會受到電流崩塌、短溝道效應和漏電流的影 響,為了克服短溝道器件中關態漏電流的影響,在 其中摻入碳或鎂用于補償。GaN CAVET距離廣泛地商業應用仍需要進一步的 發展,主要問題源于再生長工藝.相鄰電流阻擋層之間 形成的孔徑區域,其摻雜和尺寸大小控制導致制造工 藝相對復雜且難以控制,且因生長工藝所存在的問題,將導致器件的源極和漏極、柵極和漏極之間有著很高 的漏電流,難以大規模生產使用。

Ji等人的器件制備流程與上述提及的類似,不同 點在于移除了柵極下方的p-GaN層,得到了閾值電壓為20 V、擊穿電壓為225 V的常關型溝槽CAVET.在隨后 的研究中,他們通過改善柵極溝槽蝕刻質量和采用 柵極電介質使擊穿電壓達到了880 V,比導通電阻為2.7 mΩ cm2,減少了柵極與漏極之間的泄漏.由于柵極采用 金屬-絕緣層-半導體(metal insulation semiconductor, MIS)結構,閾值電壓從20 V變為21 V. 2022年, Danielraj等人采用一種三角形(“▽”形)凹槽的GaN CAVET,實現了1513~1590 V的擊穿電壓及1.24 mΩ cm2的低導 通電阻,但因為該器件的柵極長度可縮放,其性能及可 靠性可能會受到電流崩塌、短溝道效應和漏電流的影 響,為了克服短溝道器件中關態漏電流的影響,在 其中摻入碳或鎂用于補償。GaN CAVET距離廣泛地商業應用仍需要進一步的 發展,主要問題源于再生長工藝.相鄰電流阻擋層之間 形成的孔徑區域,其摻雜和尺寸大小控制導致制造工 藝相對復雜且難以控制,且因生長工藝所存在的問題,將導致器件的源極和漏極、柵極和漏極之間有著很高 的漏電流,難以大規模生產使用。

2.2垂直氮化鎵溝槽金屬氧化物半導體場效應晶體管

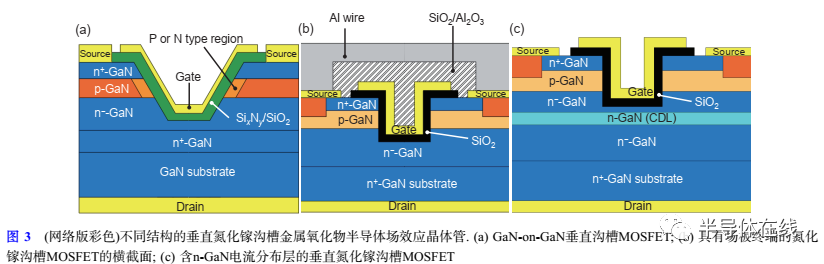

2007年,羅姆半導體集團(ROHM Semiconductor)通過MOCVD在藍寶石襯底上外延生長GaN,并 在此基礎上制造出了氮化鎵溝槽金屬氧化物半導體場 效應晶體管(GaN trench metal oxide semiconductor field effect transistor, GaN trench MOSFET).該器件顯現出良 好的直流特性,導通電壓為5.1 V,這是GaN trench MOSFET首次被報道.如圖3(a)所示, 2008年,羅姆半導 體集團在GaN襯底上制備出首個完全垂直的MOSFET,與之前的研究相同,采用SiO2硬掩模進行遮 擋,在Cl2/SiCl4氛圍中進行等離子體干法蝕刻工藝,形 成垂直柵極的溝槽結構,通過電子回旋共振(electron cyclotron resonance, ECR)等離子體在溝槽內連續沉積 氮化硅(SixNy)和二氧化硅(SiO2),以此組成的雙層結構 作為柵極絕緣體.該器件的閾值電壓為3.4 V,溝道遷移 率達到131 cm2/(V s),導通電阻低于10 mΩ cm2。干法蝕刻工藝會引發一些問題,它會導致溝槽表 面粗糙以及離子轟擊造成損壞,影響溝道遷移率. 2008年,豐田中央研究所的Kodama等人針對這一問題發 展了新的溝槽結構制造方法:使用濃度為25%的四甲 基氫氧化銨(TMAH)作為蝕刻劑,通過濕法蝕刻獲得光 滑的非極性( 1100 )平面. TMAH溶液與氫氧化鉀(KOH)不同,它不會造成堿金屬污染,可獲得平滑的垂直側 壁,從而提高溝道遷移率. He等人通過酸洗和后續NH4鈍化獲得了高質量的MOS界面,在4英寸(1 in =2.54 cm)的自支撐GaN晶圓片上制備出擊穿高壓高達1306 V、比導通電阻為1.93 mΩ cm2的大面積GaN Trench MOSFET,為以后大面積生長提供了更多的選擇。為了進一步提高耐壓, Oka等人在MOSFET的隔 離臺面周圍增加了場板結構,圖3(b)為結構示意圖.該 結構有效減緩了PN結邊緣存在的電場擁擠效應,擊穿 電壓從775 V提高到1605 V,比導通電阻為12.1 mΩ cm2,仍需要改善. 2015年,他們減小n?-GaN的厚度,但 增加其摻雜濃度,降低p-GaN的厚度和摻雜濃度,通過 采用規則六角單元溝槽柵極布局來增加單位面積的柵極寬度,雖然擊穿電壓降低到1250 V,但是比導通電 阻從12.1 mΩ cm2大幅度地降低到1.8 mΩ cm2,并在保 證擊穿電壓超過1.2 kV的特性下,制造的尺寸為1.5 mm ×1.5 mm,并且支持高達23.2 A大電流的GaN Trench MOSFET.為了使器件能夠在更高的電流中工作, Oka等人在n?-GaN中插入一層電流分布層(Current distribution layer, CDL),使正向電流密度提高了1.17倍,并制備出了能夠在100 A電流下工作的3 mm×3 mm大 尺寸垂直溝槽GaN MOSFET,其橫截面結構如圖3(c)所 示.他們分別對有無CDL層的器件進行了電學測試,帶CDL層的MOSFET性能表現更佳.該器件中的電流分 布層由輕薄的n型摻雜層組成,摻雜濃度為2×1016cm?3,并遠離p-GaN溝道層,這樣可避免p-GaN溝道引起的電 流分布層耗盡,在不影響擊穿電壓的情況下,使有效電 流在漂移層中擴散,更好地分配來自柵極溝槽底部的 電流,從而提高器件的最大工作電流。

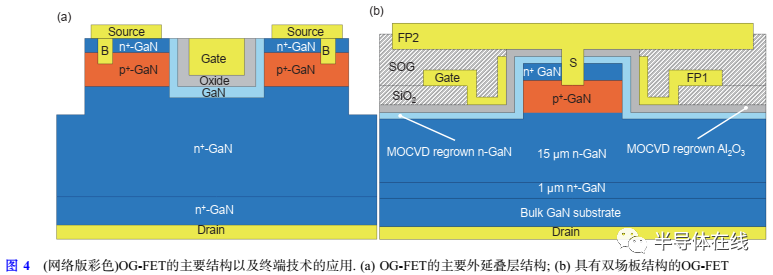

溝槽深度對器件的比導通電阻有著重要的影響,溝槽深度增加,由漂移層中耗盡區形成的勢壘會削弱 對電流路徑的影響.加寬溝槽下電流路徑的寬度,會降 低導通電阻,但也會降低擊穿電壓,因此在器件結構 設計中需仔細考慮溝槽的深度. p-GaN層的參數在調節 垂直GaN MOSFET的閾值電壓、比導通電阻和最大漏 極電流方面也起著重要的作用:降低p-GaN的摻雜濃度 可以使比導通電阻降低,但會導致最大漏極電流增 加、閾值電壓降低; p-GaN的厚度和摻雜濃度的乘 積會影響器件的擊穿機制,當其乘積足夠高時,擊穿機 制可變為雪崩擊穿.根據這一特性, Liu等人通過優 化漂移層、p +-GaN層及溝槽柵極制備出了擊穿電壓為2783 V、比導通電阻為1.6 mΩ cm2的溝槽GaN MOS-FET。2.3基于原位氧化物氮化鎵夾層的垂直溝槽金屬氧化物半導體場效應晶體管 基于原位氧化物氮化鎵夾層的垂直溝槽金屬氧化物半導體場效應晶體管(in-situoxide GaN interlayerbased vertical trench MOSFET, GaN OG-FET)是基于傳統溝槽MOSFET在結構上改進而來的.與傳統的溝 槽MOSFET相比, OG-FET具有兩個特征: (1)使用非故 意摻雜(unintentional doping, UID)的GaN中間層作為溝 道區域,減少了摻雜劑的庫侖散射,增強了溝道電子遷 移率; (2)通過MOCVD原位生長氧化物,減緩了界面狀 態,提高了柵極氧化物的可靠性.因為溝槽MOSFET的 溝道是由干法蝕刻形成的,在蝕刻過程中,側壁上產生 的缺陷會導致反型溝道電子的場效應遷移率降低,從 而影響器件的性能. OG-FET的優勢就是增強溝道電子 遷移率而不會損害正常的常關行為。加州大學的Gupta等人針對干法蝕刻帶來的問 題,對“U”形MOSFET結構的形成提出了新的改進方法,通過MOCVD在柵介質和GaN之間生長一層薄的未摻 雜GaN中間層,隨后在n-p-n溝槽結構上進行MOCVD電 介質沉積,如圖4(a)所示.這使得器件的工作原理由pGaN產生反型層變成了非故意摻雜GaN(UID-GaN)的 積累,使得垂直溝槽GaN OG-FET中的漏極電流密度提 高.與傳統溝槽柵極MOSFET相比,該器件的比導通電 阻降低至3.8 mΩ cm2,閾值電壓為2 V,擊穿電壓為195 V. 2017年,他們利用低損傷柵極溝槽蝕刻和塊狀GaN襯底,制備出了擊穿電壓為990 V,導通電阻為2.6 mΩ cm2的OG-FET,并在沒有終端的情況下實現了1.6 MV/cm的高擊穿場強.同年,他們采用場板邊緣終 端結構使擊穿場強提高到2.0 MV/cm(~1000 V). Ji等人使用15 μm厚均勻摻雜的GaN漂移層,并采用雙 場板新型結構,如圖4(b)所示.該GaN OG-FET的溝道遷 移率為185 cm2/(V s),擊穿電壓為1435 V,比導通電阻 為2.2 mΩ cm2.他們在400 μm×500 μm的大面積上制 備了同樣的器件,擊穿電壓高達900 V,導通電阻為4.1 Ω. 2018年,他們制備了可實現1 A高輸出電流的大面積OG-FET。

UID-GaN中間層在經過MOCVD生長后,需要對pGaN掩埋層進行高溫退火,用于激活p-GaN層,這個過 程產生了高熱量預算,對器件幾何形狀的形成也會造 成限制.為了減少高熱量的預算, Li等人通過分子束 外延(MBE)形成一層UID-GaN溝道,形成了與OG-FET類似的結構,該結構的擊穿電壓為600 V左右,導通電 阻為0.3 Ω cm2. MBE再生長省去了激活p-GaN這一步 驟,改善了p-GaN的再鈍化問題,避免了后續的激活 步驟,并能夠提升溝道遷移率.任何功率器件在工作時都會產生熱量.在OG-FET內部,大部分熱量都集中在溝槽和GaN夾層附近.在實 際應用時,由于電池單元的緊密排列,相互之間會產生 熱串擾. Chatterjee等人通過分析OG-FET的內部電場 和發熱分布,提出可通過增加各單元間的間距和陣列 縱橫比,顯著降低了OG-FET單元陣列的峰值溫度。

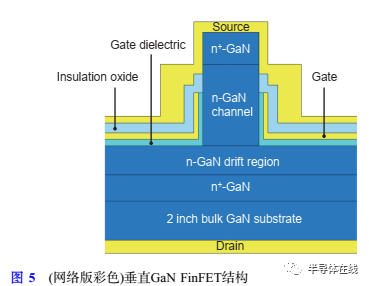

2.4垂直氮化鎵鰭式場效應晶體管 傳統的垂直溝槽GaN MOSFET已有著良好的性能 表現,但是在外延再生長以及p-GaN的需求方面,阻礙了垂直GaN功率晶體管的發展.不同于n-GaN, p-GaN具 有低的受主激活率以及較低的載流子遷移率, p-GaN的 外延再生長也很大程度地增加了器件制造的復雜性和 成本。1999年, Hu等人發明了鰭式場效應晶體管(fin field-effect transistor, FinFET),并在硅襯底上制備出一 種新型的自對準雙柵硅-絕緣體(silicon-on-insulator, SOI)結構的納米MOS器件,這種結構增大了柵極的控 制面積,提高了器件柵極的控制能力.隨著近幾年半導 體材料的發展,垂直GaN FinFET應運而生.相對于傳統 的溝槽MOSFETs, GaN FinFET的優勢是只需要n-GaN,不需要p-GaN層來提供正常關斷操作和關斷狀態下的 阻斷. FinFET的柵極由鰭側壁的電介質和柵極金屬組 成,因為柵極金屬和GaN之間的功函數差異,耗盡了鰭 片內的電荷載流子,從而提供了常關操作。對于FinFET,鰭的寬度需足夠窄(<500 nm)以用于 完全耗盡,這種結構會降低器件的電流能力.麻省理工 學院的Sun等人結合了干法、濕法蝕刻,制備出了平 滑的垂直鰭片,在GaN襯底上制備出具有亞微米級鰭 狀通道的GaN FinFET結構,如圖5所示,鰭寬度為450 nm.該器件具有1 V的閾值電壓、0.36 mΩ cm2的 比導通電阻及800 V擊穿電壓,且在積累層中獲得了150 cm2/(V s)的高電子遷移率.值得注意的是,不同于 溝槽MOSFET通過電子的反轉來工作, FinFET通過電 子的積累來運行. Zhang等人在此基礎上進一步優化 了鰭的寬度,將其降低至220 nm左右,獲得了1200 V的 高擊穿電壓和0.2 mΩ cm2低比導通電阻,并制備出具有10 A的電流能力和800 V擊穿電壓的大功率器件. 2018年, Zhang等人在0.45 mm2的大面積上制備出5 A的 電流能力及1200 V耐壓的垂直功率FinFET,其比導通 電阻為2.1 mΩ cm2,閾值電壓為1.3 V.與商用0.9~ 1.2 kV的Si和SiC功率晶體管相比,該器件表現出低的 輸入電容(CISS)、輸出電容(COSS)、柵極電荷(QG)、柵 極至漏極電荷(QGD)和反向恢復電荷(Qrr),以及高頻開 關能力和優異的開關品質因數(FOMs)。

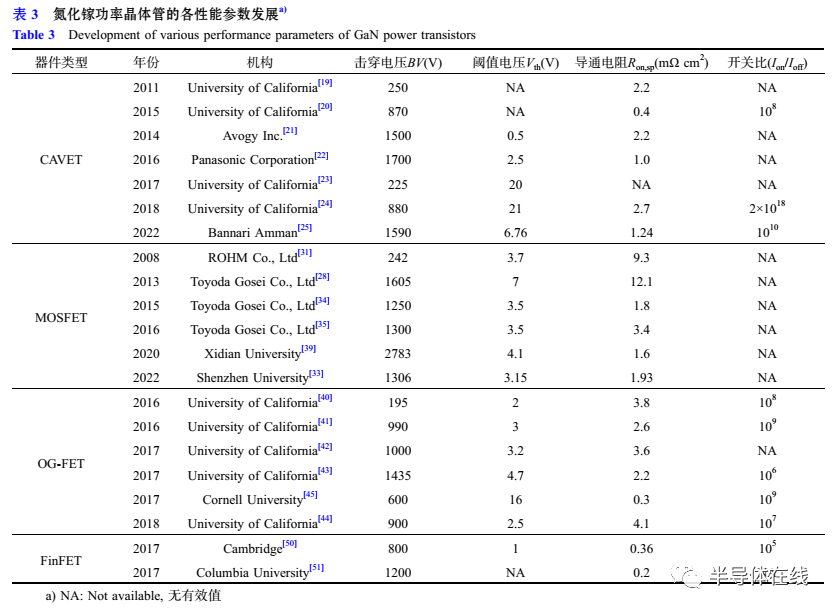

但是,缺少了p-GaN層來調節電場峰值,這些FinFET會發生不可逆轉的擊穿現象.有研究提出,在漂移 層中插入一層p基區來改善這類現象,但仍處于模擬 階段,尚未制備出實際的器件.與其他垂直器件相比, FinFET鰭的制造和寬度控制增加了工藝的復雜性,制 備成本較高; FinFET的閾值電壓相對較低(~1 V),因此 為確保設備能夠安全操作而不發生故障,對柵極驅動 器的設計有較高的要求.近年來, FinFET和基于垂直np-n疊層的納米絲(nanowire, NW)結構都實現了穩定的 常關操作,同時在3D疊層中集成p型層(基于納米 線或基于鰭式結構),使得器件在柵極施加應力的情況下仍能實現穩定常關操作。2.5總結與展望 表3列出了文中所提及的氮化鎵功率晶體管的參 數.早期的GaN功率器件朝著高耐壓、低導通電阻的 方向發展,不過隨著近幾年來集成電路的高速發展以 及GaN功率晶體管在中低壓范圍內的應用逐漸變多,為了順應市場發展與應用,對器件的閾值電壓(threshold voltage,Vt )與開關比(Ion/Ioff)也有著一定的要求,尤 其是電路及其集成系統的性能與Vt的大小和一致性有 著密切的關系.隨著未來芯片集成度越來越高,較高的 閾值電壓有利于提高電子元件的抗干擾能力.開關比 是指器件開啟和關斷的電流大小比值,反映器件對電 流的調控能力.針對未來GaN功率晶體管,可以從以下 幾個方面繼續努力: (1)由于GaN功率晶體管的實際應 用將主要集中在200及600~900 V的電壓范圍內,高耐 壓的需求將顯得不那么強烈,而是往低導通電阻、較 高的閾值電壓及高開關比發展; (2)研究GaN功率晶體 管在集成電路中的分布和優化布局,減少高密度的器 件布局之間所帶來的不良影響; (3)使用更好的散熱布 局和散熱材料,尤其是產熱量較高的位置,從而進一步 提高功率晶體管的性能和穩定工作時間.以上問題的 解決都可以有效地提高器件的安全性和可靠性,使得 器件或設備具有更長的使用壽命,從而更好地應用在 各個領域當中。

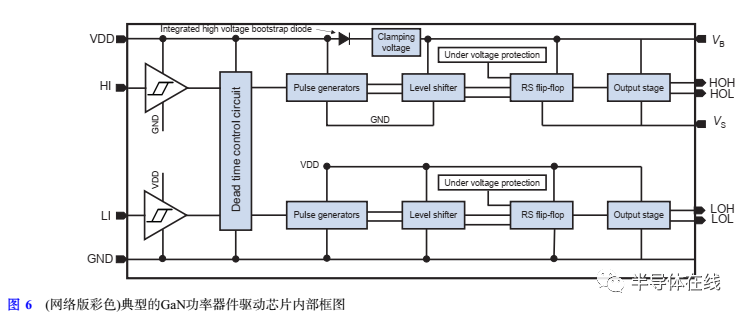

3氮化鎵驅動IC 圖6為典型的GaN功率器件驅動芯片的內部電路 框圖. GaN功率器件柵極驅動芯片可以接收來自中央 處理器(central processing unit, CPU)、微控制單元(microcontroller unit, MCU)等外部芯片的控制信號,并輸 出控制信號來控制GaN功率器件.與硅基MOSFET柵極 驅動芯片技術相比, GaN功率器件的柵極驅動電路有 以下3個要求: (1) GaN功率器件的開關頻率比現有硅基器件高10~100倍,芯片內部高低壓電路之間的隔離 區對信號傳輸電路的延遲要求極為嚴格.因此,需要設 計超高速隔離區信號傳輸技術和芯片架構. (2) GaN功 率器件的柵極電壓通常不超過6 V,對應的驅動電壓范 圍較窄.因此,驅動電路的輸出驅動電壓應具有更高的 精度和更高的抗干擾能力. (3) GaN功率器件的運行沒 有體二極管的反向恢復過程,但在死區時間內會有額 外的效率損失,需準確設置死區時間.對上述提及的3個要求, GaN功率器件驅動芯片的 關鍵技術分別對應為: (1)為匹配GaN功率器件的高頻 特性,誕生了低延遲高壓電平移位技術; (2)針對GaN基 器件柵極易擊穿的特點,提出了柵級過壓保護技術; (3)為了減少GaN功率器件反向傳導時存在的較大損耗,提出了自適應死區技術。

3.1高壓電平移位技術 高壓電平移位技術主要有: (1)電阻負載的電平移 位模式是最傳統的電平移位方式,需要RC濾波電路來 提高瞬時噪聲抑制的能力. (2)采用四管電容負載電 平移位電路,其基本原理是在瞬時噪聲信號到來時使 用共模檢測電路的輸出信號來屏蔽輸入信號. (3) VI-V電平移位技術,是Fairchild采用的核心技術,通過 將電平移位支路的輸出電壓轉化為電流信號,然后進 行共模比較,最后轉化為電壓信號輸出,可有效抑制共 模噪聲的干擾。3.2柵極過壓保護技術 為實現輸出級鉗位,避免GaN器件柵源電壓過大 而損壞,主流的柵極過壓保護技術有: (1)齊納鉗位技 術,這是一種結構相對簡單的鉗位技術.利用其反向 傳導齊納鉗位原理,將高壓側電源電壓鉗位在能夠安 全驅動E-mode GaN功率器件的電壓范圍內,用于實現E-mode GaN驅動芯片高側可靠性供電功能. (2)高壓側 輸出級電壓預調節技術,該技術是在集成自舉之后,增 加了一個低壓差線性穩壓器(low dropout regulator, LDO)來穩定GaN功率器件柵極電壓,該方案可有效地 控制驅動芯片的輸出電壓. (3)通過高壓側過壓比較 電路來控制集成自舉供電,實現低功耗的輸出級鉗位 技術.它是通過實時監測輸出電壓的大小,控制集成自 舉供電通路的通斷,從而達到輸出級鉗位的目的。

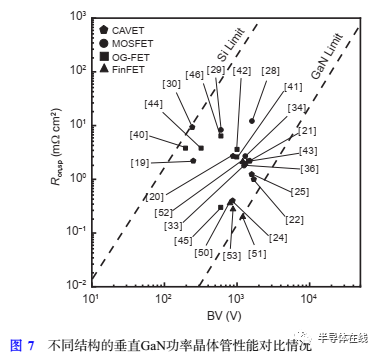

3.3自適應死區技術 自適應死區技術主要分為3種形式: (1)采用VS電 壓檢測的方式來判斷功率管的開/關,通過高壓二極管 檢測VS端的負壓,可以運用于上管關閉后,下管開通前 的死區控制; (2)采用高低壓側柵級電壓檢測的方式,高低壓側柵極信號相互影響,當低壓側GaN器件柵信 號為高時,不開啟高壓側功率管,反之亦然. (3)通 過檢測GaN功率器件開關瞬間的柵漏電荷變化量來控 制死區時間,這需要靈敏度較高的檢測單元。4總結與應用 GaN作為第三代寬禁帶半導體,有著相較于前兩 代半導體更優越的性能. GaN基晶體管的出現解決了Si基晶體管所面臨的很多問題.本文敘述了GaN材料參 數、GaN單晶襯底及其外延生長的方法,對比了橫向器件和垂直器件并解釋了選擇垂直結構的原因,同時 介紹了CAVET、Trench GaN MOSFET、OG-FET和GaN FinFET的發展情況以及氮化鎵驅動IC的關鍵技 術.圖7匯總了文中所提到的晶體管對擊穿電壓(breakdown voltage,BV)/比導通電阻(Ron,sp)的情況,可以發 現,這些器件不僅比Si基功率器件性能更好,同時也在 逐漸接近GaN材料極限發展.垂直GaN三極管可以應用 在很多領域當中,尤其是中、低壓的場景下.下面主要 介紹幾種目前比較熱門的方向。

(1)充電器及適配器.不同于十幾年前電腦的適配 器及手機的“5 V×1 A”,目前市場上很多電子產品都使 用了快充技術,小至45 W,大至250 W,再加上人們對便 捷性的追求,大功率密度、高工作溫度和小體積等成 為了目前充電器的發展目標.與目前普遍的Si基充電 器相比, GaN基充電器在滿足功率密度的條件下可以 實現更好的散熱、更高的工溫度和更小的體積.目前 市場上已經出現了GaN充電器的“身影”,不僅體積比 傳統手機、電腦充電器小得多,在充電速度和散熱方 面也有著非常不錯的表現。(2)無線通信技術.隨著5G技術的發展,通信設備 對大功率、高頻率、高速度的性能需求更加急切, GaN材料本身就已經具有這些物理性能,且GaN功率晶 體管在滿足以上要求的情況下,在散熱、體積及功耗 方面也有著較大的優勢,可進一步提升電子產品的性 能,獲得更好的通信體驗。(3)無線充電器.無線充電目前也是一項熱門且快 速發展的技術,各家手機廠商的旗艦機幾乎都適配了 無線充電技術,甚至在電動汽車上也有它的“身影”.無 線充電的頻率大致在100 kHz~6.78 MHz范圍內,這對 充電設備在溫度控制、轉換頻率和大功率等方面有著 較高的要求,尤其是給電動汽車這種大型工具進行無 線充電,對充電設備的要求會更高。 (4)汽車應用. GaN功率器件的發展,最大的受益者 之一便是汽車的電氣系統,主要應用在車載充電器(onboard charger, OBC)、DC-DC轉換器、電機驅動器和 激光雷達.目前汽車電池的電壓范圍為600~1500 V,對 器件有高耐壓、大電流和快速開關的要求,而垂直GaN晶體管的發展使得汽車電氣系統具有更簡單靈活 的設計和更高的性能。 (5)大規模集成電路.目前的硅基器件已經逼近Si材料的理論極限,對高壓高頻大功率的需求卻在不斷 增加,硅基器件在體積和散熱方面有很多的問題,不利 于后續大規模集成電路的發展.而GaN材料不僅在物 理性能上比硅材料更有優勢,在相同性能的情況下,制備出的晶體管體積可以大幅度減小,配合使用小型 散熱器,可以大幅度解決集成電路在體積和散熱方面 上的問題,并擁有更高的開關頻率,可提高設備的性能。來源:科學通報作者:李博1?, 尹越2?, 陽志超3, 劉新科1*, 李京波4*

-

集成電路

+關注

關注

5391文章

11595瀏覽量

362580 -

晶體管

+關注

關注

77文章

9723瀏覽量

138620 -

氮化鎵

+關注

關注

59文章

1644瀏覽量

116491

發布評論請先 登錄

相關推薦

氮化鎵充電器和普通充電器有啥區別?

日本開發出用于垂直晶體管的8英寸氮化鎵單晶晶圓

供應SW1108P集成氮化鎵直驅的高頻準諧振IC

供應SW1102集成氮化鎵直驅的準諧振模式反激控制IC

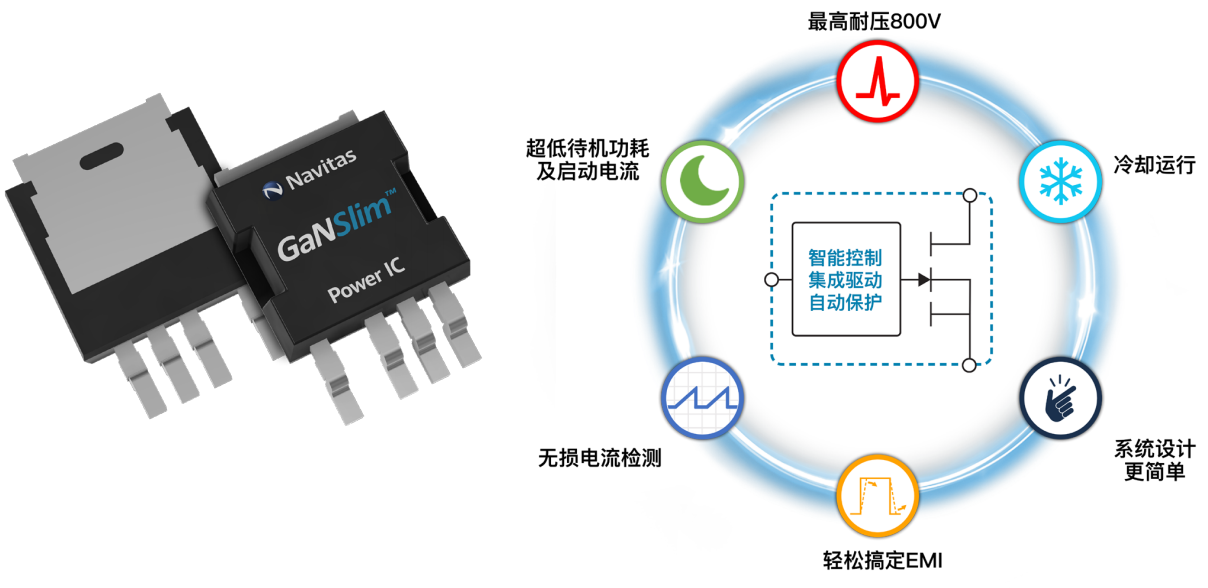

集成之巔,易用至極!納微發布全新GaNSlim?氮化鎵功率芯片

GaN晶體管和SiC晶體管有什么不同

GaN晶體管的基本結構和性能優勢

Transphorm攜手偉詮電子推出兩款新型系統級封裝氮化鎵器件

Transphorm與偉詮電子合作推出新款集成型SiP氮化鎵器件

氮化鎵(GaN)功率集成電路(IC)開發的優勢與挑戰

晶體管和集成電路是什么關系?

氮化鎵功率晶體管及其集成電路的發展狀況

氮化鎵功率晶體管及其集成電路的發展狀況

評論