一年一度的 DesignCon 是世界一流的高速通信和系統(tǒng)設(shè)計(jì)大會(huì),在電子創(chuàng)新的核心硅谷匯集行業(yè)關(guān)鍵的技術(shù)發(fā)展與碰撞。在前不久剛剛落幕的2023 DesignCon 大會(huì)上,共有兩場(chǎng)主題演講,其中一場(chǎng)來自 Cadence 的多物理場(chǎng)系統(tǒng)分析事業(yè)部研發(fā)副總裁 Ben Gu,題為《設(shè)計(jì)智能機(jī)器的智能工具(The Intelligence to Design Intelligent Machines)》;另一場(chǎng)來自 Boston Dynamics 的 Devin Billings,關(guān)于這一場(chǎng)的主題演講解讀,我們將在下周與大家分享。

《設(shè)計(jì)智能機(jī)器的智能工具》主題演講開篇提到了人類發(fā)展的歷史。起初是純粹憑借蠻力;然后人類開始用大腦思考并制作工具,從石頭工具、青銅工具,發(fā)展到鐵制工具;最終,我們學(xué)會(huì)了利用機(jī)器的力量,例如挖掘機(jī)和拖拉機(jī);之后,機(jī)器也有了自己的大腦:性能越來越強(qiáng)大的計(jì)算機(jī);現(xiàn)在,我們有了性能足夠強(qiáng)大的計(jì)算機(jī),可以使人工智能變?yōu)楝F(xiàn)實(shí)。幾十年來,人工智能的基本構(gòu)思并沒有發(fā)生太大的變化,但因?yàn)楝F(xiàn)在擁有了性能強(qiáng)勁的 CPU 和 GPU,這些想法終于可以付諸實(shí)踐。

之后,Ben 講到了智能系統(tǒng)設(shè)計(jì)中的人工智能。目前,有些人害怕人工智能會(huì)取代人類,也有些人看到了機(jī)遇——人工智能有助于提高人類的生產(chǎn)力。對(duì)此,我們的基本預(yù)期是:這項(xiàng)技術(shù)將發(fā)揮積極作用,幫助我們獲得更好的 PPA 結(jié)果、更好的設(shè)計(jì)收斂、更快的設(shè)計(jì)周期等等。

幾十年來,EDA 一直是設(shè)計(jì)師提高生產(chǎn)力的得力助手。早在平面集成電路首次問世時(shí),手動(dòng)設(shè)計(jì)流程非常繁瑣。需要將設(shè)計(jì)繪制成圖紙,而制作掩膜則需要切割紅寶石,整個(gè)制造過程就像手工制作陶器一樣復(fù)雜。然后出現(xiàn)了晶體管級(jí)設(shè)計(jì),采用 Calma GDSII 和 SPICE(或類似 SPICE)電路仿真多邊形 layout 編輯器。這使生產(chǎn)力提升了一個(gè)數(shù)量級(jí)。隨后,出現(xiàn)了基于單元的設(shè)計(jì),這種流程基于綜合和自動(dòng)放置及布線,又一次使設(shè)計(jì)生產(chǎn)力提升了一個(gè)數(shù)量級(jí)。相信每個(gè)人都期待用于描述設(shè)計(jì)的語言可以變得更加抽象,但這從始至終都沒有發(fā)生。生產(chǎn)力的又一次階段性提升歸功于可重復(fù)使用的模塊:在公司內(nèi)部,這種方法被稱為“設(shè)計(jì)重用”;而當(dāng)一家公司創(chuàng)建可重復(fù)使用的模塊,供另一家公司進(jìn)行部署時(shí),這被稱為“IP”。基于人工智能的 EDA 無疑將掀起另一次生產(chǎn)力提升熱潮。

接下來,Ben談到了針對(duì)基于人工智能的 EDA,Cadence 所涉及的領(lǐng)域,但限于 DesignCon 的演講規(guī)則,他沒有提及太多產(chǎn)品名稱——

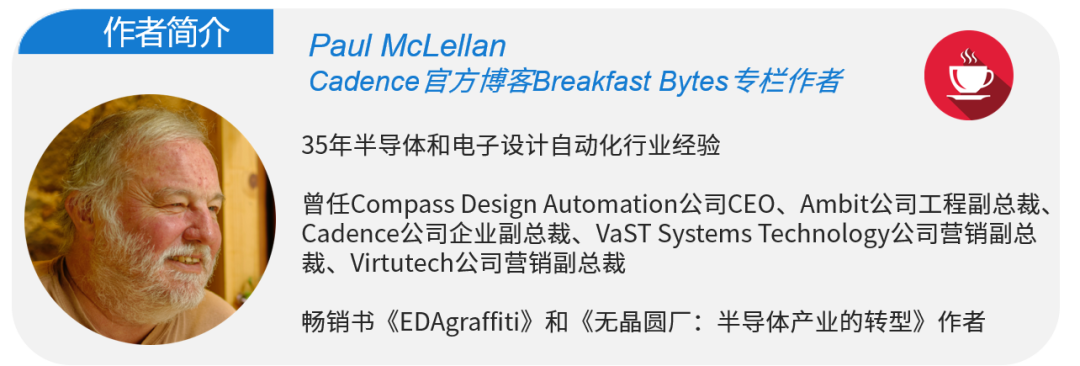

例1:調(diào)試 SoC 驗(yàn)證故障

Cadence Verisium 工具專注于這一領(lǐng)域,包括對(duì)重要故障進(jìn)行優(yōu)先級(jí)排序、跟蹤錯(cuò)誤、找到根本原因,并修復(fù)問題(在充分理解問題之后,這一步通常最為簡(jiǎn)單)。

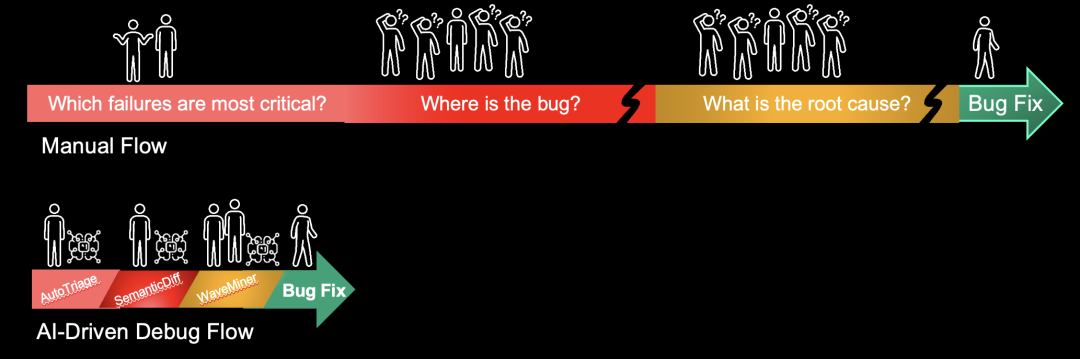

例2:數(shù)字全流程

Cadence Cerebrus 工具可以更快更好地得出結(jié)果(演講中并未提及該產(chǎn)品名稱)。工程師采用之前的方法需要耗時(shí)幾個(gè)月之久,借助 Cadence Cerebrus,一名工程師只需十天就可以將 PPA 改善 20%。這大大節(jié)省了設(shè)計(jì)時(shí)間。即便 PPA 沒有改善,從幾個(gè)月變成十天也會(huì)產(chǎn)生很大影響。退一步說,即便花費(fèi)的時(shí)間相同,依然需要幾個(gè)月之久,PPA 提高 20% 也是一種飛躍。

而做到既節(jié)省時(shí)間,又改善結(jié)果,這種兩全其美的優(yōu)勢(shì)勢(shì)必會(huì)讓公司在競(jìng)爭(zhēng)中一騎絕塵。

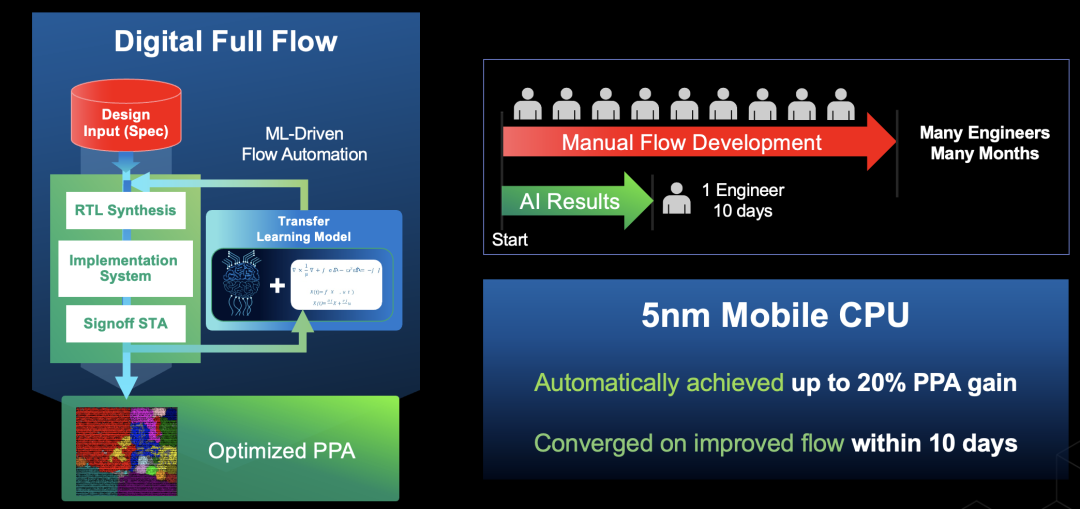

例3:高性能 GPU

請(qǐng)注意,上圖中的生產(chǎn)力提升幅度不是 5%,而是 5 倍。降低的功耗也非常可觀。在電池供電的設(shè)備中,芯片漏電問題改善了 28.5%,待機(jī)時(shí)間得以顯著延長(zhǎng)(例如,手機(jī)開機(jī)但未使用,可以隨時(shí)接聽來電或接收短信)。

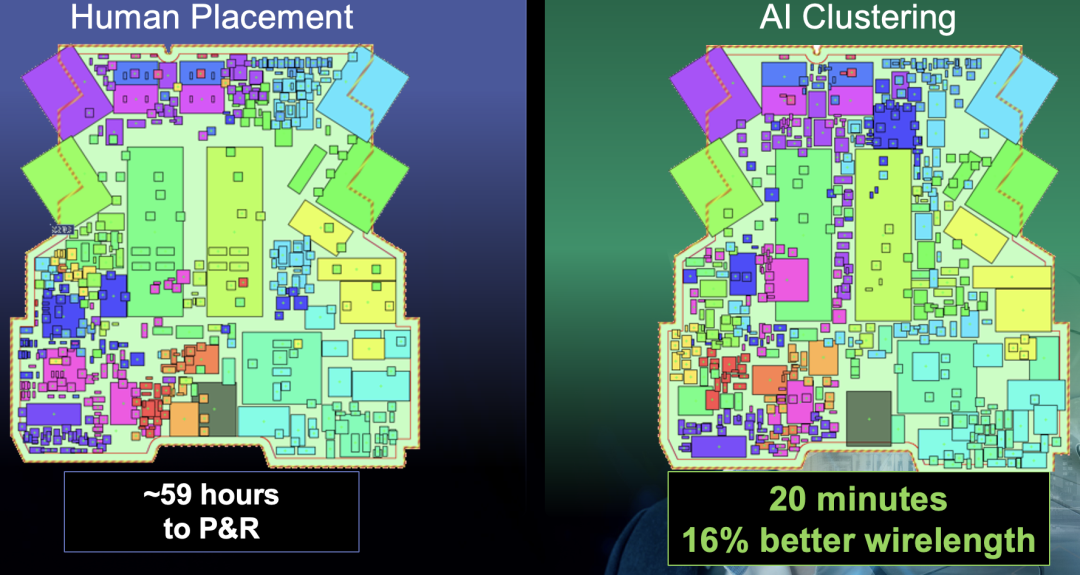

例4:PCB 布線

這是個(gè)截然不同的領(lǐng)域,同樣,生產(chǎn)力大幅提高——從50 小時(shí)縮短到 20 分鐘,相當(dāng)于速度提高 150 倍,PCB 走線線路長(zhǎng)度也同時(shí)減少了 16%。

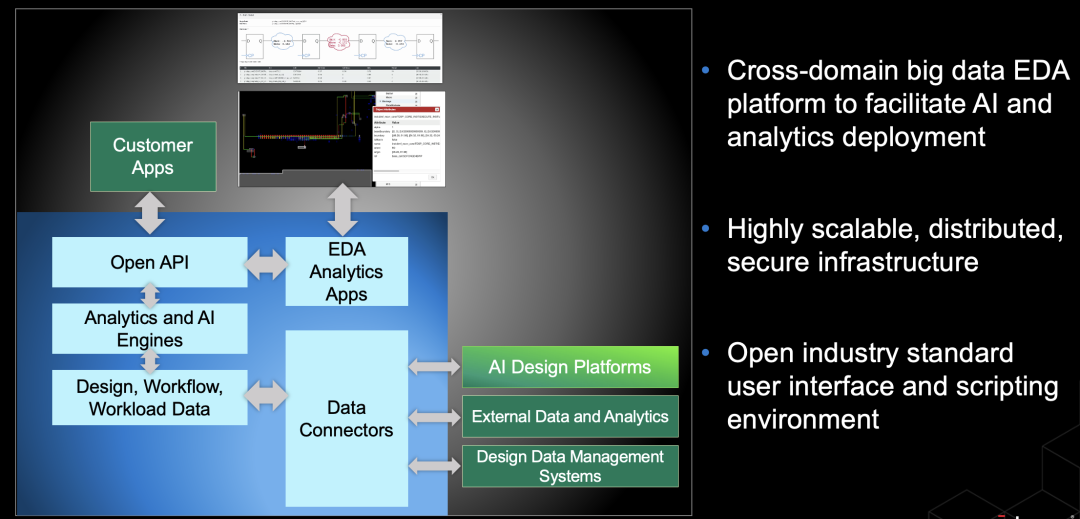

這些技術(shù)(以及 Ben 談到的和因?yàn)闀r(shí)間有限而沒有談到的其他技術(shù))背后的關(guān)鍵技術(shù)都是數(shù)據(jù)平臺(tái),即 Cadence Joint Enterprise Data and AI (JedAI) Platform。這是一個(gè)基礎(chǔ)人工智能平臺(tái),它之所以能夠提供最佳結(jié)果,是因?yàn)樗泄ぞ叨紵o縫協(xié)作,并基于相同數(shù)據(jù)進(jìn)行了訓(xùn)練。

一言以蔽之,人工智能正在改變一切,在提高生產(chǎn)力的同時(shí)也能夠提供更好的結(jié)果。但這一切只是開始。現(xiàn)代人工智能時(shí)代的開啟有一個(gè)非常明確的日期,即 2012 年 ImageNet 大規(guī)模視覺識(shí)別挑戰(zhàn)賽。在這場(chǎng)圖片識(shí)別競(jìng)賽中,神經(jīng)網(wǎng)絡(luò)方法戰(zhàn)勝了算法方法,因此也被稱為“Imagenet 時(shí)刻”。但這只發(fā)生在十多年前。從那以后,EDA 算法(以及 Ben 主題演講或這篇文章未涉及的許多其他領(lǐng)域)方法迎來了天翻地覆的變化。

Cadence Optimality Intelligent System Explorer,使用人工智能和機(jī)器學(xué)習(xí)技術(shù) (AI/ML) 來自動(dòng)指導(dǎo)優(yōu)化,使電子系統(tǒng)的多學(xué)科分析和優(yōu)化(MDAO)得以實(shí)現(xiàn)。

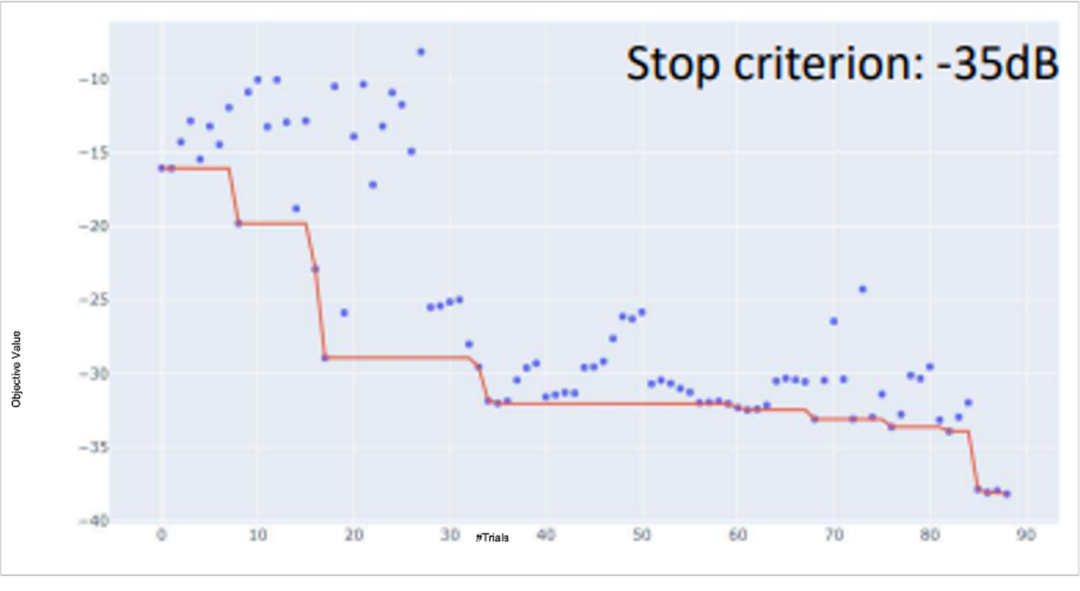

首批搭載這一新型優(yōu)化技術(shù)的產(chǎn)品是 Sigrity X 和 Clarity 3D Solver 求解器。Optimality Explorer 可以決定在迭代期間改變什么,也可以決定何時(shí)結(jié)束優(yōu)化。設(shè)計(jì)師定義要優(yōu)化的參數(shù),例如回波損耗小于某個(gè)期望的閾值。然后 Optimality Explorer 直接從 Allegro 平臺(tái)獲取設(shè)計(jì)數(shù)據(jù),生成設(shè)計(jì)變量,指導(dǎo)優(yōu)化,并自動(dòng)結(jié)束優(yōu)化。

上圖中,Optimality Explorer 在一個(gè)解上進(jìn)行收斂,一旦目標(biāo)值下降到 -35dB 以下就會(huì)退出。與傳統(tǒng)的人工方法相比,Optimality Explorer 完成設(shè)計(jì)的優(yōu)化要快上10 倍(或更多)。

-

機(jī)器

+關(guān)注

關(guān)注

0文章

782瀏覽量

40729 -

智能工具

+關(guān)注

關(guān)注

0文章

14瀏覽量

2346

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【「具身智能機(jī)器人系統(tǒng)」閱讀體驗(yàn)】+初品的體驗(yàn)

《具身智能機(jī)器人系統(tǒng)》第1-6章閱讀心得之具身智能機(jī)器人系統(tǒng)背景知識(shí)與基礎(chǔ)模塊

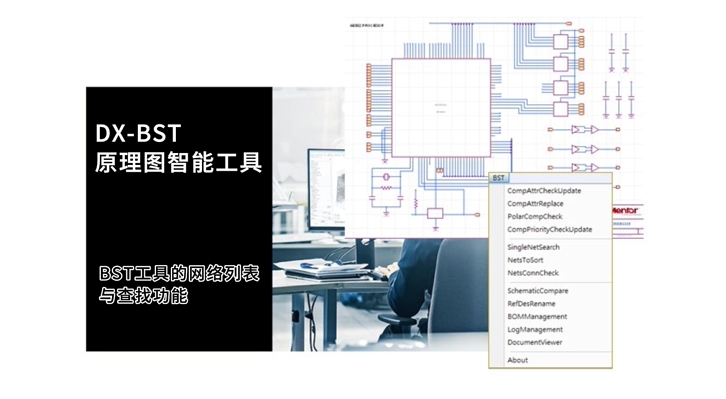

貝思科爾DX-BST原理圖智能工具,限時(shí)免費(fèi)試用開啟,不容錯(cuò)過!

【書籍評(píng)測(cè)活動(dòng)NO.51】具身智能機(jī)器人系統(tǒng) | 了解AI的下一個(gè)浪潮!

Cognex推出由人工智能(AI)驅(qū)動(dòng)的In-Sight SnAPP視覺感測(cè)器計(jì)數(shù)工具

Intel的AI Playground入門級(jí)人工智能工具亮相

DX-BST原理圖智能工具:有效提高設(shè)計(jì)效率并實(shí)現(xiàn)設(shè)計(jì)管理的智能解決方案

利用DX-BST原理圖智能工具實(shí)現(xiàn)原理圖對(duì)比的技術(shù)方法

DX-BST原理圖智能工具

XL-BST PCB LAYOUT智能工具

XL-BST PCB LAYOUT智能工具產(chǎn)品概述

智能工具柜-RFID智能工具柜管理系統(tǒng)

關(guān)于生成式人工智能你應(yīng)該知道的7件事

DesignCon解讀 I 設(shè)計(jì)智能機(jī)器的智能工具

DesignCon解讀 I 設(shè)計(jì)智能機(jī)器的智能工具

評(píng)論