ESD(Electrostatic Discharge)測(cè)試,即靜電放電測(cè)試,是所有電子設(shè)備必須要通過(guò)的測(cè)試,其目的是仿真操作人員或物體在接觸設(shè)備時(shí)產(chǎn)生的放電以及人或物體對(duì)鄰近物體之放電,以檢測(cè)被測(cè)設(shè)備抵抗靜電放電之干擾能力。

比較通用的一個(gè)測(cè)試標(biāo)準(zhǔn)是國(guó)際電工委員會(huì)(IEC)于1995年制定的 IEC 61000-4-2。

IEC 61000-4-2定義,ESD分為直接放電和間接放電。

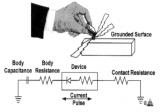

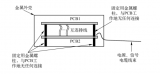

直接放電,即利用放電點(diǎn)擊直接對(duì)受試設(shè)備實(shí)施放電,其中又分為接觸放電(Contact Discharge)和空氣放電(Air Discharge)。

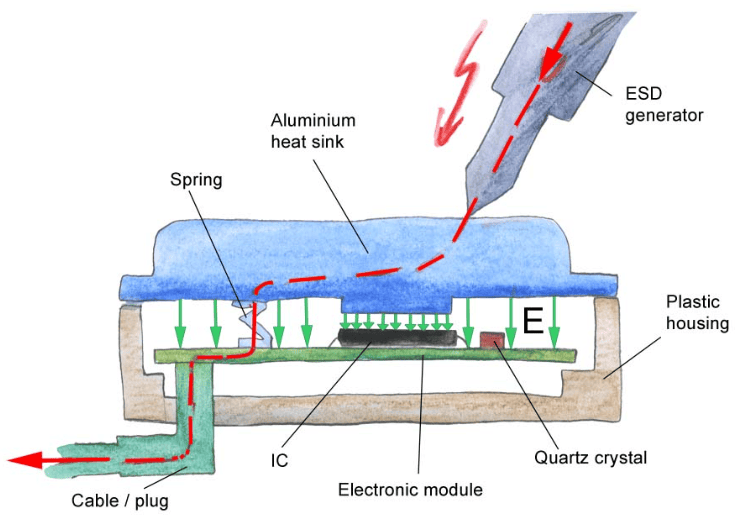

間接放電,即對(duì)受試設(shè)備附近的耦合板實(shí)施放電,以模擬人體對(duì)受試設(shè)備附近的物體的放電。

淘晶馳電子生產(chǎn)的串口屏通過(guò)ESD測(cè)試IEC 61000-4-2:2001的標(biāo)準(zhǔn)。有更高需求的客戶(hù)也可定制更高標(biāo)準(zhǔn)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀(guān)點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

相關(guān)推薦

測(cè)量對(duì)于確定IC的EMC特性是必要的。只有準(zhǔn)確了解IC的EMC特性,才能在生產(chǎn)前采取有效的預(yù)防措施,提高產(chǎn)品的抗ESD能力和EMC性能,避免后期因ESD干擾導(dǎo)致的產(chǎn)品故障和成本增加等問(wèn)題集成電路ESD

![的頭像]() 發(fā)表于

發(fā)表于 12-23 09:53

?386次閱讀

ESD

安泰小課堂

發(fā)布于 :2024年12月20日 18:14:00

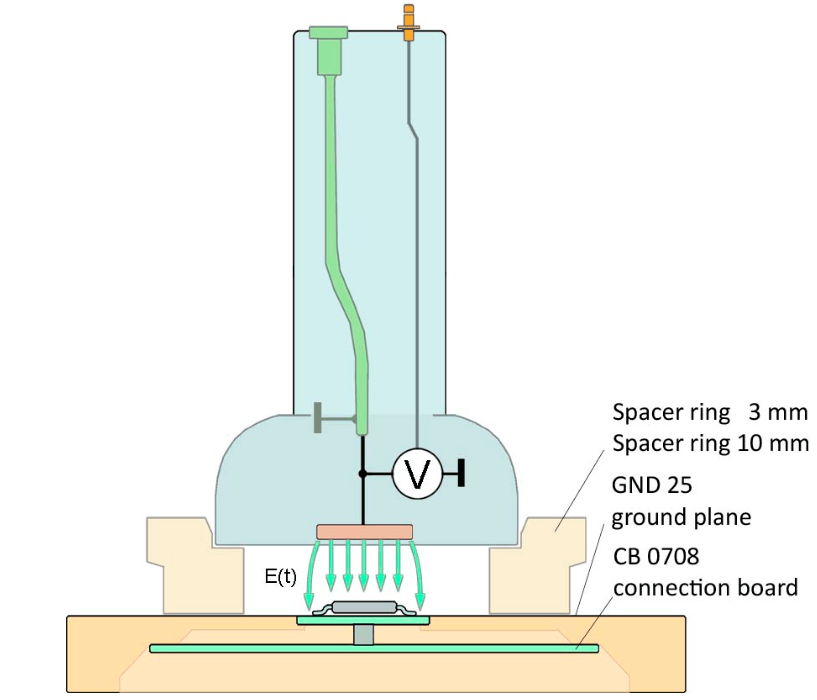

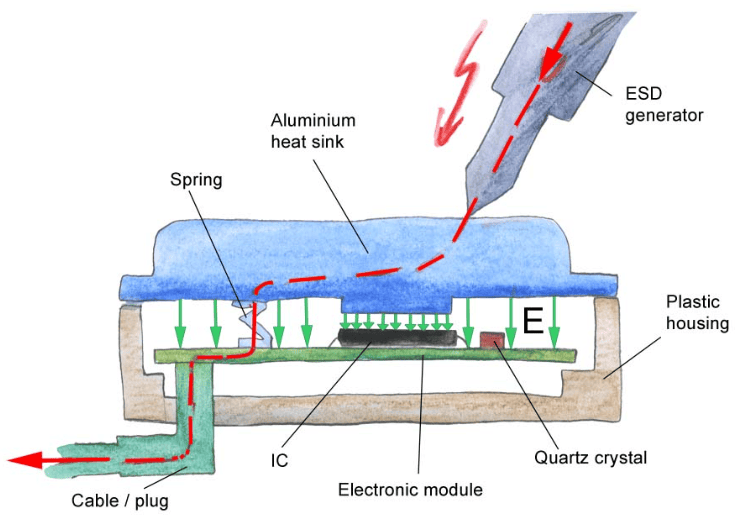

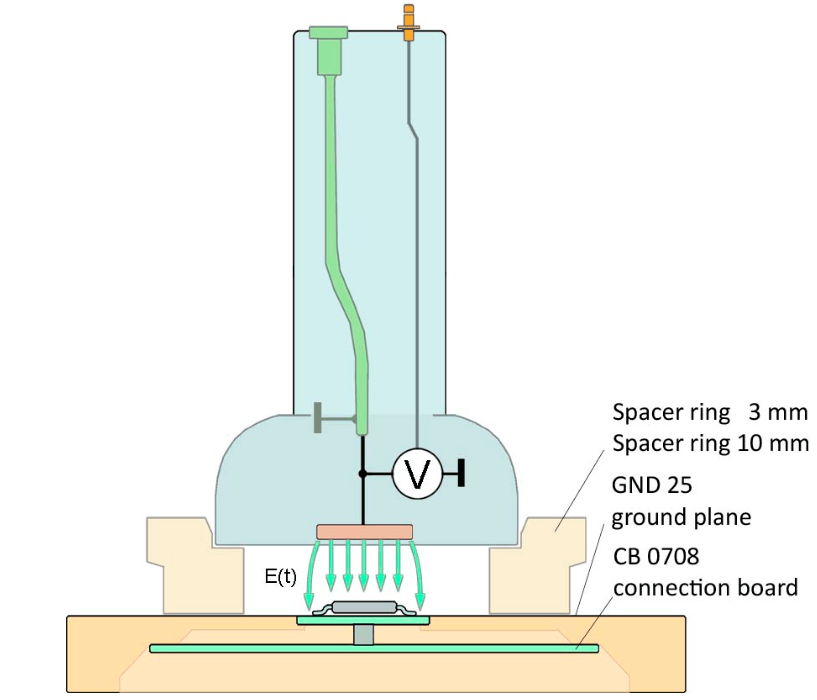

和成本增加等問(wèn)題 。 三、集成電路ESD 測(cè)試與分析 1、測(cè)試環(huán)境與電場(chǎng)產(chǎn)生 圖5 使用 ESD 發(fā)生器的測(cè)量設(shè)置l 測(cè)試環(huán)境,集成電路(I

![的頭像]() 發(fā)表于

發(fā)表于 12-20 09:14

?230次閱讀

此專(zhuān)題將從三個(gè)方面來(lái)分享:一、電子系統(tǒng)性能要求與ESD問(wèn)題二、集成電路ESD問(wèn)題應(yīng)對(duì)措施三、集成電路ESD測(cè)試與分析工業(yè)、消費(fèi)及汽車(chē)電子模塊開(kāi)發(fā)的EMC問(wèn)題會(huì)導(dǎo)致極高的開(kāi)發(fā)成本和時(shí)間浪

![的頭像]() 發(fā)表于

發(fā)表于 12-19 18:51

?306次閱讀

在電子領(lǐng)域,有一個(gè)常常被忽視卻又可能帶來(lái)巨大危害的“隱形殺手”——ESD(Electrostatic Discharge,靜電放電)。靜電放電產(chǎn)生的瞬時(shí)高電壓和大電流可能會(huì)直接損壞電子元件,使其失去

![的頭像]() 發(fā)表于

發(fā)表于 12-18 14:16

?515次閱讀

此專(zhuān)題將從三個(gè)方面來(lái)分享: 一、電子系統(tǒng)性能要求與ESD問(wèn)題 二、集成電路ESD問(wèn)題應(yīng)對(duì)措施 三、集成電路ESD 測(cè)試與分析 工業(yè)、消費(fèi)及汽車(chē)電子模塊開(kāi)發(fā)的 EMC 問(wèn)題會(huì)導(dǎo)致極高的開(kāi)

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:24

?194次閱讀

靜電放電(ESD)是指由于靜電積累而產(chǎn)生的電荷突然釋放現(xiàn)象。在電子制造和使用過(guò)程中,ESD可能會(huì)導(dǎo)致器件損壞、性能下降甚至系統(tǒng)故障。 ESD測(cè)試的重要性 保護(hù)電子設(shè)備 :通過(guò)

![的頭像]() 發(fā)表于

發(fā)表于 11-14 11:18

?1261次閱讀

在現(xiàn)代電子制造領(lǐng)域,靜電放電(ESD)是一個(gè)不可忽視的問(wèn)題。ESD可能導(dǎo)致設(shè)備性能下降、數(shù)據(jù)丟失甚至設(shè)備損壞。因此,對(duì)電子設(shè)備進(jìn)行ESD測(cè)試是確保其在實(shí)際使用中能夠抵抗靜電干擾的重要環(huán)

![的頭像]() 發(fā)表于

發(fā)表于 11-14 11:10

?594次閱讀

ESD測(cè)試,即靜電放電測(cè)試(Electrostatic Discharge Testing),是一種用于評(píng)估電子設(shè)備或組件在靜電放電環(huán)境下的性能穩(wěn)定性和可靠性的測(cè)試方法。以下是關(guān)于

![的頭像]() 發(fā)表于

發(fā)表于 09-09 18:17

?570次閱讀

(0.32V-0.24V);

請(qǐng)問(wèn):一般來(lái)說(shuō)這兩Pin的電壓差多少合適 以及 這么小的電壓差會(huì)不會(huì)存在什么異常(比如ESD測(cè)試時(shí)導(dǎo)致其輸出截然相反);

發(fā)表于 07-31 08:17

放電的模型。4 kV HBM ESD容差意味著該器件在模擬人體模型靜電放電測(cè)試中能夠承受最高4千伏的靜電放電,而不會(huì)損壞或失效。 具體解釋 HBM(Human Body Model):HBM是一種

![的頭像]() 發(fā)表于

發(fā)表于 07-10 11:30

?1.1w次閱讀

的成本。而潛在性損傷指的是器件部分被損,功能尚未喪失,且在生產(chǎn)過(guò)程的檢測(cè)中不能發(fā)現(xiàn),但在使用當(dāng)中會(huì)使產(chǎn)品變得不穩(wěn)定,時(shí)好時(shí)壞,因而對(duì)產(chǎn)品質(zhì)量構(gòu)成更大的危害。

ESD測(cè)試相關(guān)

常見(jiàn)的靜電耦合途徑:空氣

發(fā)表于 06-04 07:22

圖中有兩條ESD共模干擾路徑,即圖中左邊ICM1所在路徑和右邊ICM2路徑。

很明顯,第二條干擾路徑才是ESD測(cè)試不通過(guò)的主要原因。

發(fā)表于 03-05 10:28

?2469次閱讀

LED的反向漏電流(Ir)偏移量超過(guò)ESD測(cè)試前測(cè)量值的10倍。這也是判斷LED是否受到靜電擊穿的一個(gè)指標(biāo)。

發(fā)表于 02-18 12:28

?2065次閱讀

NUC972 USB做ESD測(cè)試時(shí)如何防護(hù)

發(fā)表于 01-17 07:32

ESD測(cè)試是什么?

ESD測(cè)試是什么?

評(píng)論