本課程基于 Cadence Allegro PCB 最新版本 Allegro X 進行 RK3588 實例項目設計,是一個完整的項目設計過程,力求通過實例項目的操作演示,將軟件新的功能和技巧融入到工程師的設計中去,減少項目冗余設計,加速項目的快速交付。

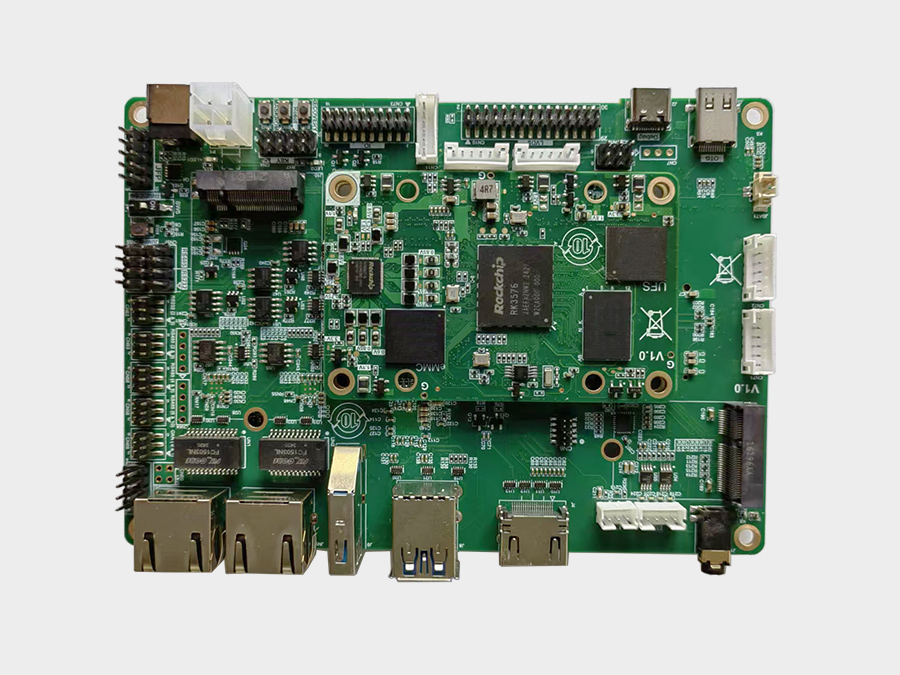

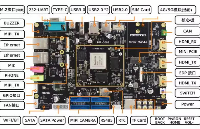

課程采用了 RK3588 芯片為核心基礎的硬件設計,對系統的片上資源,接口電路設計包括 RK3588 時鐘系統、供電系統、LPDDR4、SLASH、SD卡、USB3.0、MIPI、PCIE3.0、ADC、PMIC、DP 電路。對芯片外圍擴展各種常用的外設資源包括支持LPDDR4X、eMMC存儲、USB3.0、網卡、WIFI、HDMI、MIPI、VGA、SATA等10余個外設接口進行設計與分析。

01

課程特點

全網最新工具

Cadence Allegro 軟件提供完整原理圖和 PCB 設計解決方案,可實現原理圖與 PCB 布局無縫雙向集成,實現實時數據同步和高效的電路板設計環境。

最新版本 Allegro X 的功能更加適應高速高密、剛柔結合、背鉆異形槽孔設計等。

實例貼合

本課程所使用的 RK3588 芯片采用 8nm 制程工藝,四核 ARM Corte A76+四核 ARM Corte A55 CPU、內置 6Tops 獨立 NPU、運用 RK806-2 雙PMIC供電方案、支持 LPDDR4X/eMMC 存儲,擁有HDMI、MIPI、VGA、SATA等10余個外設接口,具有高集成度、強大性能和擴展能力。

涵蓋設計全流程

PCB設計——

依托實例項目演示 Allegro X 的最新功能及設計技巧,對元件封裝設計、表貼插件埋入元件封裝設計的處理、異形 PCB 板框處理、從原理圖一鍵同步到 PCB 中的辦法和技巧,規則驅動設計的思路及辦法、從高速 PCB 設計中的規則設置、約束技巧,模塊電路的同步與布局的技巧,總結模塊電路的同步、布局和區域布局的規劃,高速信號群組布線、差分信號布線技巧、信號延遲控制及合規性約束,信號繞線和常用的繞線優缺點分析總結,RK3588實例項目PCB設計的總結、生產文件的輸出和各種錯誤的檢查處理,進行了完整的功能和設計技巧講解。

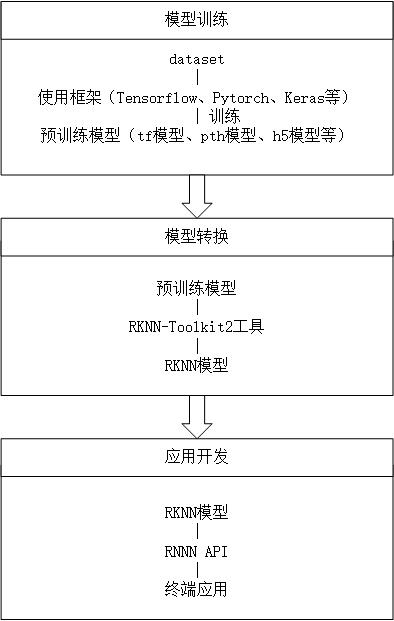

仿真分析——

使用 Sigrity Aurora 軟件對基于 RK3588 實例項目進行互連仿真分析。對 LPDDR4 部分的電路進行阻抗和寄生 LRGC 參數分析,對傳輸線的寄生參數進行仿真、優化和檢查,從約束規則驅動設計,到設計回歸檢查優化。對阻抗和寄生仿真分析,串擾分析及優化,信號拓撲提取與眼圖分析,信號互連傳輸線 S參數 建模等方法進行講解。

02

適合人群

課程難度:中等

適合需要處理復雜設計、希望精進技能,了解更多最佳實踐經驗的 PCB 工程師、硬件工程師、系統設計師

擁有一定知識基礎,希望提升實操經驗、快速成長,更好適應職場的學生和電子技術工程師

03

課程講師

李增

耀創科技Cadence 系列課程資深技術經理

畢業于電子科技大學,13+年模擬電路和數字電路及程序設計經驗,著有多本 Cadence 和高速信號仿真書籍

具有深厚信號仿真功底,熟悉模擬電路和數字電路及程序設計,一直從事電子類產品設計開發工作;多次帶領團隊獨立完成開發項目,并成功上市商用產品

在長期開發中積累了豐富的實戰經驗,從2016年開始,多次推出 Cadence 系列培訓課程,受到學員廣泛好評

04

課程形式

每月3期(共15期)實例操作視頻錄播

本微信公眾號和同名嗶哩嗶哩賬號【Cadence楷登PCB及封裝】同步推送

每月1期(共5期)總結答疑直播

本微信公眾號報名、觀看

05

課程福利

免費參與

每月1次網絡直播 + 精品高清錄播視頻無限次回放

免費下載

設計實例 + 講義資料

在線答疑

直播互動、后臺留言,主講人權威答疑解惑

更有不定期抽獎活動等著你!

06

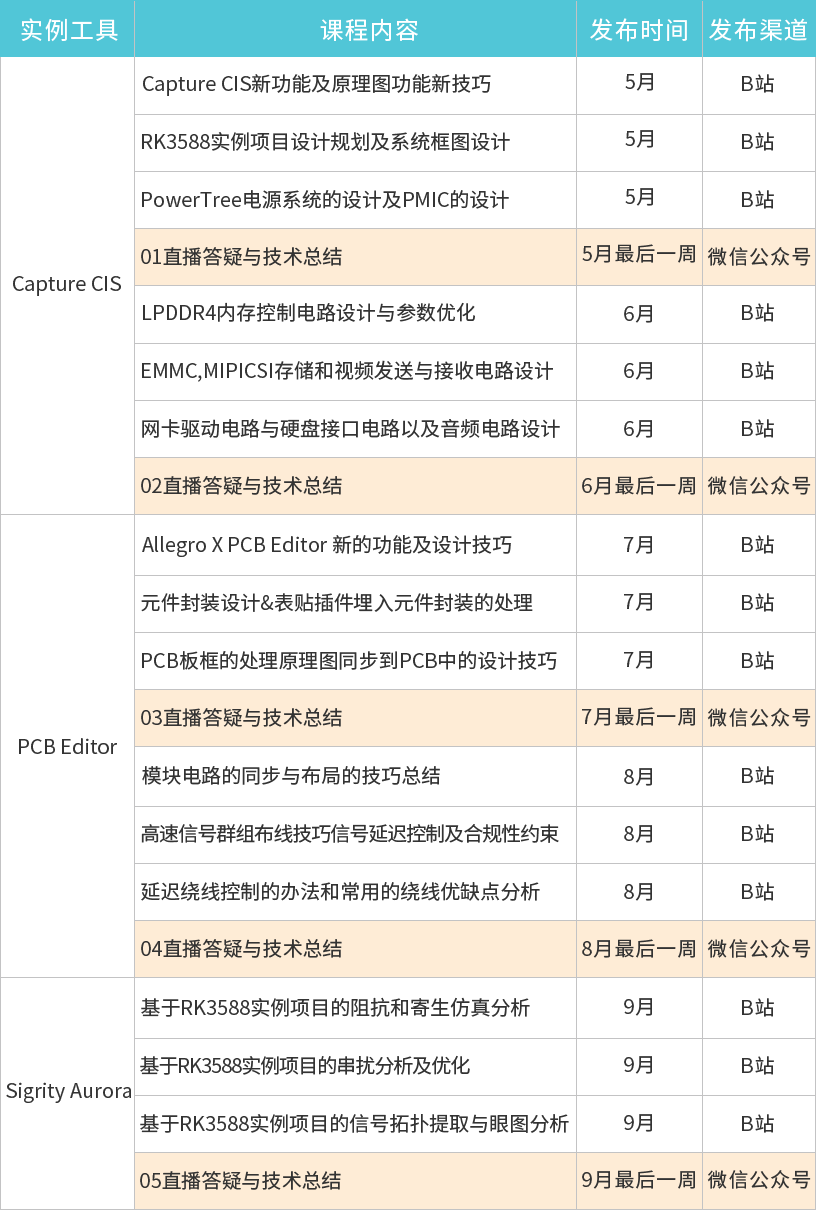

課程大綱

-

仿真

+關注

關注

50文章

4082瀏覽量

133613 -

PCB設計

+關注

關注

394文章

4688瀏覽量

85649

發布評論請先 登錄

相關推薦

米爾RK3576和RK3588怎么選?-看這篇就夠了

RK3588與RK3576區別解析

迅為瑞芯微RK3588開發板深度剖析丨首選的性能

品英Pickering最新版本的微波開關設計工具, 增強了仿真能力和原理圖設計功能

迅為RK3588開發板深度剖析丨首選的性能

探索巔峰性能 |迅為 RK3588開發板深度剖析

外協:RK3588適配linux

亮鉆科技推出重磅新品:基于RK3588S平臺的K-3588S

基于RK3588的NPU案例分享!6T是真的強!

實例課程 I 基于 RK3588 實例的最新版本 Cadence Allegro PCB 設計與仿真項目

實例課程 I 基于 RK3588 實例的最新版本 Cadence Allegro PCB 設計與仿真項目

評論