NOR Flash是一種非易失閃存技術(shù),是Intel在1988年創(chuàng)建。NOR和NAND是現(xiàn)在市場(chǎng)上兩種主要的非易失閃存技術(shù)。大多數(shù)情況下閃存只是用來(lái)存儲(chǔ)少量的代碼,這時(shí)NOR閃存更適合一些,而NAND則是高數(shù)據(jù)存儲(chǔ)密度的理想解決方案。

NOR的特點(diǎn)是芯片內(nèi)執(zhí)行(XIP, eXecuteIn Place),這樣應(yīng)用程序可以直接在flash閃存內(nèi)運(yùn)行,不必再把代碼讀到系統(tǒng)RAM中。NOR的傳輸效率很高,在1~4MB的小容量時(shí)具有很高的成本效益,但是很低的寫入和擦除速度大大影響了它的性能。NAND結(jié)構(gòu)能提供極高的單元密度,可以達(dá)到高存儲(chǔ)密度,并且寫入和擦除的速度也很快。應(yīng)用NAND的困難在于flash的管理需要特殊的系統(tǒng)接口。目前全球90%市場(chǎng)在前5大NOR FLASH公司,他們是:美光、旺宏、華邦、CYPRESS(已收購(gòu)臺(tái)灣宜揚(yáng)科技)、兆易創(chuàng)新。其它百分之十的市場(chǎng)被國(guó)內(nèi)的XMC(武漢新芯)、PUYA(普冉)、BOYA(博雅)、YICHU(易儲(chǔ))、XTX(芯天下)和其他品牌等占有。NOR FLASH目前的晶圓廠有:臺(tái)積電、華潤(rùn)上華、聯(lián)華電子、和艦科技、華虹NEC、華力微電子、武漢新芯、中芯國(guó)際等,前幾大封裝測(cè)試廠有:日月光、安靠封測(cè)、矽品科技、京隆科技、南通富士通、華潤(rùn)安盛、天水華天等。1,一般描述

先記住下面的參數(shù):

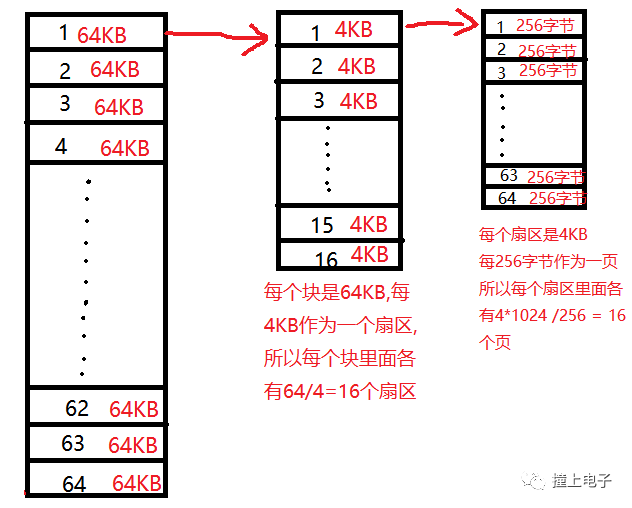

?Page:256 Bytes?Sector:16 Pages(4KB)?Block:16 Sector(64KB)

GD25Q80?8M-bit(1024K Bytes)?4096個(gè)Page?256個(gè)Sector?16個(gè)Block

GD25Q16?16M-bit(2048K Bytes)?8192個(gè)Page?512個(gè)Sector?32個(gè)Block

數(shù)據(jù)寫入的時(shí)候只能按照Page來(lái)寫入,最多一次只能寫256個(gè)字節(jié),也就是一個(gè)頁(yè)的空間。每次寫入都要先擦除。數(shù)據(jù)擦除只能按扇區(qū)擦除或按塊擦除。可以按 16 頁(yè)一組(4KB 扇區(qū)擦除)、128 頁(yè)一組(32KB 塊擦除)、256 頁(yè)一組(64KB 塊擦除)或者整片擦除(chip erase)。支持標(biāo)準(zhǔn)的 SPI(Serial Peripheral Interface),也支持高性能的 Dual/Quad I/O SPI。支持的 SPI 時(shí)鐘頻率高達(dá) 120MHz,以及當(dāng)使用快速讀 Dual/Quad I/O 指令時(shí),Dual I/O 模式的等效時(shí)鐘頻率 240MHz(120MHz * 2)和 Quad I/O 模式的 480MHz(120MHz * 2)。這樣的傳輸速率超過(guò)標(biāo)準(zhǔn)的異步 8 位和 16 位的并行 Flash 存儲(chǔ)器。Hold 管腳和 Write Protect 管腳提供了更進(jìn)一步的控制靈活性。此外,設(shè)備支持 128 位唯一UID號(hào)。數(shù)據(jù)保存時(shí)間20年,而EEPROM的數(shù)據(jù)保存時(shí)間有100年。

2,管腳描述

寫保護(hù)(Write Protect)管腳用于預(yù)防狀態(tài)寄存器被寫,該功能需要結(jié)合狀態(tài)寄存器的塊保護(hù)(Block Protect)位(CMP,SEC,TB,BP2,BP1 和 BP0)以及狀態(tài)寄存器的保護(hù)位(SRP0)一起使用。小至 4KB 的扇區(qū),大致整個(gè)存儲(chǔ)陣列都能被硬件保護(hù)。/WP 管腳低電平有效,如果狀態(tài)寄存器2 的 QE 位被置為 Quad I/O,/WP 管腳的功能不再是寫保護(hù),而是 IO2。

HOLD(/HOLD)

/HOLD 管腳允許設(shè)備被選中后能夠暫停,當(dāng) /HOLD 管腳被拉低且 /CS 為低電平時(shí),DO 管腳將變成高阻抗,而 DI 和 CLK 管腳將會(huì)被忽略。當(dāng) /HOLD 被拉高,設(shè)備操作恢復(fù)。在多個(gè)設(shè)備共享同一個(gè) SPI 信號(hào)時(shí),/HOLD 功能就很有用了。/HOLD 管腳低電平有效,當(dāng)狀態(tài)寄存器2 的 QE 位被置為 Quad I/O 時(shí),/HOLD 管腳功能失效,而變成 IO3。Serial Clock(CLK)SPI 串行時(shí)鐘輸入管腳為串行輸入和輸出操作提供時(shí)序。雙倍SPI指令使用”Fast Read Dual Output and Dual I/O(3B和BBhex)”指令支持雙倍速SPI操作。這些指令允許數(shù)據(jù)以正常速度的兩到三倍的在設(shè)備間傳輸。雙倍讀指令適用于 上電時(shí)快速加載代碼到RAM 或者 直接從SPI總線上執(zhí)行代碼(XIP) 的情形。當(dāng)使用雙倍速SPI指令時(shí),DI和DO引腳將充當(dāng) IO 0和IO 1.四倍速SPI指令使用”Fast Read Quad Output”、” Fast Read Quad I/O” 、”Word Read Quad I/O” 和 “Octal Word Quad I/O”指令(6B、EB、E7、E3)支持四倍速SPI操作。這些指令允許數(shù)據(jù)以正常速度的四到六倍的在設(shè)備間傳輸。四倍讀指令顯著提升連續(xù)和隨機(jī)訪問(wèn)傳輸速度,這速度滿足將代碼快速加載到RAM或者直接在SPI總線上執(zhí)行(XIP)。使用四倍速SPI指令時(shí),DI和DO引腳將充當(dāng) IO 0和IO 1 ,WP和HOLD充當(dāng)IO2 和IO 3。四倍速SPI指令要求狀態(tài)寄存器2中的QE功能位打開(kāi)。3,內(nèi)存區(qū)分類GD25Q32的容量是32Mbit,也就是32/8=4MB字節(jié)=4*1024=4096KB字節(jié)。GD25Q32規(guī)定每64KB字節(jié)作為一個(gè)塊,所以該芯片總共分成了 4096K/64K=64個(gè)塊。GD25Q32還規(guī)定每4KB字節(jié)作為一個(gè)扇區(qū),所以每一塊總共分成了 64K/4K=16個(gè)扇區(qū)。GD25Q32還規(guī)定每456字節(jié)作為一頁(yè),所以每一扇區(qū)總共分成了4*1024/256/4K=16個(gè)扇區(qū)。

-

芯片

+關(guān)注

關(guān)注

456文章

51016瀏覽量

425317 -

閃存

+關(guān)注

關(guān)注

16文章

1796瀏覽量

115018

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

兆易創(chuàng)新車規(guī)閃存芯片GD25/55LX系列榮獲高工智能汽車“年度產(chǎn)品技術(shù)創(chuàng)新獎(jiǎng)”

STM32H743配置了QSPI驅(qū)動(dòng)W25Q256JV,初始化成功,但后續(xù)都失敗了,為什么?

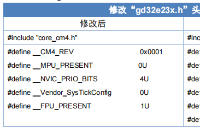

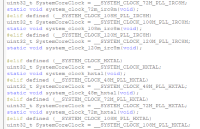

【GD32 MCU 移植教程】7、從 GD32F10x 移植到 GD32E103

【GD32 MCU 移植教程】6、從GD32F1x0和GD32F3x0移植到GD32E230

【GD32 MCU 移植教程】5、GD32E230 系列移植到 GD32F330 系列

【GD32 MCU 移植教程】2、從 GD32F303 移植到 GD32F503

【「ARM MCU嵌入式開(kāi)發(fā) | 基于國(guó)產(chǎn)GD32F10x芯片」閱讀體驗(yàn)】+書籍整體概況

解讀MIPI A-PHY與車載Serdes芯片技術(shù)與測(cè)試

【GD32H757Z海棠派開(kāi)發(fā)板使用手冊(cè)】第十一講 SPI-SPI NOR FLASH讀寫實(shí)驗(yàn)

GD32F103xxArm?Cortex?-M3 32位MCU芯片手冊(cè)

【GD32F470紫藤派開(kāi)發(fā)板使用手冊(cè)】第十一講 SPI-SPI NOR FLASH讀寫實(shí)驗(yàn)

STM32F103ZET6將SPI+W25QXX的程序移植后,步進(jìn)電機(jī)均轉(zhuǎn)速轉(zhuǎn)慢的原因?

如何對(duì)GD32 MCU進(jìn)行加密?

芯片GD32與以太網(wǎng)芯片的坑

GD25Qxx芯片解讀

GD25Qxx芯片解讀

評(píng)論