DDS(Direct Digital Synthesis,直接數字頻率合成),作為信號發生器使用,在Quartus中也叫NCO(Numerically Controlled Oscillator,數字控制振蕩器),是軟件無線電中的重要組成部分。

本次使用Vivado調用DDS的IP進行仿真,并嘗試多種配置方式的區別,設計單通道信號發生器(固定頻率)、Verilog查表法實現DDS、AM調制解調、DSB調制解調、可編程控制的信號發生器(調頻調相)。

使用System parameters和Hardware parameters分別配置,對比**Standard Mode **標準模式和 Rasterized Mode柵格模式的不同,對比不同時鐘下同一個配置的不同。

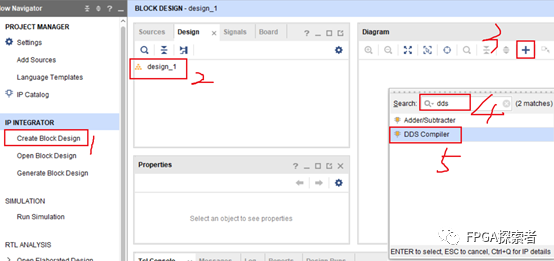

一、新建工程

新建工程,新建原理圖BlockDesign,調用DDS的IP核,默認輸出信號時域波形和相位信息。

二、DDS 配置

第一頁:基礎配置

1:配置選項

三種模式可選(相位發生器+sin/cos波形發生器、僅有相位發生器、僅有sin/cos波形發生器);

2:運行時鐘aclk;

100MHz工作時鐘,即100MHz采樣率。

3:通道個數;

設為1,單通道模式,通道的采樣頻率等于采樣時鐘100MHz,當設為多個通道時,每個通道的采樣率為工作時鐘/通道數,比如4通道100MHz時鐘,每個通道采樣率25MHz。

4:操作模式;

Standard標準模式(常用) , Rasterized柵格模式 。兩種情況下,輸出的頻率和頻率分辨率、相位增量等參量的計算方式不同,具體參見Xilinx的PG141第14~18頁。

Standard Mode 和 Rasterized Mode在實現指定頻率、幅度的信號時,輸出沒有太大的差別,兩者均能滿足要求,一般使用Standard配置方便。

主要的區別 :

Standard模式下計算出來的相位增量可能是小數,而在FPGA中要對 相位進行截斷取整 ,存在相位誤差,對噪聲要求較高的場合,可以使用8處的噪聲整形配置來彌補,使用 相位抖動(Phase Dithering) 或者 泰勒級數糾正(Taylor Series Correct) 來 補償相位誤差 ;

Rasterized Mode配置下,相位增量一定是整數,不存在截斷效應 ,沒有Standard模式下的時間基抖動。

5:參數選項(System parameters、Hardware parameters)

(1) System parameters

(2) Hardware parameters

6、7、8處配置系統參數System parameters,其中:

6:配置SFDR無雜散動態范圍

SFDR(SpuriousFree Dynamic Range,無雜散動態范圍),對應幅度 ,對應M_AXIS_DATA通道,SFDR越大,用于表示幅度的數據的位寬越大;

如下圖所示計算輸出位寬,當使用SFDR= 96 dB,配置8處的噪聲整形位None或者Dithering時,輸出位寬位96/6=16位,向上取整后為16位;使用SFDR = 95 dB,95/6=15.83,向上取整為16位。

7:配置頻率分辨率

對應相位的增量配置、位寬,對應M_AXIS_PHASE通道,頻率分辨率越小,用于表示相位的數據的位寬越大;

8:配置噪聲整形

4處配置成Standard標準模式時才會使用噪聲整形,

Auto根據設計的SFDR參數自動選擇是否使用整形;

None不整形;

Phase Dithering相位抖動,在使用相位截斷技術時,產生隨機的噪聲來使得量化誤差隨機;

Taylor Series Correct 泰勒級數校正;

4處配置成Rasterized時,不存在相位誤差,只能配置None。

For virtually all applications, the preferred implementationis the dithered DDS.

對于絕大多數的應用,首選的是帶有相位抖動補償的DDS。

相位抖動用于提高SFDR,但代價是增加底噪。

6、7兩處的配置影響輸出數據的位寬,可以在原理圖中體現,也可以在“ Summary ”頁查看,如圖所示,在 100MHz 工作時鐘下,1 處表示要達到0.4Hz的頻率分辨率,需要輸出 28 位位寬的相位(有效位寬),由AXI_Stream接口輸出時,以 8 位位寬步進,所以28位有效位寬的相位信息通過高位補零達到 32 位位寬,m_axis_phase_tdata[27:0] 為有效的相位信息;2 處表示要達到 45 dB 的輸出信噪比, 輸出的 sin 和 cos 波形數據各自需要 8 位 ,共計需要 16 位, 其中高 8 位 m_axis_data_tdata[15:8] 表示 sin,低 8 位表示 cos ;3 處表示按上述配置的輸出延時有 3 個時鐘周期,需要消耗 1 個18 Kbit 的 BRAM。

9:Hardware parameters

這種模式下直接配置輸出的位寬,但是具體輸出對應的SFDR和頻率分辨率會在Summary中體現,也可以自行計算。

第二頁:具體實現

1處:相位增量是否支持可編程配置

Fixed是固定相位增量,DDS運行過程中不可更改,即對應不可變頻率;

Programmable可編程,選中后出現配置接口,可在DDS運行過程中隨時寫入頻率控制字改變輸出波形的頻率,用于偶爾改變頻率;

Streaming應用于頻繁改變頻率,或者FM頻率調制 ;

2處:相位偏移是否支持可編程配置

None不支持;

Fixed固定相位偏移;

Programmable可編程配置(偶爾改變);

Streaming經常改變,應用于相位調制;

3處:輸出波形選擇

Sine只輸出sin波形;Cosine輸出cos波形;兩個的位寬均為第一頁設置的數據位寬, Sine and Cosine同時輸出sin和cos波形,其中高位表示sin,低位表示cos,總的數據位寬加倍 ;

4處:極性選擇

sin和cos波形默認使用的是有符號數,勾選相應的選項后,正負取反;

5處:幅度模式

Full Range:全精度(全范圍),針對通信應用,需要最大振幅,但由于自動增益控制導致振幅的值不那么重要的場合,輸出幅度接近1;

Unit Cycle:單位圓 ,用于對DDS輸出振幅值要求很高的應用, 比如產生FFT旋轉因子 。單位圓時,DDS輸出幅值為半全量程(即取值范圍為01000..(+ 0.5)。110000 . .(-0.5))。

6處:是否輸出相位信息

勾選后含有相位輸出通道,不勾選時只輸出幅度信息M_AXIS_DATA;

7處:使用的存儲資源類型

Auto由具體所需的資源決定,資源較少時使用DROM,資源多時選擇BROM;DistributeROM選擇分布式ROM(DROM),Block ROM選擇塊ROM資源(BROM);

8處:綜合優化策略

Area是面積優先,盡可能節省資源用量(LUT、FF等),Speed速度優先,盡可能提升性能;

9處:DSP48資源的使用策略

Minimal盡可能少用,節省資源,Maximal盡可能多用,提高性能;

第三頁:總線配置

單通道模式下,總線的配置只包含可選的輸出信號的Ready。多通道模式下,通道可選是否包含tlast等信號。

1處:輸出ready信號

選中則輸出的2個通道中增加tready信號(可選),根據AXI_Stream總線協議的規則, 由后級接收模塊輸入一個ready信號(高電平),表示已經準備好接收DDS輸出,此時DDS才能輸出 ;

2處:延時配置

第四頁 輸出頻率配置

配置各通道的輸出頻率,在第一頁中只使用了1個Channel,所以此處只能配置一個通道,直接配置輸出頻率,單位MHz,比如0.02MHz;

第五頁:總結

資源使用較多時默認使用Block ROM,使用面積優先Area策略;單通道采樣頻率=時鐘頻率,100MHz,輸出波形16 bit,高8位為sin,低8位cos。

三、仿真

按照上述配置,再配置一個2 MHz輸出頻率的DDS。

將輸出的16位波形數據分割, 高8位表示sin正弦信號,低8位表示cos余弦信號 ,相位為鋸齒狀,注意若輸出通道中包含了 ready信號 ,根據AXI_Stream總線的要求,外部需要給ready信號,當ready有效時,DDS才會輸出,仿真中可以一直給高電平。

wire [7:0] sin_wave;

wire [7:0] cos_wave;

wire [7:0] sin_wave_2;

wire [7:0] cos_wave_2;

assign sin_wave = M_AXIS_DATA_0_tdata[15:8];

assign cos_wave = M_AXIS_DATA_0_tdata[7:0];

assign sin_wave_2 = M_AXIS_DATA_1_tdata[15:8];

assign cos_wave_2 = M_AXIS_DATA_1_tdata[7:0];

-

振蕩器

+關注

關注

28文章

3833瀏覽量

139141 -

調制解調器

+關注

關注

3文章

854瀏覽量

38830 -

FFT

+關注

關注

15文章

435瀏覽量

59404 -

DDS

+關注

關注

21文章

634瀏覽量

152714 -

信號發生器

+關注

關注

28文章

1476瀏覽量

108807

發布評論請先 登錄

相關推薦

vivado有哪幾種常用IP核?如何去調用它們

Vivado軟件仿真DDS核的過程中應該注意的問題

調用Vivado IP核的方法

Vivado中PLL開發調用IP的方法

Vivado調用Questa Sim或ModelSim仿真小技巧

FPGA應用之vivado三種常用IP核的調用

使用Vivado調用questasim仿真報錯的原因及其解決辦法

Xilinx Vivado DDS IP使用方法

如何使用Vivado調用DDS的IP進行仿真呢?

如何使用Vivado調用DDS的IP進行仿真呢?

評論