1.先進制程貼近物理極限迭代放緩,Chiplet 展現(xiàn)集成優(yōu)勢

1.1.Chiplet 是延續(xù)摩爾定律的重要手段

Chiplet 俗稱“芯粒”或“小芯片組”,通過將原來集成于同一 SoC 中的各個元件分拆,獨立 為多個具特定功能的 Chiplet,分開制造后再通過先進封裝技術(shù)將彼此互聯(lián),最終集成封裝 為一個系統(tǒng)芯片。Chiplet 可以將一顆大芯片拆解設計成幾顆與之有相同制程的小芯片,也 可以將其拆解設計成幾顆擁有不同制程的小芯片。Chiplet 是一種硅片級別的 IP 整合重用技 術(shù),其模塊化的集成方式可以有效提高芯片的研發(fā)速度,降低研發(fā)成本和芯片研制門檻。 傳統(tǒng)的 SoC 是將多個負責不同類型計算任務的計算單元,通過光刻的形式制作到同一塊晶圓 上,其追求的是高度的集成化,利用先進制程對于所有的單元進行全面的提升。而 Chiplet 是在設計系統(tǒng)芯片時,先按照不同的計算單元或功能單元進行分解;然后針對每個單元選擇 最適合的半導體制程工藝分別進行制造;再通過先進封裝技術(shù)將各個單元彼此互聯(lián);最終集 成封裝為一個系統(tǒng)級芯片組。

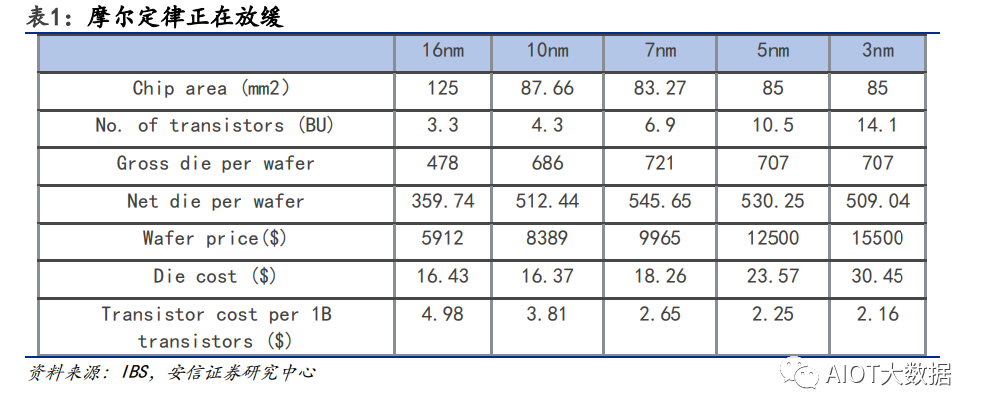

摩爾定律正在逐步放緩。隨著工藝制程節(jié)點繼續(xù)向著更小的 5nm、3nm 甚至埃米級別推進,半 導體工藝制程已經(jīng)越來越逼近物理極限,不僅推進的難度越來越高,所需要付出的代價也越 來越大。研究機構(gòu) IBS 統(tǒng)計對比 16nm 至 3nm 的單位數(shù)量的晶體管成本指出,隨著制程工藝 的推進,單位數(shù)量的晶體管成本的下降幅度在急劇降低。比如從 16nm 到 10nm,每 10 億顆晶 體管的成本降低了 23.5%,而從 5nm 到 3nm 成本僅下降了 4%。隨著先進制程的持續(xù)推進,單 位晶體管所需要付出的成本降低的速度正在持續(xù)放緩,即意味著摩爾定律正在放緩。 Chiplet 誕生背景是在摩爾定律放緩,性價比逐步凸顯。摩爾定律由戈登·摩爾(Gordon Moore) 提出,其內(nèi)容為“當價格不變時,集成電路上可容納的晶體管的數(shù)目,約每隔 18-24 個月便 會增加一倍。”在集成電路過去幾十年的發(fā)展過程中,受摩爾定律的指引,在晶體管的尺寸不 斷微縮以及處理器性能不斷增強的同時,半導體制程工藝的成本可以維持不變,甚至下降。 Chiplet 能夠通過多個裸片片間集成,突破了單芯片 SoC 的諸多瓶頸,帶來一系列優(yōu)越特性, 從而延續(xù)摩爾定律。

1.2.Chiplet 在設計成本、良率、制造成本、設計靈活性等方面優(yōu)勢明顯

與傳統(tǒng) SoC 相比,Chiplet 在設計成本、良率、制造成本、設計靈活性等方面優(yōu)勢明顯。

1. Chiplet 能顯著提升良率。在高性能計算、AI 等方面的巨大運算需求下,芯片性能快速 提升,芯片中的晶體管數(shù)量也在快速增加,導致芯片面積不斷變大。對于晶圓制造工藝而言, 芯片面積越大,工藝的良率越低。由于每片 wafer 上都有一定概率的失效點,而對于晶圓工 藝來說,在同等技術(shù)條件下難以降低失效點的數(shù)量,因此被制造的芯片面積較大,失效點落 在單個芯片上的概率就越大,所以良率會下降。通過運用 Chiplet 的手段,可以將大芯片拆 解分割成幾顆小芯片,單個芯片面積變小,失效點落在單個小芯片上的概率將大大降低,從 而提高了制造良率。

2. Chiplet 能降低芯片制造成本。Chiplet 的核心思想是先分后合,先將單芯片中的功能塊 拆分出來,再通過先進封裝模塊集成為單芯片。將 SoC 進行 Chiplet 化之后,不同的芯粒可 以根據(jù)需要來選擇合適的工藝制程分開制造,然后再通過先進封裝技術(shù)進行組裝,不需要全 部都采用先進的制程在一塊晶圓上進行一體化制造,這樣可以極大地降低芯片的制造成本。

3. Chiplet 能提高芯片設計的靈活度,顯著降低設計成本。由于 Chiplet 芯粒可以獨立設計 和組裝,因此制造商可以根據(jù)自己的需要來選擇不同類型、不同規(guī)格和不同供應商的芯粒進 行組合,很大程度上提高了芯片設計的靈活性和可定制化程度;并且制造商可以依賴于預定 好的芯片工具箱來設計新產(chǎn)品,縮短芯片的上市時間。同時 The Linley Group 在《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet 技術(shù)可以將 大型 7nm 設計的成本降低高達 25%;在 5nm 及以下的情況下,節(jié)省的成本更大。

Chiplet 方案目前在互聯(lián)與封裝兩塊還存在一定的難點。Chiplet 的關(guān)鍵是讓芯粒之間高速 互聯(lián),因此芯片設計公司在設計芯粒之間的互聯(lián)接口時,需要保證高數(shù)據(jù)吞吐量與低數(shù)據(jù)延 遲和誤碼率,同時還要考慮能效和連接距離。Chiplet 方案對封裝工藝也有更高的要求,主 要由于第一封裝體內(nèi)總熱功耗將顯著提升;第二芯片采用 2.5D/3D 堆疊,增加了垂直路徑熱 阻;第三更加復雜的 SiP,跨尺度與多物理場情況下熱管理設計復雜。以上要求都給 Chiplet 技術(shù)的發(fā)展增加了難點。

2. AI 等高算力芯片的需求增加,Chiplet 迎來高速發(fā)展

2.1.Chiplet 在服務器中率先應用

在高性能計算領域,Chiplet 是滿足當下對算力需求的關(guān)鍵技術(shù)。運用 Chiplet 技術(shù),一方 面通過 Die to Die 連接和 Fabric 互聯(lián)網(wǎng)絡,能夠?qū)⒏嗨懔卧呙芏取⒏咝省⒌凸?地連接在一起,從而實現(xiàn)超大規(guī)模計算;另一方面,通過將 CPU、GPU 和 NPU 高速連接在同一 個 Chiplet 中,實現(xiàn)芯片級異構(gòu)系統(tǒng),可以極大提高異構(gòu)核之間的傳輸速率,降低數(shù)據(jù)訪問 功耗,從而實現(xiàn)高速預處理和數(shù)據(jù)調(diào)度;同時,其采用非先進制程構(gòu)建 Cache(位于 CPU 與 內(nèi)存之間的臨時存儲器),提高片上 Cache 的容量和性價比,并通過 3D 近存技術(shù),降低存儲 訪問功耗,從而滿足大模型參數(shù)需求。 從下游應用場景來看,服務器、自動駕駛領域是比較適合 Chiplet 落地場景,消費電子由于 對輕薄、功耗要求較高,不太適合應用 Chiplet。隨著近年來高性能計算、人工智能、5G、 汽車、云端等新興市場的蓬勃發(fā)展,對于算力的需求持續(xù)攀升,僅靠單一類型的架構(gòu)和處理 器無法處理更復雜的海量數(shù)據(jù),“異構(gòu)”正在成為解決算力瓶頸關(guān)鍵技術(shù)方向。Chiplet 技術(shù) 目前主要聚焦于 HPC 高性能計算與 AI 人工智能領域,隨著算力、存儲等需求升級,Chiplet 有望在未來市場上得到更加廣泛的應用。 國際巨頭廠商已經(jīng)布局 Chiplet 在高性能計算領域的應用。英特爾于 2022 年底發(fā)布了數(shù)據(jù) 中心 GPU Max,是英特爾針對高性能計算加速設計的第一款 3D GPGPU,在一顆芯片里集成了 47 顆芯粒,有 5 種制程,以此獲得比上一代高出三倍性能的提升。

AMD 在這個方向走在了更前面,目前已經(jīng)發(fā)布了第一個數(shù)據(jù)中心 APU(Accelerated Processing Unit,加速處理器)產(chǎn)品 MI300,其采用 Chiplet 技術(shù),在 4 塊 6 納米芯片上, 堆疊了 9 塊 5 納米的計算芯片。AMD 表示,相較于上一代的 Instinct MI250,提升了 8 倍的 AI 訓練算力和 5 倍的 AI 能效。 蘋果則與臺積電合作開發(fā)了 UltraFusion 封裝技術(shù),也是一種類似 Chiplet 的技術(shù),能同時 傳輸超過 1 萬個信號,芯片間的互連帶寬可達 2.5TB/s,超出了 UCIe 1.0 的標準。蘋果此前發(fā)布的 M1 Ultra 芯片將兩個 M1 Max 芯片的裸片,采用 UltraFusion 封裝技術(shù)進行互連,其 CPU 核心數(shù)量增加至 20 個,而 GPU 核心數(shù)量更是直接增加至 64 個。M1 Ultra 的神經(jīng)網(wǎng)絡引 擎也增加至 32 核,能夠帶來每秒 22 萬億次的運算能力。

以 ChatGPT 為代表的的 AI 應用蓬勃發(fā)展,對上游 AI 芯片算力提出了更高的要求,而運用 Chiplet 模式的異構(gòu)集成方案,可以通過將通用需求與專用需求解耦,大幅降低芯片設計投 入門檻及風險,有效解決下游客戶在算法適配、迭代周期、算力利用率、算力成本等各方面 難以平衡的核心痛點。將支持人工智能的不同功能的芯片,如 GPU、CPU、加速器等,通過 Chiplet 的方式進行組合,可以構(gòu)建出更高效的 AI 加速器系統(tǒng)。國際巨頭廠商與國內(nèi)領先廠 商均在 Chiplet 技術(shù)于 AI 芯片的運用做了不同突破。 英偉達使運用 Chiplet 技術(shù)制作 AI 芯片的領先企業(yè),其于 2022 年發(fā)布的 H100 GPU 芯片就 是臺積電 4nm 工藝和 Chiplet 技術(shù)融合的創(chuàng)新之作。英偉達通過 Chiplet 技術(shù)將 HBM3 顯存 子系統(tǒng)集成到芯片里,可提供 3TB/s 的超高顯存帶寬,是上一代產(chǎn)品帶寬的近兩倍。同時借 助 4nm 先進制程,H100 GPU 芯片在 814 平方毫米的芯片面積里容納 800 億個晶體管,無論是 性能還是延遲,相較于上一代 A100 GPU 芯片都有巨大的提升。

英偉達另一款 AI 芯片 GH200 與 H100 屬于同一際代,但應用場景有所不同。英偉達 H100 的 架構(gòu)以 GPU 為主,重點用于數(shù)據(jù)運算和推理。GH200 架構(gòu)采用 CPU+GPU 異構(gòu)計算方式。GH200 采用 NVLink-C2C 技術(shù)方案,通過 Chiplet 工藝將基于 Arm 的 NVIDIA Grace CPU 與 NVIDIA H100 Tensor Core GPU 整合在了一起,實現(xiàn)流暢互連。具體來說,GH200 超級芯片將 72 核 的 Grace CPU、H100 GPU、96GB 的 HBM3 和 512 GB 的 LPDDR5X 集成在同一個封裝中,擁有高 達 2000 億個晶體管。這種組合提供了 CPU 和 GPU 之間高達 900G/s 的數(shù)據(jù)帶寬,為某些內(nèi)存 受限的工作負載提供了巨大的優(yōu)勢。相較 PCIe5,NVLink-C2C 在能效方面提升 25 倍,面積效 率提升 90 倍。

AMD 的 MI300 加速器也運用了 Chiplet 技術(shù),是業(yè)內(nèi)首款 CPU+GPU 異構(gòu)計算的存算一體芯片。 MI300 加速器專為領先的高性能計算(HPC)和 AI 性能而設計,這款加速卡采用 Chiplet 設 計,擁有 13 個小芯片,基于 3D 堆疊,包括 24 個 Zen4 CPU 內(nèi)核,總共包含 128GB HBM3 顯存和 1460 億晶體管,性能上比此前的 MI250 提高了 8 倍,在功耗效率上提高了 5 倍。

中國首款基于 Chiplet 的 AI 芯片“啟明 930”為北極雄芯開發(fā),該芯片采用 12nm 工藝生產(chǎn), 中央控制芯粒采用 RISC-V CPU 核心,可通過高速接口搭載多個功能型芯粒,并基于全國產(chǎn) 基板材料以及 2.5D 封裝,做到算力可拓展,提供 8~20TOPS(INT8)稠密算力來適應不同場 景,目前已與多家 AI 下游場景合作伙伴進行測試。

2.2.Chiplet 市場規(guī)模快速成長

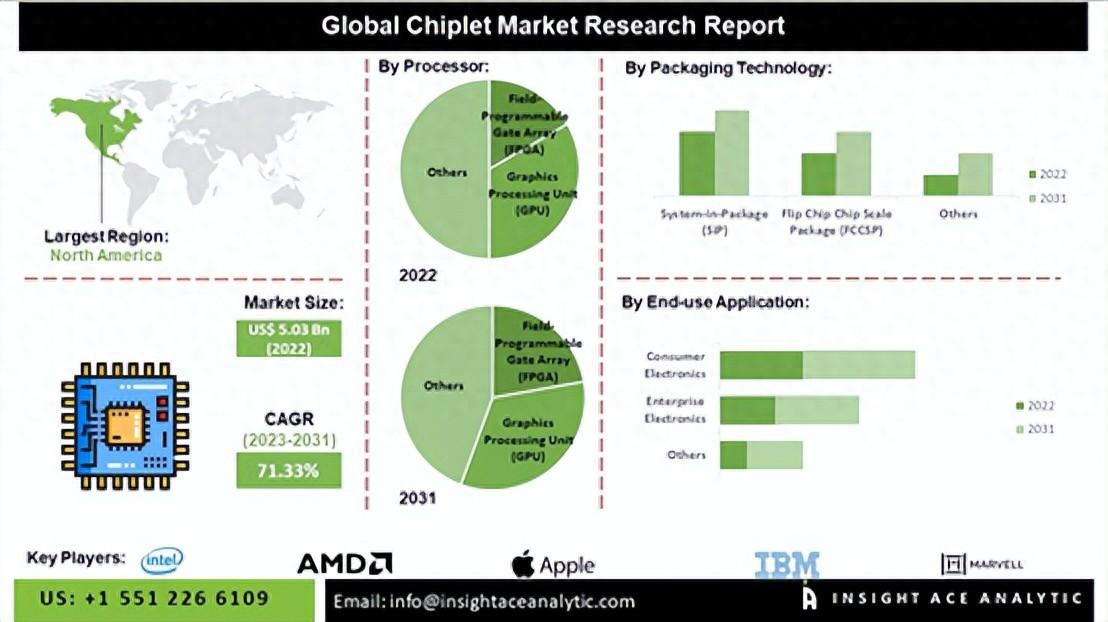

Chiplet 技術(shù)被視為“異構(gòu)”技術(shù)的焦點,也是當下最被企業(yè)所認可的新型技術(shù)之一。2022 年 3 月,英特爾、AMD、Arm、高通、三星、臺積電、日月光、Google Cloud、Meta、微軟等 全球領先的芯片廠商共同成立了 UCIe 聯(lián)盟,旨在建立統(tǒng)一的 die-to-die 互聯(lián)標準,促進 Chiplet 模式的應用發(fā)展,目前聯(lián)盟成員已有超過 80 家半導體企業(yè),越來越多的企業(yè)開始研 發(fā) Chiplet 相關(guān)產(chǎn)品。UCIe 在解決 Chiplet 標準化方面具有劃時代意義,標志著產(chǎn)業(yè)化落地 開始。

中國首個原生 Chiplet 技術(shù)標準《小芯片接口總線技術(shù)要求》于 2022 年 12 月發(fā)布,該標準 有助于行業(yè)規(guī)范化、標準化發(fā)展,為賦能集成電路產(chǎn)業(yè)打破先進制程限制因素,提升中國集 成電路產(chǎn)業(yè)綜合競爭力,加速產(chǎn)業(yè)進程發(fā)展提供指導和支持。 根據(jù) Gartner 數(shù)據(jù)統(tǒng)計,基于 Chiplet 的半導體器件銷售收入在 2020 年僅為 33 億美元, 2022 年已超過 100 億美元,預計 2023 年將超過 250 億美元,2024 年將達到 505 億美元,復 合年增長率高達 98%。超過 30%的 SiP 封裝將使用芯粒(Chiplet)來優(yōu)化成本、性能和上市 時間。MPU 占據(jù) Chiplet 大部分應用應用場景,Omdia 預測 2024 年用于 MPU 的 Chiplet 約占 Chiplet 總市場規(guī)模的 43%。

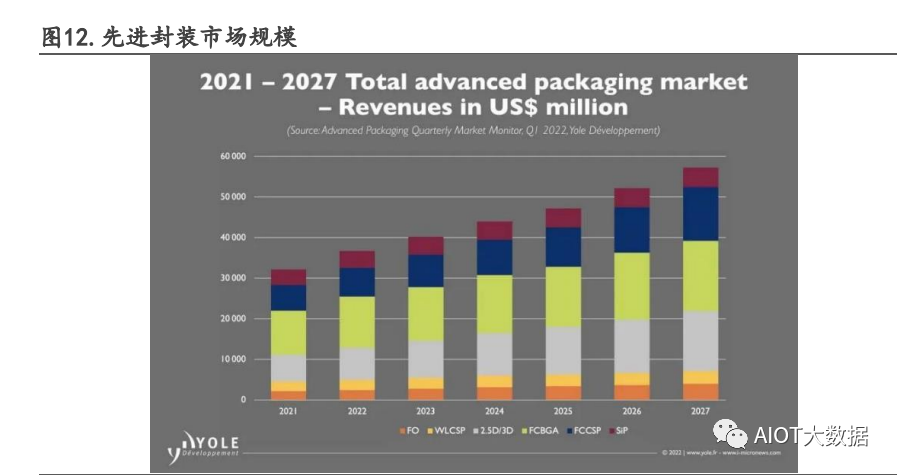

先進封裝是實現(xiàn) Chiplet 的前提,Chiplet 對先進封裝提出更高要求。根據(jù) Yole 數(shù)據(jù)統(tǒng)計, 2021 年先進封裝市場收入達 321 億美元,預計 2027 年將實現(xiàn) 572 億美元,復合年增長率為 10%。Chiplet 的實現(xiàn)需要依托于先進封裝,在芯片小型化的設計過程中,需要添加更多 I/O 與其他芯片接口,裸片尺寸有必要保持較大且留有空白空間,導致部分芯片無法拆分,芯片 尺寸小型化的上限被 pad(晶片的管腳)限制。并且單個晶片上的布線密度和信號傳輸質(zhì)量 遠高于 Chiplet 之間,要實現(xiàn) Chiplet 的信號傳輸,就要求發(fā)展出高密度、大帶寬布線的“先 進封裝技術(shù)”。先進封裝市場的快速發(fā)展為 Chiplet 市場的發(fā)展提供了技術(shù)基礎。

3.龍頭 IC 制造及封測廠加碼布局 Chiplet

3.1.Chiplet 產(chǎn)業(yè)鏈:封測環(huán)節(jié)重要性大幅提高

Chiplet 技術(shù)發(fā)展早期往往局限于企業(yè)內(nèi)部獨立研發(fā)和應用,且僅應用于一些高端產(chǎn)品,如 服務器和高性能計算等,組裝和測試等方面仍存在技術(shù)瓶頸。隨著 Chiplet 技術(shù)的不斷成熟 和商業(yè)化推廣,越來越多的芯片廠商、設計公司和封測廠開始使用 Chiplet 技術(shù),Chiplet 的 商業(yè)化應用趨勢也促進了整個芯片生態(tài)系統(tǒng)的升級和發(fā)展。隨著 Chiplet 技術(shù)的發(fā)展, Chiplet 產(chǎn)業(yè)鏈各環(huán)節(jié)逐漸完善,即由 Chiplet 系統(tǒng)級設計、EDA/IP、芯粒(核心、非核心、 IO Die、Base Die)、制造、封測組成的完整 Chiplet 生態(tài)鏈。 Chiplet 產(chǎn)業(yè)鏈主鏈有四大環(huán)節(jié),包括芯粒、芯片設計、封裝生產(chǎn)和系統(tǒng)應用,支撐環(huán)節(jié)包 括芯粒生產(chǎn)、設計平臺、EDA 工具、封裝基板、封測設備等領域。從 Chiplet 產(chǎn)業(yè)鏈邏輯看,芯片設計和封裝處于鏈條中心環(huán)節(jié),且與后端系統(tǒng)應用緊密聯(lián)動,而晶圓廠則被前置,成為 芯粒提供商的生產(chǎn)環(huán)節(jié)。

芯粒提供環(huán)節(jié)是指專業(yè)公司提供獨立設計、優(yōu)化和制造的芯粒給其他芯片制造商使用的過程。 這種模式可以提高芯片制造商的生產(chǎn)效率,加快產(chǎn)品推出時間,降低生產(chǎn)成本。傳統(tǒng)的 IP 軟 件企業(yè)將部分轉(zhuǎn)向 IP 芯片化的芯粒提供商,芯粒提供商通常會提供成熟的 IP 和技術(shù),使芯 片制造商可以更加專注于整個系統(tǒng)級設計和芯片集成。此外,芯粒提供商可以利用其專業(yè)知 識和技能,幫助芯片制造商優(yōu)化設計,提高性能和降低功耗。 Chiplet 芯片設計環(huán)節(jié)需要考慮每個小型芯片的功能和性能要求,并確定芯片之間的接口和 通信方式。在這個環(huán)節(jié)中,芯片設計師需要利用各種 EDA 工具進行設計、驗證和仿真,以確 保每個小型芯片都可以正確地集成在一起,同時滿足整個芯片的性能要求和功能需求。此外, 芯片設計人員還需要考慮芯片的功耗、可靠性和安全性等因素,并制定相應的設計方案和測 試計劃。芯片設計對于芯片的整體性能和功能有著至關(guān)重要的作用,因此芯片設計人員需要 具備深厚的電子設計自動化(EDA)知識和經(jīng)驗。

Chiplet 封測環(huán)節(jié)指將多個芯粒組裝到一個芯片上,并進行測試和驗證的過程。Chiplet 要 求高性能的芯粒互聯(lián),為先進封裝技術(shù)帶來了更多挑戰(zhàn)。包括高密度互聯(lián)帶來的工藝帶寬和 隔離問題,功率密度過高帶來的散熱問題,芯粒與封裝高速連接的基板問題,以及對無源元 件集成封裝問題等,同時 Chiplet 對封裝產(chǎn)線的要求將從 2.5D、2.5+3D 逐漸過渡到 3D。另 外關(guān)鍵的測試技術(shù)也會影響 Chiplet 芯片的良率,包括大芯片的散熱、供電、應力、信號完 整性(電磁場干擾)等。因此未來提升封測的技術(shù)水平對發(fā)展 Chiplet 至關(guān)重要。 Chiplet 技術(shù)已經(jīng)成為現(xiàn)代系統(tǒng)設計的重要組成部分,廣泛應用于云計算、人工智能、機器 學習、5G 通信、汽車和工業(yè)控制等領域。AMD 在 2019 年就發(fā)布了基于 Chiplet 模塊化設計 的 EPYC 處理器;Intel 在 2022 年發(fā)布采用了 3D 封裝的 Chiplet 技術(shù)的大型數(shù)據(jù)中心高性能 計算芯片 Ponte Vecchio,單個產(chǎn)品整合了 47 個小芯片,采用 5 種以上差異化工藝節(jié)點,集 成了超過 1000 億個晶體管;蘋果的 M1 Ultra 采用 Chiplet 技術(shù)將兩個 M1 Max 通過芯片連 接在一起。國內(nèi)以華為、寒武紀、壁仞科技等為代表的龍頭企業(yè),也有 Chiplet 產(chǎn)品上市。

3.2.全球巨頭廠商加碼布局 Chiplet 先進封裝

目前全球封裝技術(shù)主要由臺積電、三星、Intel 等公司主導,主要是 2.5D 和 3D 封裝。2.5D 封裝技術(shù)已非常成熟,廣泛應用于 FPGA、CPU、GPU 等芯片,目前是 Chiplet 架構(gòu)產(chǎn)品主要的 封裝解決方案。3D 封裝能夠幫助實現(xiàn) 3D IC,即晶粒間的堆疊和高密度互連,可以提供更為 靈活的設計選擇。但 3D 封裝的技術(shù)難度更高,目前主要有英特爾和臺積電掌握 3D 封裝技術(shù) 并商用。 臺積電比三星、英特爾更早采用 Chiplet 的封裝方式。臺積電推出了 3DFabric,搭載了完備 的 3D 硅堆棧(3D Silicon Stacking)和先進的封裝技術(shù)。3DFabric 是由臺積電前端 3D 硅 堆棧技術(shù) TSMC SoIC 系統(tǒng)整合的芯片,由基板晶圓上封裝(Chip on Wafer on Substrate, CoWoS)與整合型扇出(Integrated Fan-Out, InFO)的后端 3D 導線連接技術(shù)所組成,能夠 為客戶提供整合異質(zhì)小芯片(Chiplet)的彈性解決方案。該項技術(shù)先后被用于賽靈思的 FPGA、 英偉達的 GPU 以及 AMD 的 CPU。

Intel 主導的 2.5D 封裝技術(shù)為 EMIB,使用多個嵌入式包含多個路由層的橋接芯片,同時內(nèi) 嵌至封裝基板,達到高效和高密度的封裝。由于不再使用 interposer 作為中間介質(zhì),可以去 掉原有連接至 interposer 所需要的 TSV,以及由于 interposer 尺寸所帶來的封裝尺寸的限 制,可以獲得更好的靈活性和更高的集成度。相較于 MCM 和 CoWoS 技術(shù),EMIB 技術(shù)獲得更高 的集成度和制造良率。英特爾對各種先進封裝產(chǎn)品組合 (如 Foveros、EMIB 和 Co-EMIB) 的 投資是實施公司新領導層所公布的 IDM2.0 戰(zhàn)略的關(guān)鍵。

三星也在積極投資先進的封裝技術(shù),以滿足 HPC 應用在異質(zhì)芯片整合的快速發(fā)展。2020 年 8 月,三星公布了 X Cube 3D 封裝技術(shù)。在芯片互連方面,使用成熟的硅通孔 TSV 工藝。目前 X Cube 能把 SRAM 芯片堆疊在三星生產(chǎn)的 7nm EUV 工藝的邏輯芯片上,在更易于擴展 SRAM 容 量的同時也縮短了信號連接距離,提升了數(shù)據(jù)傳輸?shù)乃俣取4撕蟀l(fā)布的 I-Cube 可以將一個 或多個邏輯 die 和多個 HBM die 水平放置在硅中介層,進行異構(gòu)集成。

日月光憑借在 FOCoS 先進封裝技術(shù)的布局,是目前在封測代工廠中唯一擁有超高密度扇出解 決方案的供應商。日月光的 FOCoS 提供了一種用于實現(xiàn)小芯片集成的硅橋技術(shù),稱為 FOCoSB(橋),它利用帶有路由層的微小硅片作為小芯片之間的封裝內(nèi)互連,例如圖形計算芯片 (GPU)和高帶寬內(nèi)存(HBM)。硅橋嵌入在扇出 RDL 層中,是一種可以不使用硅中介層的 2.5D 封 裝方案。與使用硅中介層的 2.5D 封裝相比,F(xiàn)OCoS-B 的優(yōu)勢在于只需要將兩個小芯片連接在 一起的區(qū)域使用硅片,可大幅降低成本。

3.3.國內(nèi)企業(yè)緊跟產(chǎn)業(yè)趨勢,加快布局 Chiplet 先進封裝

Chiplet 被視為中國與國外差距相對較小的先進封裝技術(shù),有望帶領中國半導體產(chǎn)業(yè)在后摩 爾時代實現(xiàn)質(zhì)的突破,因此,中國半導體企業(yè)緊跟產(chǎn)業(yè)趨勢,紛紛走向 Chiplet 研發(fā)的道路。 中國三大封測企業(yè)長電科技、通富微電與華天科技都在積極布局 Chiplet 技術(shù),目前已經(jīng)具 備 Chiplet 量產(chǎn)能力。 長電科技推出的面向 Chiplet 小芯片的高密度多維異構(gòu)集成技術(shù)平臺 XDFOI可實現(xiàn) TSVless 技術(shù),達到性能和成本的雙重優(yōu)勢,重點應用領域為高性能運算如 FPGA、CPU/GPU、AI、5G、自動駕駛、智能醫(yī)療等。XDFOI是一種以 2.5D TSV-less 為基本技術(shù)平臺的封裝技術(shù), 在線寬/線距可達到 2μm/2μm 的同時,還可以實現(xiàn)多層布線層,以及 2D/2.5D 和 3D 多種異 構(gòu)封裝,能夠提供小芯片(Chiplet)及異構(gòu)封裝的系統(tǒng)封裝解決方案。目前長電先進 XDFOI 2.5D 試驗線已建設完成,并進入穩(wěn)定量產(chǎn)階段,同步實現(xiàn)國際客戶 4nm 節(jié)點多芯片系統(tǒng)集成 封裝產(chǎn)品出貨。

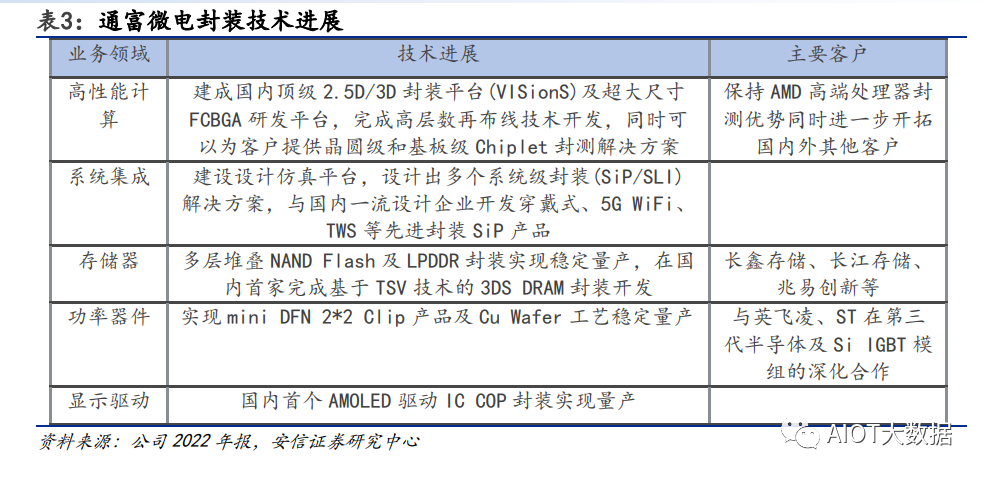

通富微電在先進封裝方面公司已大規(guī)模生產(chǎn) Chiplet 產(chǎn)品,7nm 產(chǎn)品已大規(guī)模量產(chǎn),5nm 產(chǎn) 品已完成研發(fā)即將量產(chǎn)。公司目前已建成國內(nèi)頂級 2.5D/3D 封裝平臺(VISionS)及超大尺寸 FCBGA 研發(fā)平臺,完成高層數(shù)再布線技術(shù)開發(fā)。AMD 是最早研究并實現(xiàn) Chiplet 應用的公司 之一,通富微電作為 AMD 在大陸唯一的封測合作伙伴,目前已經(jīng)在 Chiplet 封裝技術(shù)領域取 得市場先機,形成先發(fā)競爭優(yōu)勢。 華天科技已量產(chǎn) Chiplet 產(chǎn)品,主要應用于 5G 通信、醫(yī)療等領域。華天科技已掌握 SiP、 FC、TSV、Bumping、Fan-Out、WLP、3D 等先進封裝技術(shù)。華天科技目前已建立三維晶圓級封 裝平臺—3D Matrix,該平臺由 TSV、eSiFo(Fan-out)、3D SIP 三大封裝技術(shù)構(gòu)成。

后摩爾時代,Chiplet 由于高性能、低功耗、高面積使用率以及低成本的優(yōu)勢,在延續(xù)摩爾 定律的“經(jīng)濟效益”方面被寄予厚望。Chiplet 芯片設計環(huán)節(jié)能夠降低大規(guī)模芯片設計的門 檻,給中國集成電路產(chǎn)業(yè)帶來巨大發(fā)展機遇。

4.重點公司分析

4.1.長電科技:國內(nèi)先進封裝龍頭,23H2 有望迎周期拐點

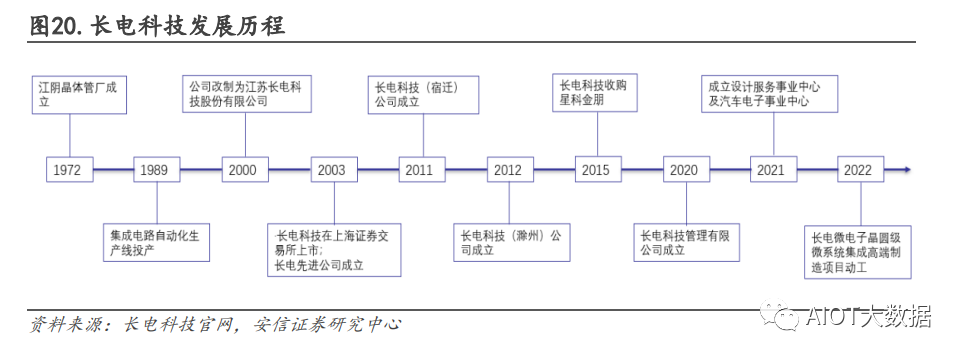

長電科技成立于 1972 年,并于 2003 年在上交所上市,是全球領先的集成電路制造和技術(shù)服 務企業(yè),在中國、韓國和新加坡設有六大生產(chǎn)基地和兩大研發(fā)中心。公司提供全方位的芯片 成品制造一站式服務,包括集成電路的系統(tǒng)集成、設計仿真、技術(shù)開發(fā)、產(chǎn)品認證、晶圓中 測、晶圓級中道封裝測試、系統(tǒng)級封裝測試、芯片成品測試,并可向世界各地的半導體客戶 提供直運服務。公司通過高集成度的晶圓級封裝(WLP)、2.5D/3D 封裝、系統(tǒng)級封裝(SiP)、 高性能倒裝芯片封裝和先進的引線鍵合技術(shù),覆蓋了主流集成電路系統(tǒng)應用,包括網(wǎng)絡通訊、 移動終端、高性能計算、車載電子、大數(shù)據(jù)存儲、人工智能與物聯(lián)網(wǎng)、工業(yè)智造等領域。

從公司的財務數(shù)據(jù)來看,公司營收規(guī)模不斷擴大,歸母凈利潤穩(wěn)定提升。2020-2022 年,公 司營業(yè)收入分別約為 264.64 億元、305.02 億元和 337.62 億元,歸母凈利潤分別為 13.04 億 元、29.59 億元、32.31 億元。公司近幾年加速從消費類轉(zhuǎn)向市場需求快速增長的汽車電子、 5G 通信、高性能計算、存儲等高附加值市場的戰(zhàn)略布局,持續(xù)聚焦高性能封裝技術(shù)高附加值 應用,進一步提升核心競爭力。公司 2022 年實現(xiàn)營業(yè)收入 337.62 億元,同比增長 10.7%; 歸屬于上市公司股東的凈利潤 32.3 億元,同比增長 9.2%;資產(chǎn)負債率同比下降 6 個百分點, 主要系公司于 2022 年在汽車電子,高性能計算等領域完成了多項新技術(shù)開發(fā)及多家全球知 名客戶新產(chǎn)品的量產(chǎn)導入;來自于汽車電子的收入 2022 年同比增長 85%,來自于運算電子的 收入同比增長 46%。 2023 年 Q1 公司實現(xiàn)營業(yè)收入 58.60 億元,同比-27.99%;歸母凈利潤 1.10 億元,較去年同 比-87.24%;扣非歸母凈利潤 0.56 億元,較上年同比-92.80%。公司 Q1 業(yè)績下滑主要系 23Q1 半導體行業(yè)景氣周期繼續(xù)下行,導致國內(nèi)外客戶需求繼續(xù)下降,訂單減少。從盈利能力來看, 由于公司產(chǎn)能利用率大幅下滑,2023Q1盈利能力也有所下滑,毛利率環(huán)比-5.20pct至11.84%, 凈利率環(huán)比-7.69%至 1.88%。23Q1 在下游需求大幅下降的背景下,公司汽車電子業(yè)務仍然保 持高速增長。隨著公司產(chǎn)品結(jié)構(gòu)的優(yōu)化,公司業(yè)績有望復蘇。

公司 2022 年度營業(yè)收入按市場應用領域劃分來看,通訊電子占比 39.3%、消費電子占比 29.3%、 運算電子占比 17.4%、工業(yè)及醫(yī)療電子占比 9.6%、汽車電子占比 4.4%,與去年同期相比消費 電子下降 4.5 個百分點,運算電子增長 4.2 個百分點,汽車電子增長 1.8 個百分點。在測試 領域,公司引入 5G 射頻,車載芯片,高性能計算芯片等更多的測試業(yè)務,相關(guān)收入同比增長 達到 25%。

公司在 Chiplet 領域處于領先地位,目前 XDFOI Chiplet 高密度多維異構(gòu)集成系列工藝已 按計劃進入穩(wěn)定量產(chǎn)階段,同步實現(xiàn)國際客戶 4nm 節(jié)點多芯片系統(tǒng)集成封裝產(chǎn)品出貨,最大 封裝體面積約為 1500mm2的系統(tǒng)級封裝。該技術(shù)是一種面向 Chiplet 的極高密度、多扇出型 封裝高密度異構(gòu)集成解決方案,其利用協(xié)同設計理念實現(xiàn)了芯片成品集成與測試一體化,涵 蓋 2D、2.5D、3D 集成技術(shù)。經(jīng)過持續(xù)研發(fā)與客戶產(chǎn)品驗證,公司 XDFOI不斷取得突破,已 在高性能計算、人工智能、5G、汽車電子等領域應用,為客戶提供了外型更輕薄、數(shù)據(jù)傳輸 速率更快、功率損耗更小的芯片成品制造解決方案,滿足日益增長的終端市場需求。

4.2.通富微電:深度合作 AMD,AI+Chiplet 打開成長空間

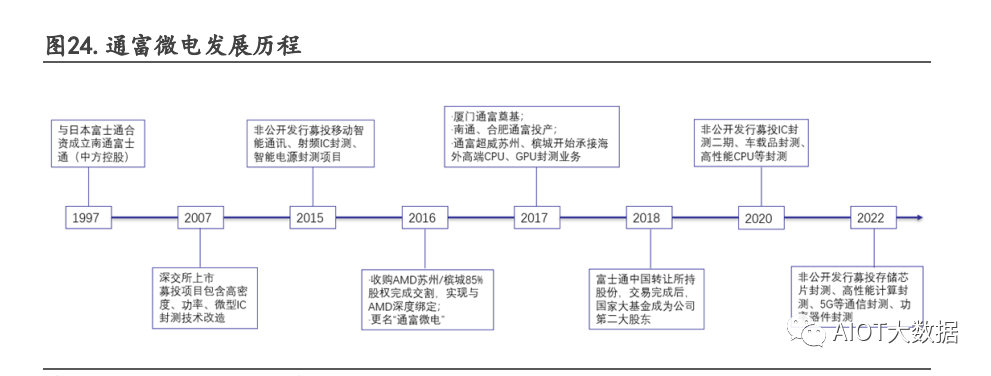

通富微電成立于 1997 年,并于 2007 年在深交所上市,是集成電路封裝測試服務提供商,為 全球客戶提供設計仿真和封裝測試一站式服務。2014 年以來,通富微電相繼在南通、合肥、 廈門等地投資建廠,目前,通富微電相繼投資了崇川總部工廠、南通通富、通富通科、合肥 通富、廈門通富、通富超威蘇州、通富超威檳城七大生產(chǎn)基地,員工總數(shù) 2 萬多人,生產(chǎn)總 面積超過 100 萬平米。2021 年全球 OSAT 中通富微電位列第五,先進封裝方面位列第七。公 司的產(chǎn)品、技術(shù)、服務全方位涵蓋人工智能、高性能計算、大數(shù)據(jù)存儲、顯示驅(qū)動、5G 等網(wǎng) 絡通訊、信息終端、消費終端、物聯(lián)網(wǎng)、汽車電子、工業(yè)控制等領域。

2016 年,通富微電通過并購通富超威蘇州和通富超威檳城,與 AMD 形成了“合資+合作”的 強強聯(lián)合模式,深度鎖定了 AMD 供應鏈并占據(jù) AMD 封測訂單的大部分份額。由于通富超威蘇 州和通富超威檳城前身為 AMD 內(nèi)部封測廠,熟悉 AMD 產(chǎn)品的生產(chǎn)及管理流程,對于 AMD 而言, 通富超威蘇州及通富超威檳城在產(chǎn)品驗證、產(chǎn)品質(zhì)量、新產(chǎn)品開發(fā)時間、業(yè)務對接效率等方 面具有優(yōu)勢。收購以來,通富微電與 AMD 的合作不斷深化,為 AMD 第一大封測產(chǎn)品供應商, 未來隨著大客戶資源整合漸入佳境,產(chǎn)生的協(xié)同效應將帶動整個產(chǎn)業(yè)鏈持續(xù)受益。 從公司的財務數(shù)據(jù)來看,公司業(yè)務發(fā)展迅速,收入規(guī)模不斷擴大,市場份額持續(xù)提升。2020- 2022 年,公司營業(yè)收入分別約為 107.69 億元、158.12 億元和 214.29 億元,歸母凈利潤分 別為 3.38 億元、9.57 億元、5.02 億元。在全球前十大封測企業(yè)中,公司營收增速連續(xù) 3 年 保持第一。公司通過積極調(diào)整產(chǎn)品業(yè)務結(jié)構(gòu),加大市場調(diào)研與開拓力度,憑借 7nm、5nm、FCBGA、 Chiplet 等先進技術(shù)優(yōu)勢,不斷強化與 AMD 等行業(yè)領先企業(yè)的深度合作,鞏固和擴大先進產(chǎn) 品市占率,營收穩(wěn)定提升。公司 2022 年歸母凈利潤有所下滑,主要系集成電路行業(yè)景氣度下 行,部分終端產(chǎn)品需求疲軟,導致公司產(chǎn)能利用率及毛利率下降;同時公司加大 Chiplet 等 先進封裝技術(shù)創(chuàng)新研發(fā)投入,研發(fā)費用增加,導致利潤下降。

2023 年 Q1 公司實現(xiàn)營業(yè)收入 46.42 億元,同比+3.11%;歸母凈利潤 0.05 億元,較去年同比 -97.24%;扣非歸母凈利潤-0.46 億元,較上年同比-131.72%。公司 Q1 業(yè)績有所下滑,主要 系受歐洲地緣政治風險升級、美國持續(xù)高通脹等外部因素影響,集成電路行業(yè)景氣度下降, 終端廠商進去庫周期導致封測行業(yè)訂單出現(xiàn)下滑。從盈利能力來看,2023Q1 盈利能力有所下 滑,毛利率 9.45%,環(huán)比-4.45pct,主要系公司產(chǎn)能利用率下降所致。

Chiplet 技術(shù)方面,公司通過在多芯片組件、集成扇出封裝、2.5D/3D 等先進封裝技術(shù)方面的 提前布局,可為客戶提供多樣化的 Chiplet 封裝解決方案并已量產(chǎn),基于 ChipLast 工藝的 Fan-out 技術(shù),實現(xiàn) 5 層 RDL 超大尺寸封裝(65×65mm),超大多芯片 FCBGAMCM 技術(shù),實現(xiàn) 最高 13 顆芯片集成及 100×100mm 以上超大封裝。目前,公司技術(shù)布局進展順利,已開始大 規(guī)模生產(chǎn) Chiplet 產(chǎn)品,工藝節(jié)點方面 7nm 產(chǎn)品實現(xiàn)量產(chǎn),5nm 產(chǎn)品完成研發(fā)。受益于公司 在封測技術(shù)方面的持續(xù)耕耘,目前公司與 AMD、NXP、TI、英飛凌、ST、聯(lián)發(fā)科、展銳、韋爾 股份、兆易創(chuàng)新、長鑫存儲、長江存儲、集創(chuàng)北方及其他國內(nèi)外各細分領域頭部客戶建立了 良好的合作關(guān)系,2021 年,國內(nèi)客戶業(yè)務規(guī)模增長超 100%。

4.3.華天科技:業(yè)績靜待周期復蘇,Chiplet 布局業(yè)內(nèi)領先

華天科技成立于 2003 年 12 月 25 日,2007 年 11 月 20 日在深交所成功上市。公司主要從事 半導體集成電路、半導體元器件的封裝測試業(yè)務,主要為客戶提供封裝設計、封裝仿真、引 線框封裝、基板封裝、晶圓級封裝、晶圓測試及功能測試、 物流配送等一站式服務。目前公 司集成電路封裝產(chǎn)品主要有 DIP/SDIP、SOT、SOP、SSOP、TSSOP/ETSSOP、QFP/LQFP/TQFP、 QFN/DFN、BGA/LGA、FC、MCM(MCP)、SiP、WLP、TSV、Bumping、MEMS 等多個系列,產(chǎn)品主要 應用于計算機、網(wǎng)絡通訊、消費電子及智能移動終端、物聯(lián)網(wǎng)、工業(yè)自動化控制、汽車電子 等電子整機和智能化領域。2022 年公司持續(xù)加大研發(fā)投入,完成了 3D FO SiP 封裝工藝平 臺、基于 TCB 工藝的 3D Memory 封裝技術(shù)的開發(fā);雙面塑封技術(shù)、激光雷達產(chǎn)品完成工藝驗 證;基于 232 層 3D NAND Flash Wafer DP 工藝的存儲器產(chǎn)品、長寬比達 7.7:1 的側(cè)面指紋、 PAMiD 等產(chǎn)品均已實現(xiàn)量產(chǎn);與客戶合作開發(fā) HBPOP 封裝技術(shù)。

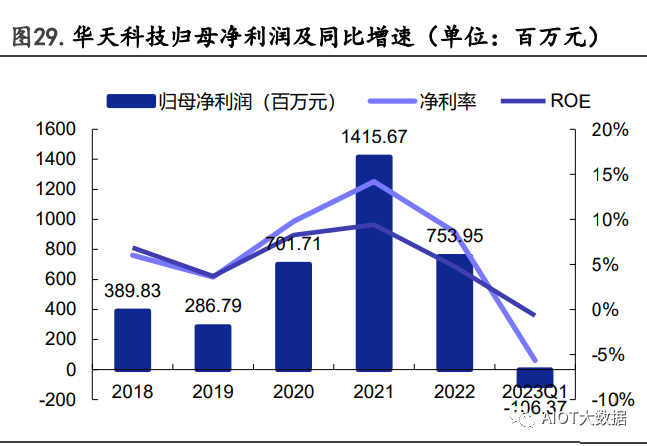

從公司的財務數(shù)據(jù)來看,公司業(yè)務發(fā)展迅速,收入規(guī)模不斷擴大,市場份額持續(xù)提升。 2020- 2022 年,公司營業(yè)收入分別約為 83.82 億元、120.97 億元和 119.06 億元,歸母凈利潤分別 為 7.02 億元、14.16 億元、7.54 億元。公司 2022 年營收與歸母凈利潤同比有所下滑,主要 由于終端市場產(chǎn)品需求下降,集成電路行業(yè)景氣度下滑。從盈利能力來看,公司 2022 年毛利 率 16.84%,同比下降 7.77 個百分點;公司凈利潤率 8.59%,同比下滑 5.62 個百分點。 2023 年 Q1 公司實現(xiàn)營業(yè)收入 22.39 億元,同比-25.56%;歸母凈利潤-1.06 億元,較去年同 比-151.43%;扣非歸母凈利潤-1.82 億元,較上年同比-222.67%。公司 Q1 業(yè)績下滑主要系地 緣政治沖突、經(jīng)濟發(fā)展放緩等因素導致半導體市場終端消費動力不足。從盈利能力來看,由 于公司產(chǎn)能利用率大幅下滑,2023Q1 盈利能力也大幅下滑,毛利率環(huán)比-12.85pct 至 3.99%, 凈利率環(huán)比-14.25%至-5.66%。公司在市場需求減弱、去庫存等不利因素的情況下,積極優(yōu)化客戶結(jié)構(gòu),2022 年公司導入客戶 237 家,通過 6 家國內(nèi)外汽車終端及汽車零部件企業(yè)審核, 引入 42 家汽車電子客戶,涉及 202 個汽車電子項目。同時公司積極推進募集資金投資項目 及韶華科技等新生產(chǎn)基地建設。隨著半導體行業(yè)的復蘇,公司產(chǎn)業(yè)規(guī)模有望進一步擴大。

在 Chiplet 領域,公司實現(xiàn)了 3D FO SiP 封裝工藝平臺的開發(fā),現(xiàn)已具備由 TSV、eSiFo、3D SiP 構(gòu)成的最新先進封裝技術(shù)平臺——3D Matrix。其中晶圓級 eSiFO 主要應用于 Fan-out 封 裝上,其優(yōu)勢包括硅基板,翹曲小、應力低的高可靠性,生產(chǎn)周期短、工藝設備小的低成本、 高集成度、系統(tǒng)級封裝。公司基于 eSiFO 結(jié)合 TSV 技術(shù),開發(fā)了 eSinC 技術(shù)。在 eSiFO 技術(shù) 的基礎上,可以通過 TSV、Bumping 等晶圓級封裝的技術(shù),實現(xiàn) 3D SiP 的封裝,為多芯片的 異質(zhì)異構(gòu)集成提供了可能性。公司目前 Chiplet 技術(shù)已經(jīng)實現(xiàn)量產(chǎn),主要應用于 5G 通信、醫(yī) 療、物聯(lián)網(wǎng)等領域。

4.4.甬矽電子:聚焦先進封裝,Chiplet 前景可期

甬矽電子成立于 2017 年,于 2022 年在上海證券交易所上市。公司主要從事集成電路的封裝 和測試業(yè)務。公司成立之初就聚焦集成電路封測業(yè)務中的先進封裝領域,車間潔凈等級、生 產(chǎn)設備、產(chǎn)線布局、工藝路線、技術(shù)研發(fā)、業(yè)務團隊、客戶導入均以先進封裝業(yè)務為導向, 公司全部產(chǎn)品均為中高端先進封裝形式,封裝產(chǎn)品主要包括“高密度細間距凸點倒裝產(chǎn)品(FC 類產(chǎn)品)、系統(tǒng)級封裝產(chǎn)品(SiP)、扁平無引腳封裝產(chǎn)品(QFN/DFN)、微機電系統(tǒng)傳感器(MEMS)” 4 大類別。公司自 2017 年成立以來,憑借出色的產(chǎn)品質(zhì)量控制和服務能力,在短時間內(nèi)迅速 形成量產(chǎn)并進入恒玄科技、晶晨股份、聯(lián)發(fā)科等頂尖集成電路設計企業(yè)供應鏈,特別在射頻 芯片封測領域具備較強的競爭力。

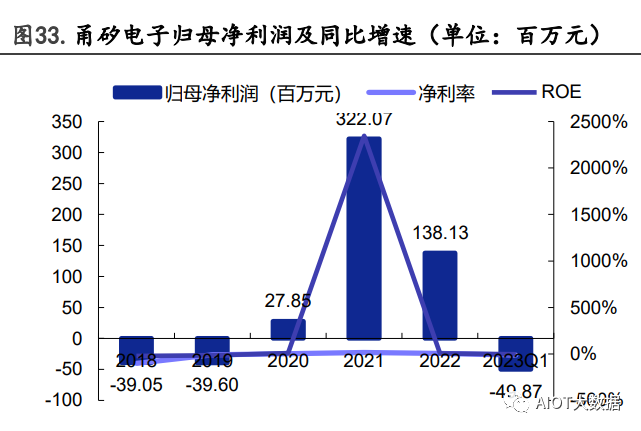

從公司財務數(shù)據(jù)來看,得益于集成電路國產(chǎn)化、智能化以及 5G、新基建等新興應用的驅(qū)動、 下游客戶旺盛的市場需求以及公司市場地位和品牌形象的提升,公司營業(yè)收入、營業(yè)毛利逐 年穩(wěn)定上升。2020-2022 年,公司營業(yè)收入分別約為 7.48 億元、20.55 億元和 21.77 億元, 歸母凈利潤分別為 0.28 億元、3.22 億元、1.38 億元。公司 2022 年營收緩慢增長主要系在 市場需求減弱、行業(yè)整體進入去庫存周期等不利因素的情況下,公司持續(xù)優(yōu)化客戶結(jié)構(gòu),與 多家細分領域頭部客戶建立戰(zhàn)略合作伙伴關(guān)系。公司 2019 年-2021 年,主營業(yè)務毛利率逐年 穩(wěn)步上升,2022 年毛利率有所下降主要系國內(nèi)消費電子等市場需求萎縮,公司部分產(chǎn)品的銷 售單價有所下降,SiP 類產(chǎn)品、QFN 類產(chǎn)品毛利率有所下降。

2023 年 Q1 公司實現(xiàn)營業(yè)收入 4.25 億元,同比-26.86%;歸母凈利潤-0.50 億元,較去年同 比-170.04%;扣非歸母凈利潤-0.69 億元,較上年同比-211.12%。公司 Q1 業(yè)績下滑主要系 2023Q1,終端市場整體延續(xù)了 2022 年下半年的疲軟狀態(tài),下游客戶整體處于庫存調(diào)整狀態(tài), 整體訂單仍較為疲軟。從盈利能力來看,受 1 月份春節(jié)假期、訂單整體下滑等影響,公司整 體產(chǎn)能利用率有所下滑,毛利率環(huán)比-13.52%至 8.39%。此外,公司二期項目有序推進,公司 人員規(guī)模持續(xù)擴大,人員支出及二期籌建費用增加,使得管理費用同比增長 75.06%,23Q1 歸 母凈利潤同比下滑 170.04%。

從公司營收結(jié)構(gòu)來看,2022 年系統(tǒng)級封裝產(chǎn)品(SIP)實現(xiàn)銷售收入 122,524.49 萬元,較上 年同期增長 7.93%,銷售成本同比增長 25.16%,毛利率同比下降 10.45 個百分點。扁平無引 腳封裝產(chǎn)品(QFN/DFN)實現(xiàn)銷售收入 63,184.17 萬元,較上年同期減少 10.10%,銷售成本 同比增加 11.31%,毛利率同比下降 16.92 個百分點。高密度細間距凸點倒裝產(chǎn)品(FC 類產(chǎn) 品)實現(xiàn)銷售收入 29,206.06 萬元,較上年同期增長 58.64%,銷售成本同比增長 66.82%,毛 利率同比下降 3.36 個百分點。微電機系統(tǒng)傳感器(MEMS)實現(xiàn)銷售收入 537.12 萬元,較上 年同期減少 70.54%,銷售成本同比減少 74.56%,毛利率同比上升 13.12 個百分點。

Chiplet 模式能滿足現(xiàn)今高效能運算處理器的需求,而 SiP 等先進封裝技術(shù)是 Chiplet 模式 的重要實現(xiàn)基礎。公司在 SiP 領域具備豐富的技術(shù)積累,通過實施晶圓凸點產(chǎn)業(yè)化項目布局 “扇入型封裝”(Fan-in)、“扇出型封裝”(Fan-out)、2.5D、3D 等晶圓級和系統(tǒng)級封裝應用 領域,并為進一步拓展異構(gòu)封裝領域打下基礎。。同時,公司已經(jīng)掌握了系統(tǒng)級封裝電磁屏蔽 (EMI Shielding)技術(shù)、芯片表面金屬凸點(Bumping)技術(shù),并積極開發(fā) 7 納米以下級別 晶圓倒裝封測工藝、高密度系統(tǒng)級封裝技術(shù)、硅通孔技術(shù)(TSV)等,為 Chiplet 技術(shù)儲備了 充足的技術(shù)基礎。

4.5.芯原股份:發(fā)展先進工藝,以 Chiplet 拓展廣闊市場

芯原股份成立于 2001 年,于 2020 年在上海證券交易所上市。芯原股份是一家依托自主半導 體 IP,為客戶提供平臺化、全方位、一站式芯片定制服務和半導體 IP 授權(quán)服務的企業(yè)。在 芯原獨有的 Silicon Platform as a Service 經(jīng)營模式下,通過基于公司自主半導體 IP 搭建的技術(shù)平臺,可在短時間內(nèi)打造出從定義到測試封裝完成的半導體產(chǎn)品。公司的業(yè)務范圍 覆蓋消費電子、汽車電子、計算機及周邊、工業(yè)、數(shù)據(jù)處理、物聯(lián)網(wǎng)等行業(yè)應用領域。

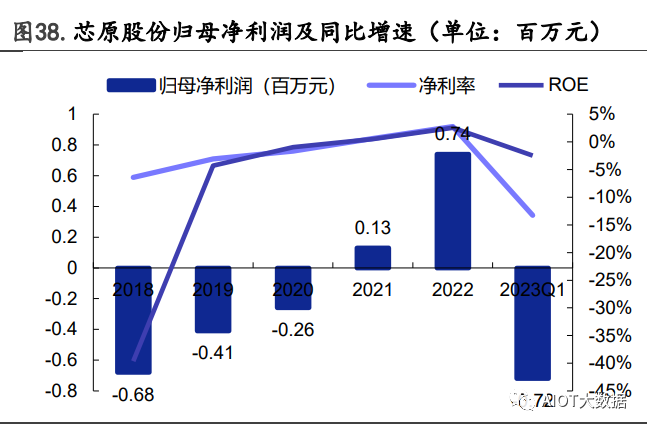

從公司的財務數(shù)據(jù)來看,2022 年度,公司實現(xiàn)營業(yè)收入 26.79 億元,同比增長 25.23%,其中 半導體 IP 授權(quán)業(yè)務(包括知識產(chǎn)權(quán)授權(quán)使用費收入、特許權(quán)使用費收入)實現(xiàn)營收 8.93 億 元,同比增長 26.57%;一站式芯片定制業(yè)務(包括芯片設計業(yè)務收入、量產(chǎn)業(yè)務收入)實現(xiàn) 營收 17.80 億元,同比增長 24.19%。公司 2022 年實現(xiàn)歸母凈利潤 0.74 億元,同比增長 455.31%。公司 2022 年度在半導體產(chǎn)業(yè)下行壓力增大的產(chǎn)業(yè)背景下,實現(xiàn)業(yè)績穩(wěn)定增長,主 要得益于公司獨特商業(yè)模式,即原則上無產(chǎn)品庫存的風險,無應用領域的邊界,以及逆產(chǎn)業(yè) 周期的屬性等。公司 2022 年在手訂單金額 21.50 億元,其中一年內(nèi)(2023 年)轉(zhuǎn)化的在手 訂單金額 16.95 億元,占比 78.82%,在手訂單飽滿。 2023 年 Q1 公司實現(xiàn)營業(yè)收入 5.39 億元,同比-3.77%;歸母凈利潤-0.72 億元,較去年同比 -2280.25%。公司在手訂單充足,截至 2023 年一季度末,公司在手訂單金額為 18.10 億元。 公司 Q1 業(yè)績下滑主要系知識產(chǎn)權(quán)授權(quán)業(yè)務與客戶項目啟動安排相關(guān),單季度收入存在一定 季度性波動。從盈利能力來看,由于公司知識產(chǎn)權(quán)授權(quán)業(yè)務受到客戶項目啟動安排相關(guān)等因 素影響單季度收入有所波動,導致高毛利率的半導體 IP 授權(quán)業(yè)務收入及收入占比下降,毛 利率環(huán)比-9.98%至 38.94%。公司一站式芯片定制業(yè)務毛利率同比有所提升,其中芯片設計業(yè) 務毛利率 5.31%,芯片量產(chǎn)業(yè)務毛利率 26.92%。

Chiplet 可從多維度降低芯片設計及制造成本,公司深耕 Chiplet 技術(shù),大算力時代有望持 續(xù)受益。隨著半導體工藝制程推進,晶體管尺寸越來越逼近物理極限,所耗費的研發(fā)時間及 成本越來越高,Chiplet 技術(shù)通過大幅提高大芯片良率、降低設計復雜度和成本、芯片制造 成本,具有極大的發(fā)展?jié)摿Α9净凇癐P 芯片化,IP as a Chiplet”和“芯片平臺化, Chiplet as a Platform”兩大設計理念,推出了基于 Chiplet 架構(gòu)所設計的高端應用處理 器平臺,目前該平臺 12nm SoC 版本已完成流片和驗證,并正在進行 Chiplet 版本的迭代。 公司持續(xù)推進 Chiplet 技術(shù)產(chǎn)業(yè)化,加入 UCIe 聯(lián)盟,強化在自動駕駛、數(shù)據(jù)中心和平板電腦 領域的布局,有望在大算力時代持續(xù)受益。

4.6.長川科技:國內(nèi)半導體測試設備領先廠商,Chiplet+先進封裝打開發(fā)展機遇

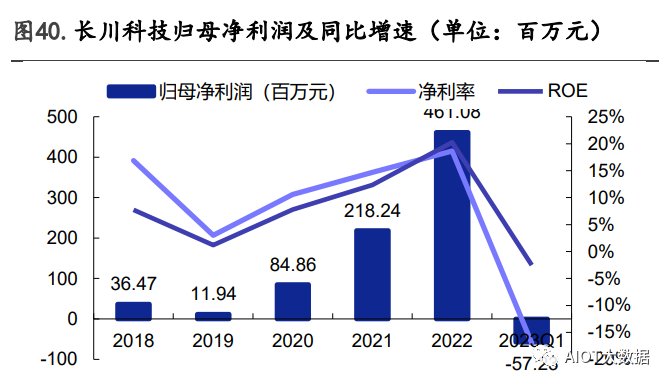

長川科技成立于 2008 年,是國內(nèi)領先的集成電路測試設備及自動化解決方案供應商。公司 目前主營產(chǎn)品包含測試機、分選機和探針臺,全面布局后道測試設備,并通過并購 STI 進入 前道晶圓檢測領域。目前,公司生產(chǎn)的集成電路測試機和分選機產(chǎn)品已獲得長電科技、 華天 科技、通富微電、士蘭微、華潤微電子、日月光等多個一流集成電路企業(yè)的使用和認可。 從公司的財務數(shù)據(jù)來看, 公司近幾年營收以及歸母凈利潤呈現(xiàn)快速提高趨勢,營收從 2018 年的 2.16 億元提高到 2022 年的 25.77 億元,歸母凈利潤從 2018 年的 0.36 億元提高到 2022 年的 4.61 億元。2022 年公司全年營收及歸母凈利潤大幅提高,主要系公司堅持研發(fā)創(chuàng)新, 豐富產(chǎn)品矩陣,穩(wěn)步擴大市場份額。同時公司產(chǎn)品結(jié)構(gòu)優(yōu)化,高端品類收入占比持續(xù)上升, 也推動了業(yè)績的增長。另外,公司于 2022 年通過了發(fā)行股份購買資產(chǎn)收購長奕科技(馬來 西亞 Exis)的審批。EXIS 主要從事集成電路分選設備的研發(fā)、生產(chǎn)和銷售,核心產(chǎn)品主要 為轉(zhuǎn)塔式分選機,有助于長川科技豐富產(chǎn)品類型,實現(xiàn)重力式分選機、平移式分選機、轉(zhuǎn)塔 式分選機的產(chǎn)品全覆蓋。

2023Q1 公司實現(xiàn)收入 3.20 億元,同比-40.48%,環(huán)比-61.12%;實現(xiàn)歸母凈利潤-0.57 億元, 同比-180.50%,環(huán)比-141.91%。公司 Q1 營收同比大幅下滑,主要系封測廠稼動率承壓致使其 資本開支下修,公司訂單下滑導致營收與凈利潤均大幅下滑。公司目前是國內(nèi)數(shù)字測試機領 域龍頭供應商,在數(shù)字測試機領域已完成 D9000K 產(chǎn)品研發(fā),隨著 SoC 測試機在市場持續(xù)放 量,公司與大客戶合作加深,公司業(yè)績有望復蘇。

從收入結(jié)構(gòu)來看,2022 年公司分選機、測試機營業(yè)收入分別為 12.55 億元、11.16 億元,同 比分別+34.04%、+128.18%,毛利率分別為 44.62%、68.96%,同比分別+1.97pct、+1.29pct, 各項業(yè)務營收大幅提高,高毛利率的測試機業(yè)務占比 43.32%,份額逐步提升。

Chiplet 技術(shù)的興起,拉動測試產(chǎn)業(yè)整體需求。在 CP 測試環(huán)節(jié),因為 Chiplet 封裝成本高, 為確保良率、降低成本,需要在封裝前對每一顆芯片裸片進行 CP 測試,相較于 SoC,Chiplet 對芯片的 CP 測試需求按照芯片裸片數(shù)量成倍增加;在 FT 測試環(huán)節(jié),隨著 Chiplet 從 2D 逐 漸發(fā)展到 2.5D、3D,測試的難度提升,簡單測試機減少,復雜測試機增加。經(jīng)過多年持續(xù)技 術(shù)創(chuàng)新,公司測試機和分選機在核心性能指標上已達到國內(nèi)領先、接近國外先進水平。公司 生產(chǎn)的集成電路測試機和分選機等產(chǎn)品已獲得長電科技、華天科技、通富微電、士蘭微、華 潤微電子、日月光等多個一流集成電路廠商的使用和認可。隨著 Chiplet 方案的引入,測試 設備將伴隨下游芯片封測數(shù)量、價值量提升,有望迎來需求快速起量。

4.7.華興源創(chuàng): 半導體檢測設備快速放量,充分受益 Chiplet 技術(shù)發(fā)展

華興源創(chuàng)成立于 2005 年 6 月,于 2019 年成為全國第一家在科創(chuàng)板上市的企業(yè)。公司是國內(nèi) 領先的檢測設備與整線檢測系統(tǒng)解決方案提供商,主要從事平板顯示及集成電路的檢測設備 研發(fā)、生產(chǎn)和銷售。2018 年公司進軍半導體檢測,2020 年公司通過并購歐立通進軍智能穿戴 領域。公司產(chǎn)品主要應用于 LCD 與 OLED 平板顯示及微顯示、半導體、可穿戴設備、新能源 汽車等行業(yè),為客戶提供從整機、系統(tǒng)、模塊、SIP、芯片各個工藝節(jié)點的自動化測試設備。

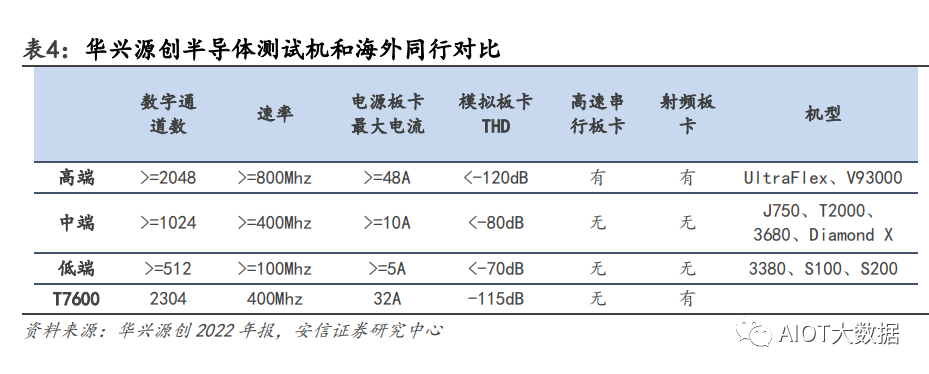

從公司產(chǎn)品結(jié)構(gòu)來看,公司在平板和半導體檢測板塊產(chǎn)品十分豐富,在平板檢測業(yè)務保持業(yè) 內(nèi)領先水平,MiniLED、Micro-LED 及 Micro-OLED 等新一代顯示檢測技術(shù)儲備不斷升級;半 導體檢測業(yè)務包括測試機、分選機、AOI 缺陷檢測設備在內(nèi)的多個標準設備也陸續(xù)進入量產(chǎn)。 消費電子檢測及自動化設備業(yè)務是目前收入主要來源,半導體檢測設備業(yè)務份額有望繼續(xù)提 升。根據(jù)公司公告,2022 年公司消費電子檢測及自動化設備業(yè)務營收 15.08 億元,同比增長0.92%,占總營收 64.98%;半導體檢測設備制造業(yè)務營收 5.66 億元,同比增長 35.55%,占總 營收 24.39%。 在半導體測試機上,公司是全球為數(shù)不多的可以同時自主研發(fā) ATE 架構(gòu) SOC 測試機和 PXIE 架構(gòu)射頻和系統(tǒng)模塊測試機的企業(yè),主打 SOC、射頻測試機以及 SiP 測試解決方案。在 SoC 測試機上,公司自主研發(fā)的 T7600 系列測試機頻率速率達到 400MHZ,部分技術(shù)參數(shù)已經(jīng)達到 行業(yè)內(nèi)公認的中檔 SOC 測試機水平,直接對標泰瑞達的 J750-HD,目前已經(jīng)獲得下游知名 CIS、 MCU 以及指紋識別等芯片客戶訂單。

從公司的財務數(shù)據(jù)來看,公司業(yè)務發(fā)展迅速,收入規(guī)模不斷擴大,市場份額持續(xù)提升。 2020- 2022 年,公司營業(yè)收入分別約為 16.77 億元、20.20 億元和 23.20 億元,歸母凈利潤分別為 2.65 億元、3.14 億元、3.31 億元。公司 2022 年業(yè)績穩(wěn)定增長主要系半導體檢測設備產(chǎn)品的 需求穩(wěn)步擴大,同時公司進一步優(yōu)化了成本結(jié)構(gòu),使成本增長遠低于公司收入增長。從盈利 能力來看,公司 2022 年毛利率 52.08%,同比下降 0.96 個百分點;公司凈利潤率 14.27%,同 比下滑 1.27 個百分點,公司盈利水平總體穩(wěn)定在高位。 2023Q1 公司實現(xiàn)營收 3.59 億元,同比-3.91%;實現(xiàn)歸母凈利潤 0.27 億元,同比增長-34.41%。 公司 Q1 營收同比小幅下滑,主要受制于消費電子行業(yè)景氣下行;凈利潤下滑明顯主要系費 用率提高所致,Q1 期間費用率為 52.03%,同比+4.93%。隨著消費電子景氣度復蘇、Micro OLED 檢測設備放量以及半導體檢測設備出貨量提高,公司業(yè)績有望進一步增長。

Chiplet 技術(shù)代表的先進封裝工藝,是將多顆芯片整合成一個半導體系統(tǒng)的先進封裝技術(shù)。 Chiplet 技術(shù)的廣泛應用,亦帶動了下游廠商對配套測試設備的需求。由于 Chiplet 技術(shù)實 現(xiàn)了芯片的模組化和系統(tǒng)級整合,因此針對系統(tǒng)級芯片的檢測需要滿足覆蓋功能多、差異化 程度高的需求,這也導致了檢測環(huán)節(jié)的耗時增長。華興源創(chuàng)目前推出的基于 PXIE 架構(gòu)的測試機搭配 EP3000 分選機的綜合測試解決方案為歌爾微電子等客戶提供了高效測試解決方案, 可滿足客戶的先進封裝需求。

-

摩爾定律

+關(guān)注

關(guān)注

4文章

636瀏覽量

79111 -

晶體管

+關(guān)注

關(guān)注

77文章

9708瀏覽量

138517 -

AI

+關(guān)注

關(guān)注

87文章

31158瀏覽量

269524 -

chiplet

+關(guān)注

關(guān)注

6文章

434瀏覽量

12608

原文標題:AI助力Chiplet發(fā)展

文章出處:【微信號:AIOT大數(shù)據(jù),微信公眾號:AIOT大數(shù)據(jù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

RISC-V在AI領域的發(fā)展前景怎么樣?

IMEC組建汽車Chiplet聯(lián)盟

2031年全球Chiplet市場預測

AI網(wǎng)絡物理層底座: 大算力芯片先進封裝技術(shù)

人工智能ai4s試讀申請

國產(chǎn)半導體新希望:Chiplet技術(shù)助力“彎道超車”!

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場景提供低成本、高靈活解決方案

西門子EDA創(chuàng)新解決方案確保Chiplet設計的成功應用

AI應用致復雜SoC需求暴漲,2.5D/Chiplet等先進封裝技術(shù)的機遇和挑戰(zhàn)

AI快訊:華為助力金融行業(yè)加速擁抱AI 馬斯克xAI 展示首個多模態(tài)模型

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術(shù)?

荷蘭AI芯片設計公司Axelera計劃推出新型汽車芯粒AI架構(gòu)

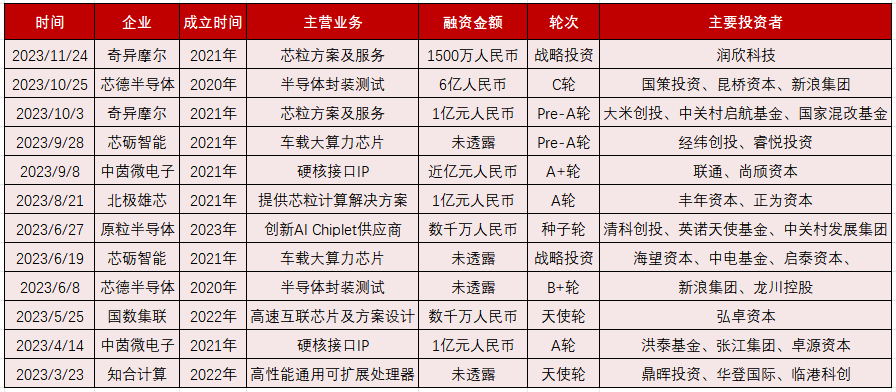

2023年Chiplet發(fā)展進入新階段,半導體封測、IP企業(yè)多次融資

AI助力Chiplet發(fā)展

AI助力Chiplet發(fā)展

評論