有些情況下,constraint不能簡單用一行來表達,而是需要復雜的計算,如果都寫到constraint block內部就比較復雜,而且很亂,這時候可以調用functions來約束隨機變量。在constraint內調用function就稱為”function in constraints”。它的格式如下:

constraint constraint_name { rand_var == function_call(arguments...); }

- function的定義寫在constraint block之外,它內部包含了對arguments的處理。

- 在調用randomize()的時候,function會先被求解,function的返回值將會作為state variables去參與接下來的求解。

不過在使用function in constraints有以下幾點需要注意:

- 在constraint內部調用的function不能包含output或ref類型的arguments,但是const ref是允許的;

- 在constraint內部調用的function應該是automatic類型的;

- 在constraint內部調用的function不能修改constraints,例如調用rand_mode或constraint_mode方法;

- Function會先被求解,也就是它的返回值會被當作state variables。因此,function的arguments和其它rand variables會隱含建立求解order關系(有一點點類似solve…before…),arguments會先求解,解完之后作為傳入function得到返回值作為state variables,最后再求解其它rand variables。另外,如果隱含約束關系會造成求解循環依賴,那么仿真器將會報錯;

順便提一下state variables的概念,它是constraint guards的一種,我們可以把它理解成常數(constants),也就是它的值是固定的了,不會發生變化,不會創建constraint。

接下來看個例子來加深印象。

代碼1如下:

class packet;

rand int length, size, add;

constraint const_c { /*solve length before size;*/ length == calc(size, add); }

constraint const_d { size inside {1, 2, 3, 4, 5, 6, 7, 8}; }

constraint const_e { add inside {1, 0}; }

function int calc(int _s, int _m);

if ( _m )

return ( 100 + 2**_s + _s);

else

return ( 100 - 2**_s - _s);

endfunction: calc

endclass

module top;

initial begin

packet pkt;

pkt = new();

repeat(3) begin

pkt.randomize();

$display("length = %0d, size = %0d, add=%0d",pkt.length, pkt.size, pkt.add);

end

end

endmodule

使用Cadence Xcelium 20.09運行結果如下:

xcelium > run

length = 120, size = 4, add=1

length = -35, size = 7, add=0

length = 80, size = 4, add=0

xmsim: *W,RNQUIE: Simulation is complete.

結果分析:

上面例子在const_c constraint block里使用了函數calc,block給calc傳遞的實參是size和add,因此systemverilog會先求解size和add變量的值,然后再去計算calc的返回結果,這時size, add以及calc()函數的返回值都當作state variables,最終再去求解length變量的值。

但如果將代碼1里第4行的/ solve length before size; /注釋打開,也就是如下代碼2:

class packet;

rand int length, size, add;

constraint const_c { solve length before size; length == calc(size, add); }

constraint const_d { size inside {1, 2, 3, 4, 5, 6, 7, 8}; }

constraint const_e { add inside {1, 0}; }

function int calc(int _s, int _m);

if ( _m )

return ( 100 + 2**_s + _s);

else

return ( 100 - 2**_s - _s);

endfunction: calc

endclass

module top;

initial begin

packet pkt;

pkt = new();

repeat(3) begin

pkt.randomize();

$display("length = %0d, size = %0d, add=%0d",pkt.length, pkt.size, pkt.add);

end

end

endmodule

那么使用Cadence Xcelium 20.09運行結果變成如下所示:

xcelium > run

xmsim: *W,RNDSVB: These solve/before constraints are circular:

0. length - > size

constraint const_c { solve length before size; length == calc(size, add); } (./testbench.sv,4)

1. size - > length

( because of an implicit solve..before for random function-call arguments ): constraint const_c { solve length before size; length == calc(size, add); } (./testbench.sv,4)

pkt.randomize();

|

xmsim: *W,SVRNDF (./testbench.sv,22|18): The randomize method call failed. The unique id of the failed randomize call is 0.

Observed simulation time : 0 FS + 0

結果分析:

這是因為solve length before size與cacl()函數創造的隱含求解order約束沖突了。(Circular dependencies)

-

Verilog語言

+關注

關注

0文章

113瀏覽量

8284 -

求解器

+關注

關注

0文章

77瀏覽量

4539

發布評論請先 登錄

相關推薦

SystemVerilog中的“const”類屬性

[啟芯公開課] SystemVerilog for Verification

SystemVerilog中$cast的應用

SystemVerilog中的package

SystemVerilog中的Semaphores

簡述SystemVerilog的隨機約束方法

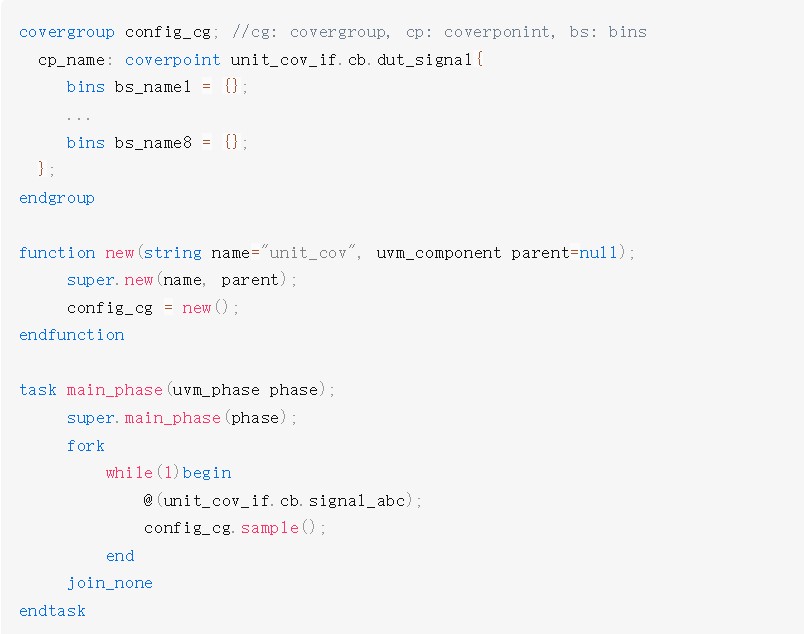

SystemVerilog實用知識點:覆蓋率之Function Coverage

Systemverilog中的Driving Strength講解

聊聊Systemverilog中的function in constraints

聊聊Systemverilog中的function in constraints

評論